荣耀2022数字芯片设计提前批

时间2021.8.03 一个小时

简答题(共40道题,合计80分)

1.[单选题]下列电路中属于时序逻辑电路的是( )

A.编码器

B.计数器

C.数据选择器

D.译码器

解:B

2.[单选题]关于同步设计描述错误的是( )

A.时钟上未叠加任何用户功能逻辑

B.所有寄存器的异步置位及异步复位端口上未叠加任何用户功能逻辑

C.同步设计便于静态时序分析

D.所有寄存器均采用同一时钟

解:D 分频也算啊

3.[单选题]下面哪种措施不能减少亚稳态影响( )

A.用反应更快的FF

B.引入同步机制,防止亚稳态传播

C.改善时钟质量,用边沿变化平缓的时钟信号

D.提高系统时钟

解:CD都不对吧

改善亚稳态的方法:

1.降低系统时钟

2.用反应更快的FF

2.引入同步机制,防止亚稳态传播

3.改善时钟质量,用边沿变化快速的时钟信号

关键是器件使用比较好的工艺和时钟周期的裕量要大。

4.[单选题]状态机没有冗余状态时,可以不写default状态。

A.正确

B.错误

解:B

不写default会有latch

5.[单选题]状态机如果状态未列全,不需要使用default状态。

A.正确

B.错误

解:B 那就更不行了

6.[单选题]#UDLY语句可以被综合成延时电路

正确

错误

解:B 不能综合

7.[单选题]下列关于实现不符合低功耗设计规范要求的是( )

A.在不进行算术、逻辑运算的时候,使这些模块的输入保持“0”,不让操作数进来,输出结果不会翻转;而如果进行这方面的运算时,再将它们打开

B.FPGA全功能版本在产品适用温度范围内,结温不超过阀值的90%

C.接口电平如果可选,选择高电平模式

D.在满足性能要求时,尽量采用低的系统时钟

解:C

8.[单选题]下列说法错误的是( )

A.两个向量进行比较操作或加减操作或赋值操作时,两个向量的位宽要相等,避免隐式扩展;

B.if/else语句配对使用,case语句加default项;组合逻辑中在所有条件下都要对信号赋值,如果要保持不变用a=a的方式赋值;

C.可综合代码中,除了for语句中的循环变量可以定义为integer型外,所有变量和信号都只能为wire或reg型,不能定义为整型、实数型、无符号型、realtime型和time型;

D.条件语句,如果无优先级关系,尽量采用case,避免多级else if影响时序;

解:C

A 对

B 对

C 还可以是三态 tri

9.2 Verilog 可综合性设计 | 菜鸟教程

D if-else与case的区别:

verilog case语句实例_芯片设计小实例——优先级“转移”_weixin_39630466的博客-CSDN博客

9.[单选题]下列说法正确的是( )

A.在always语句中赋值的变量,可以是wire也可以是reg

B.reg变量一定被综合为寄存器

C.always块只能用来描述组合逻辑

D.在assign语句中赋值的变量要定义为wire

解:D

A对

B不 组合逻辑中的always里用的reg不会综合成寄存器

C不是

D对

10.[单选题]我们通常所说的时序逻辑电路是指( )

A.锁存器

B.D触发器

C.RS触发器

D.触发器

解:B

11.[单选题]中断指示寄存器由实时告警的状态触发,是只读寄存器( )

A.正确

B.错误

解:A

12.[单选题]对于信号定义语句:reg[0:4]always,a;,说法错误的是:( )

A.bit定义顺序应该从高到低;

B.信号定义为reg型,只能使用在时序电路的赋值中;

C.每个信号应单独用一行来声明;

D.不能使用关键字定义信号名;

解:AB

A大小端

B always@(*)也能用

13.[单选题]如果两个时钟的频率不同,则两个时钟为异步时钟( )

A.正确

B.错误

解:A

每次遇到这个题都纠结,加入是分频来的呢?

14.[单选题]格雷码(gray code)比二进制码(binary code)有什么优势?

A.编码实现电路更小;

B.实现电路速度更快;

C.更容易判断不同的编码是否相等

D.相邻的两个编码只有一比特发生跳变;

解:D

15.[单选题]用于逻辑的真假判断,结果为单比特,0或1。!用于数据按位取反,结果是单个或多个比特( )

A.正确

B.错误

解:反了 ~多bit !单bit

16.[单选题]以下哪个阶段的仿真可以真实的模拟实际的环境( )

A.综合后仿真

B.布局布线后仿真

C.编译后仿真

D.综合前仿真

解:B

17.[单选题]形式验证可以判断( )

A.两个设计是否等价

B.设计时序是否满足

C.其他均不能保证

D.设计功能是否正确

解:不懂 D

A

7、三种验证技术-形式验证、仿真验证、硬件辅助加速验证

7.1、形式验证

形式验证,采用逻辑和数学公式的方式而不是测试向量来确定硬件的属性。

形式验证优点:①形式验证技术可以是设计实现特性的完备声明,即全部可能输入流;②形式验证技术不需要测试向量输入。

形式验证技术:等价性检查和属性检查。

等价性检查,在所有可能的输入组合和序列下,两个硬件实现的功能是等价的。

属性检查,①属性能够在设计流程的任何阶段被描述出来,包括在系统设计阶段属性的定义、把属性指定到微观结构的设计模块中;②属性描述可在设计规范和开发进行的过程中,不断的搜集和添加;③属性描述可以在设计的开始阶段,当验证环境没有搭建好的时候,为形式属性检查工具提供测试激励;④属性间接地定义了覆盖率统计点,可以用作检查验证过程的完备性。

7.2、仿真验证

仿真验证,通过验证平台应用激励数据到设计中,计算设计下一个状态的值,检查下一个状态是否符合设计期望。

7.3、硬件辅助加速验证

硬件辅助加速验证,把设计映射到可配置平台,如FPGA或者通用单元,以便数字设计部分可以在接近最终产品的时钟速度下运行。硬件加速仿真,使用可配置平台来仿真被测设计,在硬件加速中,验证程序在主机中运行。硬件模拟仿真,激励到设计的数据可以通过实际的接口获取,整个验证环境是真实的,可以通过软件和硬件的检测机制对验证过程进行监测和调试。System Verilog与功能验证(一)_布丁的FPGA之旅的博客-CSDN博客

18.[单选题]哪些情况下不会产生latch电路?( )

A.使用if选择语句的组合逻辑没有e1se部分表达;

B.使用case选择语句的组合逻辑没有else表达

C.时序逻辑中if选择语句,没有else部分表达。

D.组合逻辑中条件不全的case语句没有default赋值;

解:C

19.[单选题]SystemVerilog中,下面那种数组在使用前需要先执行new操作。( )

A.动态数组

B.联合数组

C.多维数组

D.压缩数组

解:不懂

A

定长数组:

动态数组:定义时不指定大小,得先new()再使用,如reg [7:0] ID[]; ID = new(100);

队列:声明时要加$,如int q[$] = {0,1,3};q.delete()——删除掉整个队列

关联数组:

假如一个处理器的寻址范围是几个G,但是处理器只访问几百或几千个字节,这种情况 对几个G的存储空间进行分配和初始化显然是很浪费的

用于保存稀疏矩阵的元素。

仿真器采用树或者哈希表的形式存放关联数组。

便于建立存储模型,不需要在内存中建立非常大的存储。

关联数组的定义,初始化和遍历见绿皮书31页http://blog.sina.com.cn/s/blog_6314c0900102w0wj.html

20.[单选题]下面两端代码中in,q1、q2和q3的初值分别为0,1,2,3,那么经过1个时钟周期后,左侧q3的值和右侧q3的值分别变成了( )

always @(posedge clk)

begin

q1=in;

q2=q1;

q3=q2;

end

always @(posedge clk)

begin

q1<=in;

q2<=q1;

q3<=q2;

end

A.0,0

B.0,2

C.0,3

D.2,0

解:B

21.[单选题]下面那些模块划分方式是不合理的( )

A.将不同优化目标的逻辑分开

B.模块划分根据开发人员的个数进行

C.将存储逻辑独立划分

D.将相关的逻辑或者可以复用的逻辑划分在同一个模块内

解:B

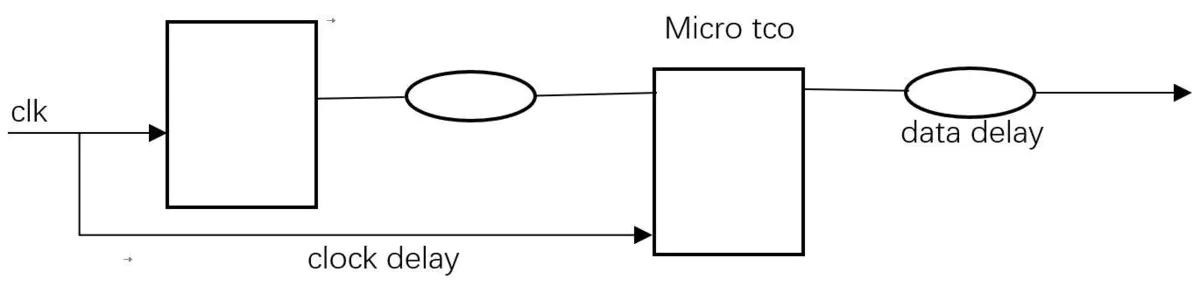

22.[单选题]如下图,对时钟到输出时间分析正确的是( )

A. tCo = Data Delay-clock Delay+Micro Tco

B.tCo = Data Delay+Clock Delay-Micro Tco

C.tCo = Clock Delay-Data Delay+Micro tCo

D.tCo = Data Delay+Clock Delay+Micro Tco

解:D

23.[单选题]关于verilog代码风格,以下说法错误的有:( )

A.每个文件只能定义一个模块

B.Verilog区分大小写,所有信号命名能以大小写来区分不同信号

C.多个reg变量赋值,如果赋值条件完全相同,可以放在同一个always块内

D.每行只能有一个Verilog语句

解:因为是好的风格,所以我选B

24.[单选题]异步电路都不需要STA进行约束检查。

A.正确

B.错误

解:A

25.[单选题]完全消除亚稳态的方法正确的是( )

A.降低时钟频率

B.使用寄存器打拍同步

C.其他均不正确

D.使用异步fifo传递异步信号

解:C 亚稳态只能降低概率不能完全避免

26.[单选题]下列不属于异步时序电路设计特征的是:

A.容易组织流水,提升芯片速率

B.不利于时序分析

C.依赖逻辑时延,时延不好控制

D.容易产生毛刺

解:A 同步才能流水线

27.[单选题]以下哪一项对于提高系统处理能力没有帮助( )

A.减少寄存器翻转率

B.扩大数据位宽

C.缩短处理流水

D.提升系统工作频率

解:A

28.[单选题]同步电路设计中出现setup time不满足、不可以采样下面哪种措施解决( )

A.降低时钟频率

B.pipeline

C.增加时钟频率

D.减小信号延迟

解:C

29.[单选题]单bit电平信号使用级联三触发器电路跨异步时钟城可以消除亚稳态。

A.正确

B.错误

解:B

减低概率

30.[单选题]对于initial语句,说法错误的是:()

A.在模拟的0时刻开始执行;

B.这是一种过程结构语句

C.可用于给实际电路赋初值

D.在仿真过程中只执行一次;

解:C 这是仿真啊

31.[单选题]时序逻辑电路按照其触发器是否有统一的时钟控制分为同步时序电路和异步时序电路。

A.正确

B.错误

解:A

32.异步时钟数据采样的方法错误的是( )

A.使用fifo隔离进行多bit的采样;

B.握手信号后再采样;

C.高频时钟直接采样低频时钟的多bit数据;

D.单bit高频时钟脉冲展宽后给低频时钟进行采样

解:C 这是多bit

33.[单选题]Verilog语言的层次高低对应( )

A.系统级,行为级,功能级,寄存器传输级,门级

B.系统级,行为级,寄存器传输级,功能级,门级

C.系统级,功能级,寄存器传输级,行为级,门级

D.系统级,功能级,行为级,寄存器传输级,门级

解:D

算法级:主要用于快速验证算法的正确性,不一定可以综合成实际电路结构

结构级:更接近电路的实际结构,电路的层次化描述,类似于电路框图

RTL级:贴近实际电路结构的描述,描述的细节到寄存器内容传输级别,可以精确描述电路的工作原理、执行顺序,细化到寄存器级别的结构描述也就是RTL级描述,并无绝对划分标准

开关级:完整描述了电路的细节,最底层的电路描述,可以描述pmos/nmos

34.[单选题]设计异步FIFO时,FIFO深度必须是2的整数次幕,才能使用格雷码

A.正确

B.错误

解:B

35.[单选题]表示任意两位无符号十进制数需要( )位二进制数

A.7

B.8

C.9

D.6

解:A

36.[单选题]模块端口的输入信号,如果没有进行赋值,其值是( )。

A.1

B.C

C.Z

D.0

解:C

37.[单选题]基于Verilog HDL,时钟或复位信号可以出现在赋值表达式中。

A.正确

B.错误

解:A

某年华为IC笔试_Azad_Walden的博客-CSDN博客_以下哪些属于时钟的属性

38.线型信号必须显示定义( )

A.正确

B.错误

解:A

B

Verilog程序模块中输入、输出信号类型默认自动定义为wire型,可以不用显式定义。

39.[单选题]编码中可以使用显式端口映射,也可以使用位置端口映射,位置端口映射方式更好。

A.正确

B.错误

解:B 我感觉显示短裤映射更好,因为可以断开,答案我不知道

端口映射

在元件实例化过程中,有两种方法实现元件端口的映射:位置映射和名称映射。

component inverter is

port ( a: in std_logic;

b: out std_logic

);

end component;

…

U1: inverter port map(x, y);

此处采用的是位置映射法,x对应a,y对应b。

U1: inverter port map(a => x, b=> y);

此处采用的是名称映射法。对于不需要使用的端口可以断开,只需使用关键字open即可,但是输入端口不能指定为空连接。比如:

U2: my_circuit port map(x => a, y => b, w => open, z => b);

40 [单选题]常说的7nm工艺,7nm指的是晶体管的( )

A.漏极宽度

B.栅极宽度

C.整体宽度

D.源极宽度

解:B

最后

以上就是落后小伙最近收集整理的关于荣耀2022数字芯片设计提前批的全部内容,更多相关荣耀2022数字芯片设计提前批内容请搜索靠谱客的其他文章。

发表评论 取消回复