这里设计一个三线八线译码器

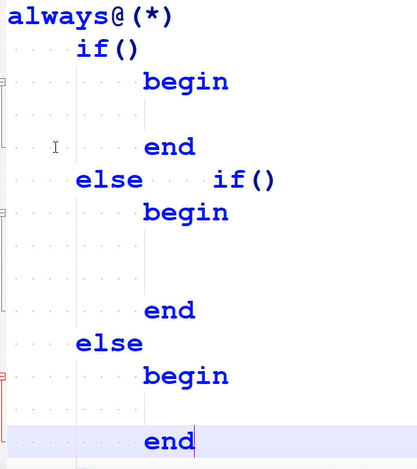

组合逻辑赋值的大体框架:

当只有单条赋值语句时可以省略begin -- end 语句

module my3_8(a,b,c,out);

input a;//输入端口a

input b;//输入端口b

input c;//输入端口c

output reg [7:0]out;//输出端口,[]中表示位宽,且在always模块中赋值的变量一定为reg型

always@(a,b,c)begin//当abc中任意一个发生变化即执行begin中的内容

case({a,b,c})//abc均为单位信号,所以在此时利用{}可将其联系为一个3位的信号

3'b000:out = 8'b0000_0001;//中间的下划线为站位符不代表任何作用

3'b001:out = 8'b0000_0010;

3'b010:out = 8'b0000_0100;

3'b011:out = 8'b0000_1000;

3'b100:out = 8'b0001_0000;

3'b101:out = 8'b0010_0000;

3'b110:out = 8'b0100_0000;

3'b111:out = 8'b1000_0000;

//default:out = 8'b0000_0000;,此为未考虑到的情况,在此可以不用

endcase

end

endmodule case语句比if--else好处在于case不存在先后顺序的关系

仿真文件(textbench)

`timescale 1ns/1ps

module my3_8_tb;

reg a;

reg b;

reg c;

wire [7:0] out;//与之前always模块的定义类型不冲突

my3_8 u1(

.a(a),

.b(b),

.c(c),

.out(out)

);

initial begin //initial上电后只执行一次,begin--end的作用更像是一个括号

a=0; b=0; c=0;

#200;

a=0; b=0; c=1;

#200;

a=0; b=1; c=0;

#200;

a=0; b=1; c=1;

#200;

a=1; b=0; c=0;

#200;

a=1; b=0; c=1;

#200;

a=1; b=1; c=0;

#200;

a=1; b=1; c=1;

#200;

$stop;

end

endmodule

最后

以上就是发嗲酒窝最近收集整理的关于FPGA学习笔记3 -- 多路选择器的全部内容,更多相关FPGA学习笔记3内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复