3.2、时序逻辑电路

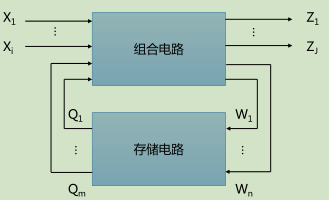

时序逻辑电路如图所示

Zi = f(X1,X2,...,Q1,Q2,...)(I = 1,2,...) Wi = g(X1,X2,...,Q1,Q2,...)(I = 1,2,...) Qi(n+1) = h(X1,X2,...,Q1(n),Q2(n),...)(I = 1,2,...)

输出方程Z和驱动方程W是用来描述组合逻辑关系的,状态方程Q是用来描述存储电路的新状态Qn+1与原状态Qn和驱动信号W之间的关系。由图可知,一个完整的时序电路是由组合逻辑电路和存储电路组成,它在任何时刻的输出,不仅与该时刻的输入信号有关,而且还与该时刻以前的输入信号有关。

常用的存储电路有两类,一类是锁存器,另一类是触发器。

3.2.1、锁存器(Latch)

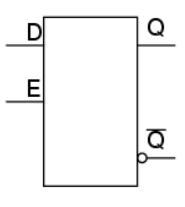

锁存器是数字电路中的一种具有记忆功能的逻辑元件,采用电平触发方式的存储单元。状态的改变取决于输入脉冲信号的电平值,当输入脉冲为高电平(或低电平)时输出数据才会发生变化。锁存器的接口有四个,如图所示:

3.2.1.1、RS锁存器

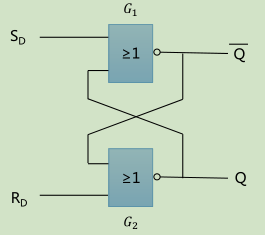

RS锁存器:RS锁存器是构成所有复杂的锁存器和复杂触发器的基础,如图所示:

R和S分别代表RESET和SET,D表示DATA,两个输出逻辑值互补,若Q = 0,则称锁存器为0状态,若Q = 1,则称锁存器为1状态。。

RS锁存器置位:即SD = 1,RD = 0,则Q非 = 0,Q = 1,锁存器状态为1.

RS锁存器复位:即SD = 0,RD = 1,则Q非 = 1,Q = 0,锁存器状态为0.

RS锁存器要禁止SD和RD同时为1的情况出现,否则会出现错乱状态。因为如果SD和RD突然全为0,而连个变0有先后,而不同的先后顺序会产生不同的结果。

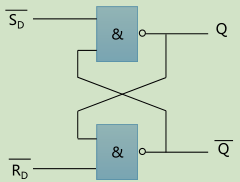

也可以用与非门构成RS锁存器的电路图:

时序电路的四种描述方法:特性表、特性方程、状态图、波形图

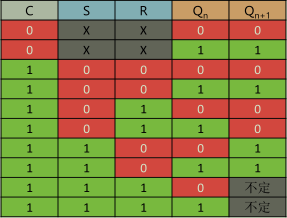

特性表:特性表就是反应输入变量的原始状态以及新状态之间关系的一种真值表,也被称为状态转换真值表。原状态用Qn表示,新状态用Qn+1表示,RS锁存器的特性表如图所示:

根据特性表可以看出RS锁存器的逻辑功能,:SD和RD都为0时,新状态和原状态保持不变;当RD为1时,新状态都变为0;当SD为1时,新状态都变为1;当SD和RD都为1时,新状态不确定。

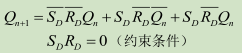

特性方程:特性方程就是新状态的逻辑函数表达式,RS锁存器的特性方程由上面的真值表可得:

利用约束条件将上式化简为:

![]()

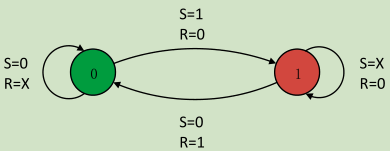

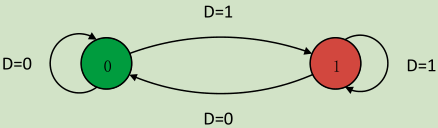

状态图:状态图是表示器件的状态的转换过程,RS锁存器的状态图如图所示:

箭头的末端是原状态,前端是新状态,X表示任意状态。由状态图看出RS锁存器的状态是如何变化的。

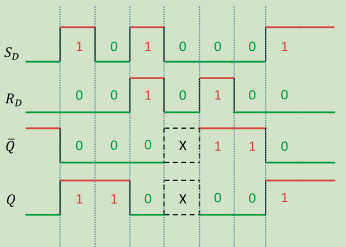

波形图:波形图是表示输入和输出的波形。RS锁存器的波形图如图所式:

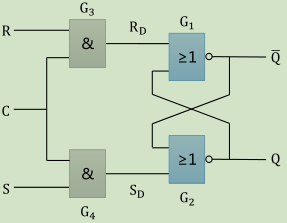

3.2.1.2、门控RS锁存器

门控RS锁存器是在原来的RS锁存器的基础上添加了一个控制端,只有控制端的信号变为有效电平后,RS锁存器才能按照输入的置1或者置0信号改变相应的状态。结构图如图所示:

添加了一个控制信号C,RD = RC,SD = SC,根据电路图写出门控RS锁存器的特性表如图所示:

当C = 0时,无论S和R的值是什么,状态维持不变。

3.2.1.3、D锁存器

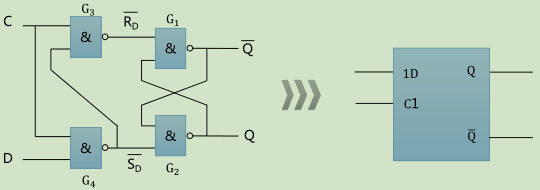

D锁存器:能够将输入端的单路数据D存入到锁存器中的电路,为了解决RS锁存器不能同时为1带来的问题。D锁存器的电路图和逻辑符号如图所示:

根据电路图写出特性表如图所示:

从特性表看出,D = 0,新状态就变为0,D = 1,新状态就变为1。而当C = 0 时,无论D是什么,输出端的将维持之前的状态,此时就表示将数据锁存起来了。特性方程为Qn+1 = D。状态图如图所示:

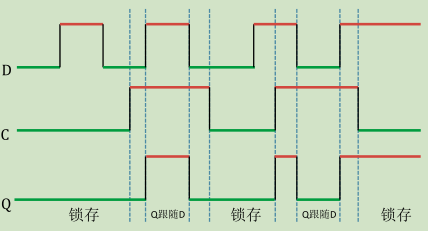

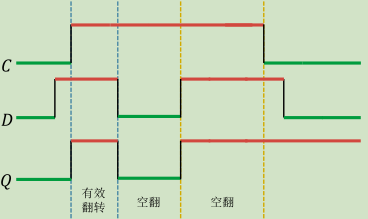

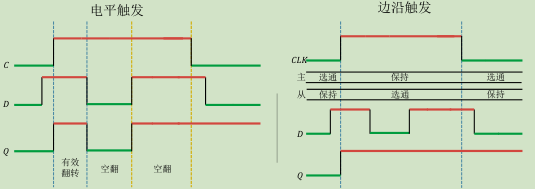

波形图如图所示:

由图可知,D是锁存器的输入信号,C是锁存器的控制信号,Q是锁存器的输出信号,当C = 1时,Q随着D的变化而变化;当C = 0时,Q会被锁存而不再变化。

3.2.1.4、空翻现象

空翻:锁存器中存在空翻现象,当控制信号有效时,输入信号若发生多次变化,输出状态也跟着发生多次变化,这一现象就被称为锁存器的空翻。空翻波形示意图如图所示:

后面的两次翻转被称为空翻,空翻是一种有害的现象,它使得时序电路不能按时钟节拍工作,造成系统的误动作,锁存器都存在空翻现象。

3.2.1.5、锁存器的特点及产生情况

锁存器的特点:

1、Latch由电平触发,非同步控制。在使能信号有效时Latch相当于通路,在使能信号无效时Latch保持输出状态。

2、Latch对输入电平敏感,受布线影响大,很难保证没有毛刺产生。

3、Latch将静态时序分析变得极为复杂

在绝大多数设计中应该避免产生Latch。

在组合逻辑电路中,如果条件描述不全容易产生Latch:

1、if语句中缺少else。

2、case语句中没有给出全部的情况。

3.2.2、触发器(Flip-flop)

触发器是对脉冲边沿敏感的存储单元电路,它只在触发脉冲的上升沿(或下降沿)瞬间改变其状态。

3.2.2.1、D触发器(D Flip-flop)

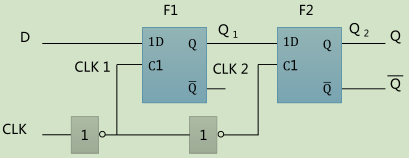

FPGA设计中使用更多的是D触发器(D-type flip-flops)—— DFF,DFF由两个相同的D锁存器以及两个非门连接而成,DFF的电路图如下图所示:

F1为主锁存器,F2为从锁存器,两个锁存器的控制信号都由外部时钟信号CLK提供。当CLK = 0时,F1为通路,此时Q1随着D的变化而变化;当D = 1时,F1数据被锁存,Q1已经不再变化,F2被选通,Q2 = Q1,所以触发器在一个时钟周期里最后输出状态只改变一次,克服了空翻现象。

D锁存器和D触发器的波形对比图如图所示:

当CLK = 0时将D的最后变化的数据锁存起来,当CLK = 1时将锁存的数据送出到输出端,所以D触发器就是在CLK的上升沿进行触发的,通常将这种触发方式称为边沿触发,这种边沿触发方式的D触发器称为边沿D触发器。

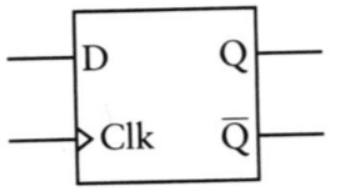

D触发器的电路符号和D锁存器的区别是CLK处的小三角,表示触发方式是边沿触发,如图所示:

D触发器的verilog代码如图所示:

//---------------------------------------------------------------------------

//-- 文件名 : Digital_Data_Flip_Flop.v

//-- 作者 : ZIRCON

//-- 描述 : D触发器模块

//-- 修订历史 : 2017-1-1

//---------------------------------------------------------------------------

module Digital_Data_Flip_Flop

(

/* 时钟和复位端口 */

CLK_50M,RST_N,

/* 输入端口 */

D,

/* 输出端口 */

Q

);

//---------------------------------------------------------------------------

//-- 外部端口声明

//---------------------------------------------------------------------------

input CLK_50M; //时钟端口

input RST_N; //复位端口

input D; //输入端口

output Q; //输出端口

//---------------------------------------------------------------------------

//-- 内部端口声明

//---------------------------------------------------------------------------

reg Q; //输出端口

//---------------------------------------------------------------------------

//-- 逻辑功能实现

//---------------------------------------------------------------------------

/* 时序电路,给Q寄存器赋值 */

always @ (posedge CLK_50M or negedge RST_N)

begin

if(!RST_N)

Q <= 1'b0;

else

Q <= D;

end

endmodule

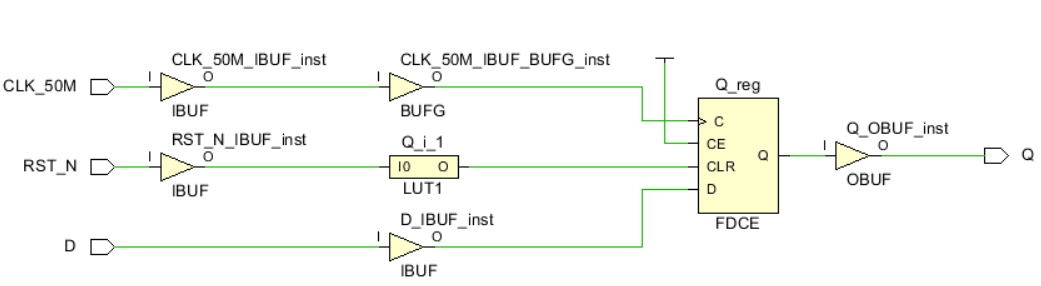

综合出来的原理图如图所示:

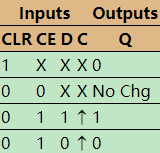

FDCE是同步使能,异步复位的D触发器。FDCE is a single D-type flip-flop with clock enable and asynchronous clear. When clock enable (CE) is High and asynchronous clear (CLR) is Low, the data on the data input (D) of FDCE is transferred to the corresponding data output (Q) during the Low-to-High clock (C) transition. When CLR is High, it overrides all other inputs and resets the data output (Q) Low. When CE is Low, clock transitions are ignored. 真值表如图所示:

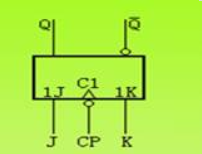

3.2.2.2、JK触发器(JK Flip-flop)

在时钟脉冲操作下,根据J、K取值的不同,凡是具有保持、置1、置0、翻转功能的电路,都称为JK型时钟触发器,简称JK触发器。逻辑符号如图所示:

特性方程为:

![]()

特性表如图表所示:

| J | K | Qn | Qn+1 | 功能 |

| 0 | 0 | 0 | 0 | 保持 |

| 0 | 0 | 1 | 1 | |

| 0 | 1 | 0 | 0 | 置0 |

| 0 | 1 | 1 | 0 | |

| 1 | 0 | 0 | 1 | 置1 |

| 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 1 | 翻转 |

| 1 | 1 | 1 | 0 |

3.2.2.3、T触发器(T Flip-flop)

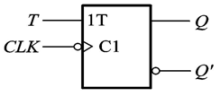

在时钟脉冲下,根据输入信号T取值的不同,凡是具有保持和翻转功能的电路,即当T = 0时能保持状态不变,T = 1时一定能翻转的电路,称为T触发器,逻辑符号如下图所示:

特性方程如图所示:

![]()

特性表如下表所示:

| T | Qn | Qn+1 | 功能 |

| 0 | 0 | 0 | 保持 |

| 0 | 1 | 1 | |

| 1 | 0 | 1 | 翻转 |

| 1 | 1 | 0 |

3.2.2、寄存器

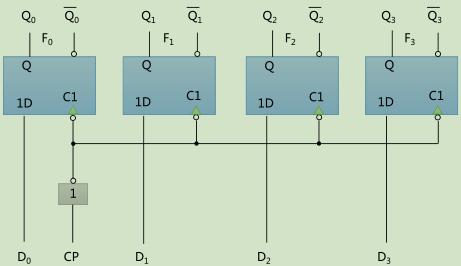

寄存器是能够存储多位二进制数的时序电路,寄存器是由多个触发器组成的。由四位D触发器组成的寄存器如图所示:

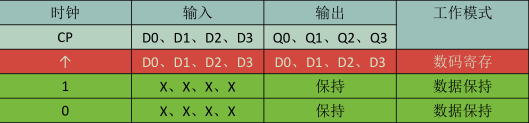

当给CP端一个脉冲,此时D0、D1、D2、D3的值就被存储在寄存器里了,知道CP端的下一个脉冲的上升沿到来时,存储的值才会改变。由四位D触发器组成的寄存器特性表如图所示:

这种寄存器的工作状态只有寄存和保持两种。

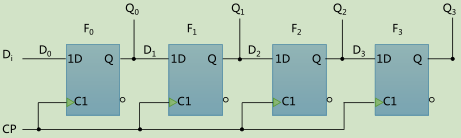

移位寄存器:分为单向移位寄存器和双向移位寄存器,单向分为左移位寄存器和右移位寄存器,双向移位寄存器既能左移也能右移。

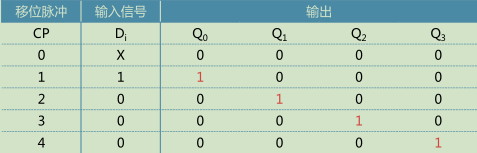

右移位寄存器由四个D触发器连接起来的如图所示:

特性表如图所示:

移位寄存器代码如图所示:

//---------------------------------------------------------------------------

//-- 文件名 : Digital_Shift_Reg.v

//-- 作者 : ZIRCON

//-- 描述 : 移位寄存器模块

//-- 修订历史 : 2017-1-1

//---------------------------------------------------------------------------

module Digital_Shift_Reg

(

/* 时钟和复位端口 */

CLK_50M,RST_N,

/* 输入端口 */

DATA_EN,DATA_IN,

/* 输出端口 */

DATA_OUT

);

//---------------------------------------------------------------------------

//-- 外部端口声明

//---------------------------------------------------------------------------

input CLK_50M; //时钟端口

input RST_N; //复位端口

input DATA_EN; //输入端口

input DATA_IN; //输入端口

output DATA_OUT; //输出端口

//---------------------------------------------------------------------------

//-- 内部端口声明

//---------------------------------------------------------------------------

reg [3:0] DATA_OUT; //输出端口

reg [3:0] DATA_OUT_N; //DATA_OUT的下一个状态

//---------------------------------------------------------------------------

//-- 逻辑功能实现

//---------------------------------------------------------------------------

/* 时序电路,给DATA_OUT寄存器赋值 */

always @ (posedge CLK_50M or negedge RST_N)

begin

if(!RST_N)

DATA_OUT <= 4'b0;

else

DATA_OUT <= DATA_OUT_N;

end

/* 组合电路,实现移位寄存器 */

always @ (*)

begin

if(DATA_EN)

DATA_OUT_N = {DATA_OUT[2:0] , DATA_IN};

else

DATA_OUT_N = DATA_OUT;

end

endmodule

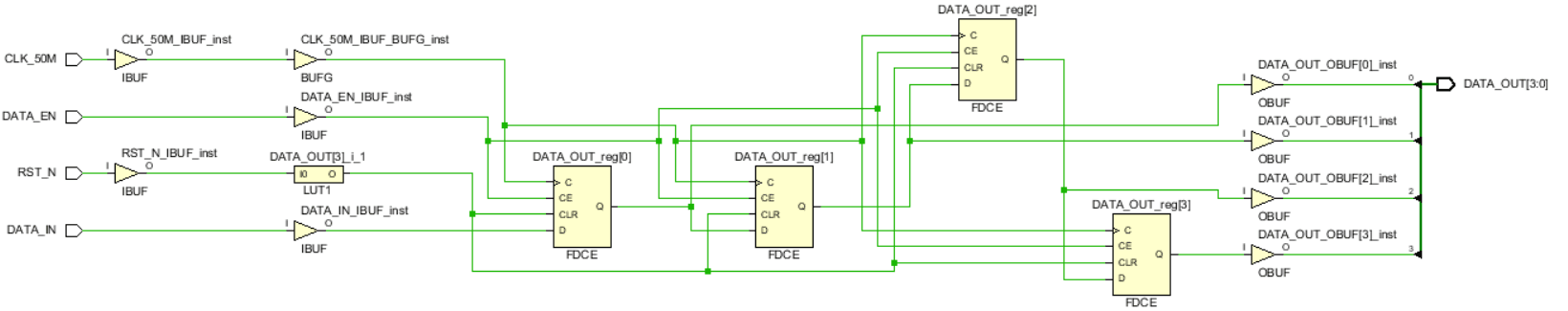

综合原理图如图所示:

参考:锆石教程

最后

以上就是饱满小蝴蝶最近收集整理的关于数字电路篇四的全部内容,更多相关数字电路篇四内容请搜索靠谱客的其他文章。

发表评论 取消回复