汇总了华为海思、乐鑫科技等多家的笔试题中有关Verilog语法部分的题目,涉及位拼接、阻塞赋值与非阻塞赋值、Latch锁存器、量化、运算位扩展、可综合与不可综合、三目运算符(?:)等。

目录

1. 位拼接

2. Latch锁存器

3. 存储器声明

4. ==和===

5. ?:条件运算符(三目运算符)

6. 乘加运算位宽扩展

7. 变量名称定义

8. 数据定义与量化

9. 阻塞赋值与非阻塞赋值

10. 地址编码问题

11. Verilog关键字

12. Verilog可综合与不可综合语句

13. Verilog标识符

1. 位拼接

已知【a=1'b1; b=3'b001;】,那么{a,b}=?

A. 3'b001

B. 3'b101

C. 4'b0011

D. 4'b1001

答案:D

解析:

{}为位拼接运算符,顾名思义:把信号按位拼接起来,左边的在高位。

{}还可以用于复制,比如{3{a}} = 3’b111,等效于{a, a, a}是3个拼接;

2. Latch锁存器

描述组合逻辑时,当if语句不需要有else分支时,不写else分支,可以节省面积。

A. 正确

B. 错误

答案:B

解析:

组合逻辑中,if...else完整可能是综合出选择器;if如果不写else,默认进行保持,此时会综合出【锁存器】,比选择器占用更多的面积。

锁存器的缺点:不利于时序分析,需要更多资源。

3. 存储器声明

reg [255:0] mem [31:0]; 该声明定义了一个位宽32 bit、深度256的memory。

A. 正确

B. 错误

答案:B

解析:

reg [7:0] addr; 表示 8 bit位宽的信号addr;

reg [255:0] mem [31:0]; 表示256位宽、32深度的存储器mem,前面的表示位宽,后面的是深度;

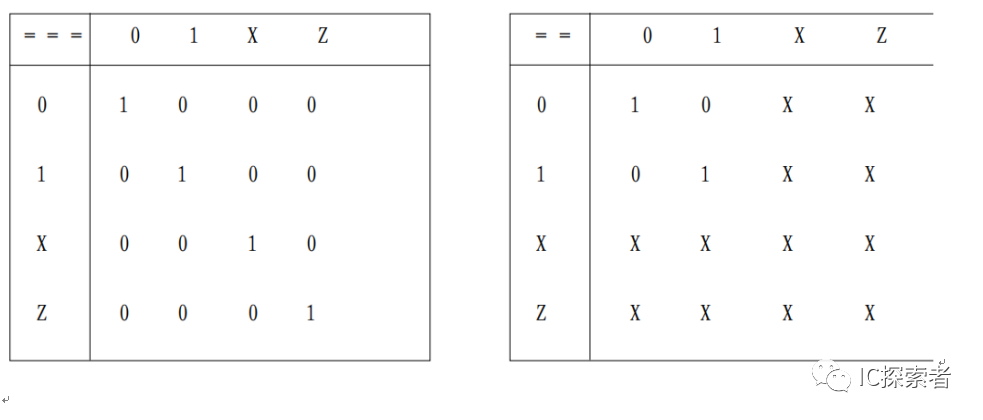

4. ==和===

如果A和B是两个3bit的变量:A=3'b1X0,B=3'b1X0,那么【A == B】和【A === B】的结果分别是?

A. 1,0

B. x,1

C. 0,x

D. 0,1

答案:B

解析:

==,判断相等,但是只能比较0、1,一旦出现X和Z结果就为X;

===,范围更大的判断,能判断0、1、X、Z。

5. ?:条件运算符(三目运算符)

现有表达式expr = cond_expr ? expr1 : expr2,如果cond_expr为X或者Z,expr1=1001,expr2=1010,则expr应为()

A. 1010

B. 10XX

C. 1001

D. 101X

答案:

解析:

三目运算符?:,expr = cond_expr ? expr1 : expr2

等效于

if(cond_expr == 1’b1)

expr = expr1;

else

expr = expr2;

这里当cond_expr为X或者Z时,不满足if(cond_expr == 1’b1),所以执行else,结果是expr = expr2 = 4’b1010。

6. 乘加运算位宽扩展

假设输入信号X位宽为10 bit,InputA位宽为5 bit,InputB位宽为14 bit,实现Y = X*InputA + InputB功能,并要求不损失精度,那么输出信号Y位宽应不小于()

A. 16 bit

B. 29 bit

C. 15 bit

D. 24 bit

答案:A

解析:

M bit + N bit的和,位宽为max(M, N) + 1 bit时才能保证结果不溢出且不损失精度,其中max(M, N)表示取M和N中的最大值;

M bit * N bit的积,位宽为M+N bit时才能保证结果不溢出且不损失精度;

因此,X*InputA要用15 bit,Y要用16 bit。

7. 变量名称定义

编写Verilog HDL程序时,变量的定义不可以与关键词冲突。

A. 正确

B. 错误

答案:A

解析:

变量命名规则:

(1)不能与关键词冲突;

(2)不能以数字开头;

8. 数据定义与量化

表示任意两位无符号十进制数需要()位二进制数

A. 7

B. 8

C. 6

D. 5

答案:A

解析:

最大的两位十进制:99,无符号表示时在0~127范围内,7 bit表示即可。

0000000~1111111:0~127。

如果是有符号数表示的99呢?

要多添加1 bit的符号位,8 bit表示范围:-128 ~ 127

9. 阻塞赋值与非阻塞赋值

下面两段代码中in、q1、q2和q3的初值分别为0、1、2、3,那么经历1个时钟周期后,左侧q3的值和右侧q3的值分别变成了()

always @(posedge clk) beginq1 = in;q2 = q1;q3 = q2;end

always @(posedge clk) beginq1 <= in;q2 <= q1;q3 <= q2;end

A. 0,0

B. 0,3

C. 2,0

D. 0,2

答案:D

解析:

=阻塞赋值,<=非阻塞赋值;

阻塞赋值:当前语句的赋值会阻塞后面赋值,后面的必须等当前语句赋值完成后再执行,所以先执行q1 = in = 0,此时q1已经变为0;再执行q2 = q1 = 0,q2也变为了0;最后q3 = q2 = 0,q3也变为0,和C语言的赋值类似,顺序执行;

非阻塞赋值:当前语句的赋值不会阻塞下面语句的赋值,当在begin...end块中时,块内的<=语句在块结束时一起更新赋值,所以更新时完成的是q1 = 0,,q2 = 1,q3 = 2;

10. 地址编码问题

十六路数据选择器的地址输入端至少需要几根线()

A. 2

B. 4

C. 16

D. 8

答案:B

解析:

2^4 = 16。

4根地址线,实现4-16译码器。(3根地址线,3-8译码器)

11. Verilog关键字

下面()不是Verilog循环关键字

A. forever

B. repeat

C. while

D. force

答案:D

解析:

ABC都是循环用的,D是强制赋值用的。

12. Verilog可综合与不可综合语句

可综合的verilog语法包括()

A. assign

B. for

C. always

D. wait

E. time

F. initial

G. generate

答案:ABCG

解析:

A. assign赋值可综合;

B. for循环可综合;

C. always 可综合;

D. wait等待,不可综合,一般用于Testbench中调试;

E. time时间类型的变量,不可综合;

F. initial赋初值,不可综合,一般Testbench中赋初值;

G. generate可综合,generate for时必须把循环变量定义为genvar类型,for后面的begin必须用冒号:后起名字;

13. Verilog标识符

在verilog中,下面哪个标识符是非法的

A. IsErr

B. ERR

C. 0_is_err

D. Error

答案:C

解析:

不能以数字开头,不能与关键字冲突。

最后

以上就是土豪夕阳最近收集整理的关于笔试 | FPGA和数字IC刷题——Verilog语法类笔试题合集(1)的全部内容,更多相关笔试内容请搜索靠谱客的其他文章。

发表评论 取消回复