一、测试点分解的意义

测试点分解是制定验证计划中极其重要的和极具含金量的基础性步骤,充分体现验证人员经验、能力、价值的一项工作,要求完备细致。

二、测试点分解的依据

1.DUT的spec

2.标准、协议

3.其他文档(产品需求、架构文档、算法说明、产品说明书、应用手册等

4.通用基本逻辑单元的常规测试点

5.来自设计工程师的要求(是否有特殊的、对某些极端的电路测试要求)

6.来自验证工程师的经验

三、测试点分解的原则

1.测点完全。若资源允许,DUT的全部功能都应当被测试。

2.描述精准。测试点的描述应当清晰、准确。

3.精细适度。测试点既要覆盖全面,又要避免过度验证。

4.有先有后。资源有限的情况下,把握优先级。

5.过程持续。测试点分解并非一蹴而就,需要反复迭代更新。

四、测试点分解的步骤

1.阅读、学习必要的各种文档,逐步简明列写测试点

(1)阅读文档:spec->标准、协议->其他文档

(2)模块级:文字描述->寄存器描述->端口信号->通用逻辑单元->时钟复位及特殊逻辑

(3)芯片级:互联,”系统中验模块“,模块功能,芯片功能,芯片级特有功能

2.与设计工程师积极交流,辅之以验证工程师经验,对测点查漏补缺

3.合并、细化测试点,检查最终结果是否符合测试点分解的原则

五、测试点分解的思路与方法

1.主要思路

(1)功能(包含性能):单独、组合

(2)时序:端口、内部

(3)异常

2.常用方法

(1)等价类划分

输入值的子集,分为有效等价类和无效等价类,如输入值是正整数且小于16,则有效等价类为0<x<=15,小于0和大于16为无效等价类

(2)边界值分析

把输入值的边界值作为测试点,则可划分为正常区域,正常边界区域,异常边界区域,异常区域,如输入值是正整数且小于16,则正常边界区域为1和15,异常边界区域为0和16.

(3)随机

对输入的值进行随机化,一般和等价类法联合使用,在等价区域使用随机化的值。

(4)因果判决表

如输入a和b得到结果x,输入c和d得到结果y,列出所有的关系,在对不能同时的输入简化,做出测试点。

(5)流程图

根据不同的条件执行不同的处理,画出流程图,确认测试路径,一般用在定向测试中,有明确的的输入输出关系。

(6)应用场景分析

根据用户的使用场景进行测试点分解。

(7)错误推测

根据经验和对DUT的理解,假设DUT在特定激励下会发生异常或错误,有目的构建一些测试用例去捕捉这类错误或确定错误不存在。

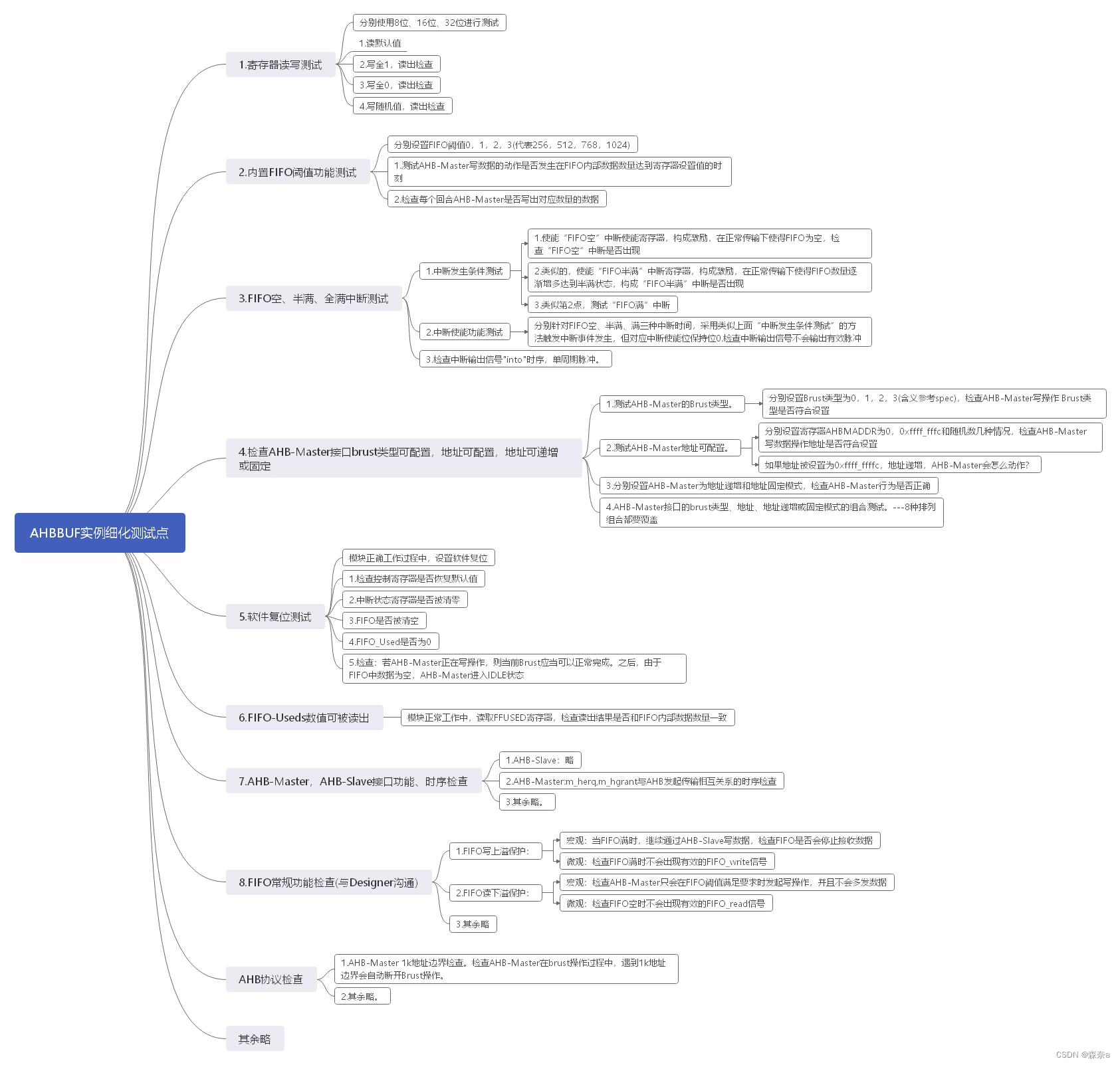

六、模块级测试点分解实例AHBBUF

1.阅读文档-列写测试点

(1)spec

a.文字描述的功能

总功能:收发数据、存数据

功能1:AHB-Slave接口的寄存器访问

功能2:FIFO阈值可配置

功能3:FIFO空、满、半满中断,包括中断端口into

功能4:发数据Brust类型可配置,输出地址可配置,地址可递增或固定

b.寄存器描述的功能

功能5:软件复位功能测试

功能6:内置FIFO数据个数可被读出

spec中每个寄存器认真分析,提取验证点。

c.端口信号

功能7:AHB-Master,AHB-Slave接口功能检查

d.通用逻辑单元

“内置FIFO宽度8-bit,深度1024”:

功能8-x: FIFO常规检查:深度、位宽、空满判断

功能8-x: FIFO异常检查:FIFO满后写,空后读;FIFO清空检查。软件复位可以清空FIFO?

e.时钟复位及特殊逻辑

考虑有无特殊时钟设计:多时钟;跨时钟域设计

是否有复位设计:复位是否清空FIFO

验证人员必须关注DUT的多时钟、跨时钟、时钟切换、变频等任何与时钟复位相关的电路设计,或其他特殊电路。

(2)标准、协议

查看文档中明确描述的各种信号变化规则,逻辑事件的前因后果关系、数据传输处理与倍率等各要求。

功能x+1:AHBx协议内容检查;AHB-Slave和AHB-Master接口信号必须符合AMBA-AHB Rev2.0('m_hreq’和‘m-hgrant’信号时序逻辑关系;’haddr’在brust传输中的变化规则;任何brusts操作不能穿越1kb地址边界!…)

(3)其他文档

2.与设计工程师交流,辅之以验证工程师经验,查缺补漏

答疑解惑;了解模块设计者是否有明确的要求对设计中某一部分功能·、子模块进行一些特殊的检查;考虑该模块在异常激励,异常时钟,异常复位,异常配置下的行为;根据经验对高风险部分特别关注,单独列写测试点。

AHBBUF:'into’输出端口的信号功能时序是如何的;FIFO在满后写,空后读?;AHB-MAster在一个Brust传输未完成时,电路被复位,后续如何处理…

3.合并、细化测试点,检查最终结果是否符合测试点分解的原则

简明列写测试点步骤完成后,合并多角度相同测试点,得到清晰准确的测试点集合。

七、芯片级或子系统级测试点分解实例AHBBUF

1.芯片级验证与模块级验证的区别和联系

(1)芯片由模块组成

芯片是由若干模块自底向上例化而成。芯片级验证的重点是:模块间的、模块与顶层的互联;各个模块的功能;整体系统的功能;

对已完成模块级验证的模块,理论上芯片级仿真不必关注模块内部功能,但实际上,针对每个模块的内部功能,可挑选典型、重要的功能进行仿真。特别是关注模块在系统中是否工作正常。

对未进行独立模块级验证模块,采取”系统中验模块“

(2)芯片是特殊的模块

在更高层级,芯片亦是模块

2.芯片级验证测试点分解步骤

(1)模块间、模块与顶层的互联检查

通过芯片级DUT的spe以及其他形式文档,例如封装说明,应用手册等获得各个模块之间的连接关系、芯片全部端口与各个模块之间的连接关系。

通过各个模块的spec的端口列表确定每个模块输入信号的来源。

(2)在系统中测模块“的模块验证

参考模块级验证

(3)各个模块在系统中的基本功能验证

针对模块本身

(4)全芯片角度功能验证

例1:X->AHB_BUF->Memories,需检查数据传输是否正确;AHB_BUF对Memories地址访问范围。

例2:系统软硬件协同仿真:CPU初始化Y模块、使能中断模块、使能Y模块开始传输数据、发生中断事件、cpu进入中断服务程序、处理中断时间、清中断,这一系列操作功能检查

(5)芯片级特有测试点验证

a.时钟、复位;

b.上电/断电/休眠/重启/…

c.中断

d.软硬件交互

e.功耗仿真

f.pad、pin功能仿真

g.应用级、压力测试

h.DFT/门级仿真

…

最后

以上就是聪明蚂蚁最近收集整理的关于IC验证之测试点分解的全部内容,更多相关IC验证之测试点分解内容请搜索靠谱客的其他文章。

发表评论 取消回复