IC验证——MCDF结构 - 知乎

目录

- MCDF简介

- 通道模块(_Channel)

- 寄存器模块(_Registers)

- 仲裁模块(_Arbiter)

- 整形器模块(_Formater)

MCDF简介

这个例子作为IC验证的入门案例,接下来所有的关于语法和试验都会从这个例子展开所有我们一遍看功能文档一边对照Verilog语句实现仔细弄清楚这个设计的各个部分。

该设计我们称之为多通道数据整形器(MCDF,multi-channel data formatter),它可以将上行(uplink)多个通道数据经过内部的FIFO,最终以数据包(data packet)的形式送出。

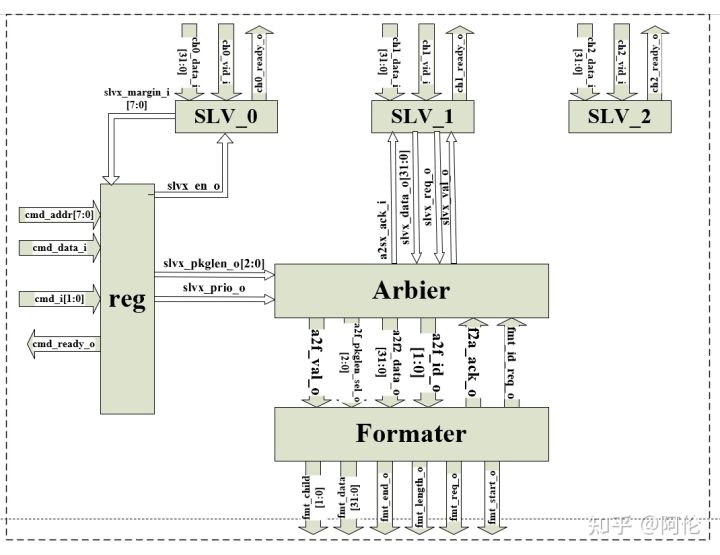

MCDF结构图

MCDF结构描述

因为内部信号太多同一类型统一表示,时钟和复位信号每个模块都有没有表示,上图x表示0,1,2

从上图的MCDF结构来看主要可以分为如下几个部分:

- 上行数据的通道从端(Channel Slave),负责接收上行数据,并且存储到其FIFO中。

- 仲裁器(Arbiter)可以选择从不同的FIFO中读取数据,进而将数据进一步传送至整形器(formatter)。

- 整形器(Formatter)将数据按照一定的接口时序送出至下行接收端。

- 控制寄存器(Control Registers)有专用的寄存器读写接口,负责接收命令并且对MCDF的功能做出修改。

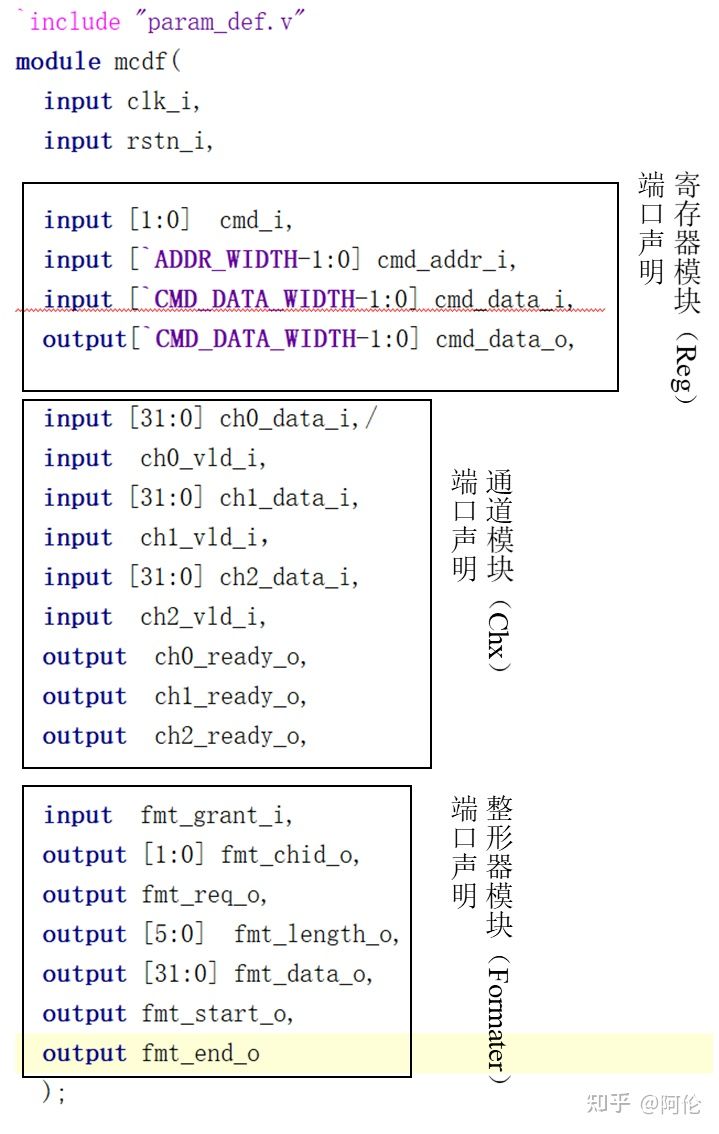

MCDF顶层文件

MCDF顶层文件

由顶层文件我们也可以看出仲裁器模块是MCDF整个系统的中间模块并没有外部接口。接下来我们先简略看一下各模块功能描述。

MCDF模块功能描述

接口描述

1、系统信号接口

- CLK(0):时钟信号。

- RSTN(0):复位信号,低位有效。

2、通道从端接口

- CHx_DATA(31:0):通道数据输入。

- CHx_VALID(0):通道数据有效标志信号,高位有效。

- CHx_READY(0):通道数据接收信号,高位表示接收成功。

3、整形器接口

- FMT_CHID(1:0):整形数据包的通道ID号。

- FMT_LENGTH(4:0):整形数据包长度信号。

- FMT_REQ(0):整形数据包发送请求。

- FMT_GRANT(0):整形数据包被允许发送的接受标示。

- FMT_DATA(31:0):数据输出端口。

- FMT_START(0):数据包起始标示。

- FMT_END(0):数据包结束标示。

4、控制寄存器接口

- CMD(1:0):寄存器读写命令。

- CMD_ADDR(7:0):寄存器地址。

- CMD_DATA_IN(31:0):寄存器写入数据。

- CMD_DATA_OUT(31:0):寄存器读出数据。

接口时序

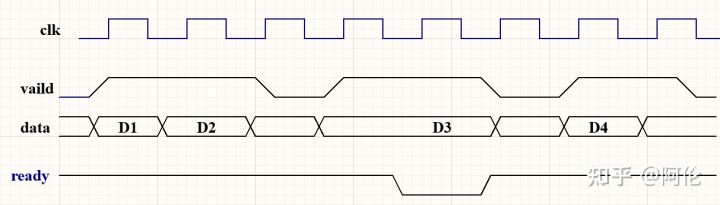

1、通道从端接口时序

通道从端接口时序

当valid为高时,表示要写入数据。如果该时钟周期ready为高,则表示已经将数据写入;如果该时钟周期ready为低,则需要等到ready为高的时钟周期才可以将数据写入。

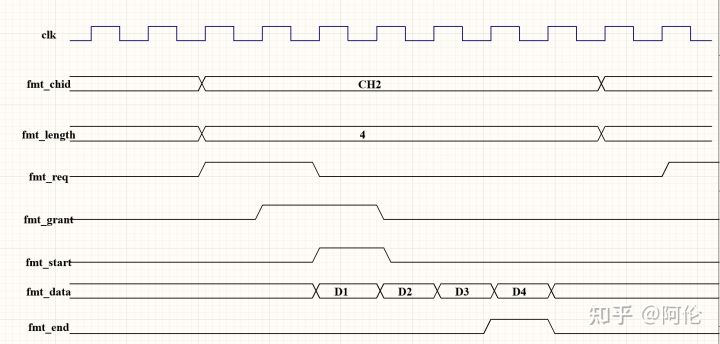

2、整形器接口时序

整形器接口时序

- 整形器发送数据是按照数据包的形式发送的,可以选择数据包的长度有4、8、16和32。整形器必须完整发送某一个通道的数据包后,才可以转而准备发送下一个数据包,在发送数据包期间,fmt_chid和fmt_length应该保持不变,直到数据包发送完毕。

- 在整形器准备发送数据包时,首先应该将fmt_req置为高,同时等待接收端的fmt_grant。当fmt_grant变为高时,应该在下一个周期将fmt_req置为低。fmt_start也必须在接收到fmt_grant高有效的下一个时钟被置为高,且需要维持一个时钟周期。在fmt_start被置为高有效的同一个周期,数据也开始传送,数据之间不允许有空闲周期,即应该连续发送数据,直到发送完最后一个数据时,fmt_end也应当被置为高并保持一个时钟周期。

- 相邻的数据包之间应该至少有一个时钟周期的空闲,即fmt_end从高位被拉低以后,至少需要经过一个时钟周期,fmt_req才可以被再次置为高。

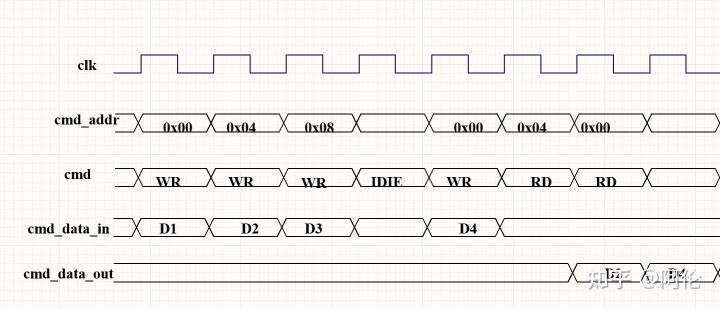

3、控制寄存器接口时序

控制寄存器接口时序

在控制寄存器接口上,需要在每一个时钟解析cmd。当cmd为写(WR)指令时,需要把数据cmd_data_in写入到cmd_addr对应的寄存器中;当cmd为读指令(RD)时,即需要从cmd_addr对应的寄存器中读取数据,并在下一个周期,将数据驱动至cmd_data_out接口。

寄存器描述

1、地址0x00 通道1控制寄存器 32bits 读写寄存器

- bit(0):通道使能信号。1为打开,0位关闭。复位值为1。 bit(2:1):优先级。0为最高,3为最低。复位值为3。

- bit(5:3):数据包长度,解码对应表为, 0对应长度4,1对应长度8,2对应长度16,3对应长度32,其它数值(4-7)均暂时对应长度32。复位值为0。

- bit(31:6):保留位,无法写入。复位值为0。

2、地址0x04 通道2控制寄存器 32bits 读写寄存器

同通道1控制寄存器描述。

3、地址0x08 通道3控制寄存器 32bits 读写寄存器

同通道1控制寄存器描述。

4、地址0x10 通道1状态寄存器 32bits 只读寄存器

- bit(7:0):上行数据从端FIFO的可写余量,同FIFO的数据余量保持同步变化。复位值为FIFO的深度数。

- bit(31:8):保留位,复位值为0。

5、地址0x14 通道2状态寄存器 32bits 只读寄存器

同通道1状态寄存器描述。

6、地址0x18 通道3状态寄存器 32bits 只读寄存器

同通道1状态寄存器描述。

上面的描述可以使用两个表来表示

表一:读写寄存器RW_addr(0x00/0x04/0x08这三个即是读写寄存器通道一到三的地址)每个通道有32位

| 位数 | 0 | 1~2 | 3~5 | 6~13 |

|---|---|---|---|---|

| 功能 | 通道使能信号 | 设定优先级 | 数据包长度 | 保留位无法写入复位值为0 |

| 设置 | 1为打开(复位值) 0为关闭 | 0为最高 3为最低(复位值) | 0:长度为4(复位值) 1:长度为82:长度为163~7:长度为32 |

表二:制度寄存器R_addr(0x10/0x14/0x18)

| 位数 | 0~7 | 8~31 |

|---|---|---|

| 功能 | 上行数据从端FIFO的写余量同FTFO的数据量保持同步变化(复位值:FIFO的深度数) | 保留位(复位值:0) |

上面是关于MCDF结构的简要介绍,下一节将从程序的角度详细介绍MCDF结构。

编辑于 2022-03-30 10:04

最后

以上就是能干大神最近收集整理的关于IC验证——MCDF结构的全部内容,更多相关IC验证——MCDF结构内容请搜索靠谱客的其他文章。

发表评论 取消回复