前言

《数字电子技术基础》第6.1和6.2节学习笔记,本人在编写Verilog时序逻辑代码时,关于这一部分的状态图FSM需要好好学一下。参考清华大学王红来时的国家精品课。

6.1 概述

一、时序逻辑电路的特点

- 功能上:任意时刻的输出不仅取决于该时刻的输入,还与电路原来的状态有关。

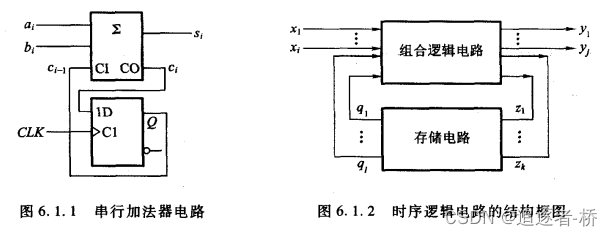

- 电路结构上:包含存储电路和组合电路;存储器状态和输入变量共同决定输出。

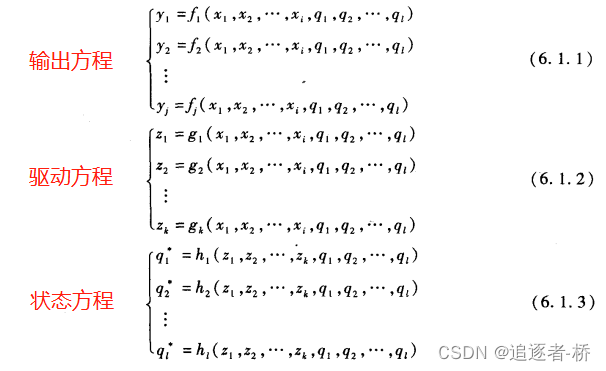

二、时序电路的一般结构形式与功能描述

三、时序电路的分类

1、同步时序电路与异步时序电路

同步:存储电路中所有触发器的时钟使用统一的clk,状态变化发生在同一时刻。

异步:没有统一的clk,触发器状态的变化有先有后。

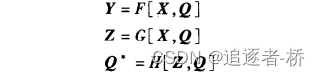

2、Mealy型和Moore型

Mealy型:Y = F(X,Q) 与X、Q有关

Moore型:Y = F(Q) 仅取决于电路状态

区别在于输出是否与时钟同步,Q与时钟有关

6.2 时序电路的分析方法

6.2.1 同步时序电路的分析方法

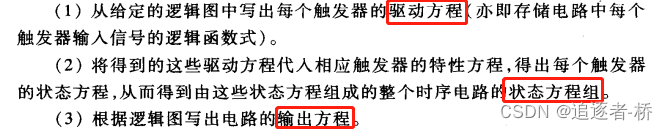

分析:找出给定时序电路的逻辑功能,即找出输入x和时钟clk作用下,电路的次态和输出。

一般步骤:

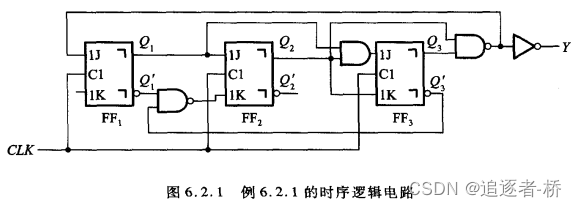

例:

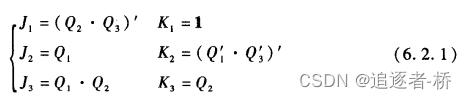

到触发器的就断掉,最终自变量为Q本身。驱动方程:

JK触发器的特征方程Q*=JQ'+K'Q于是得到电路的状态方程:

输出方程:![]()

6.2.2 状态转换表、状态转换图、状态机流程图和时序图

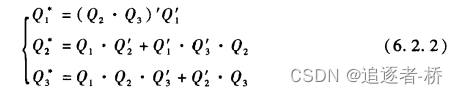

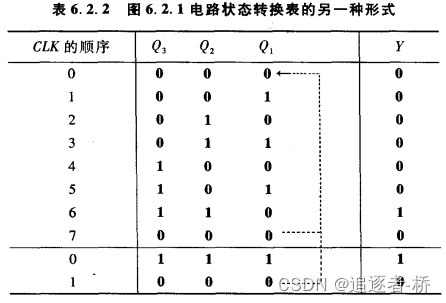

一、状态转换表(真值表)

上面的状态方程与输出方程的真值表:

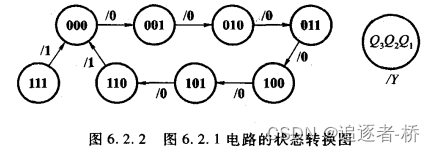

二、状态转换图

Mealy型将Y放在外面。

Moore型将Y放到⚪的里面,因为Y只与现态有关,所以上图需要进行一下改变。

能够自启动的电路,其状态图必定能形成回路。无效态尽量可以回到最初态。

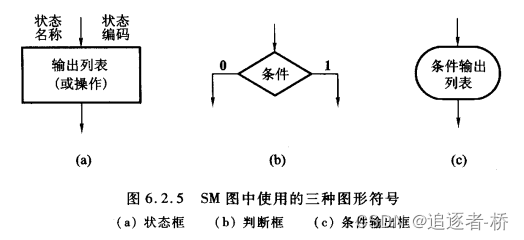

三、状态机流程图(SM图)

状态机流程图(SM图),也可以称为ASM图。思想类似于编写计算机程序时使用的程序流程图。

*6.2.3 异步时序逻辑电路的分析方法

只能规规矩矩从头往后分析,没有简便方法。由于比较繁琐这里不详细介绍。

最后

以上就是瘦瘦大碗最近收集整理的关于《数字电子技术基础》6.1/2 时序逻辑电路——概述及分析方法前言6.1 概述6.2 时序电路的分析方法的全部内容,更多相关《数字电子技术基础》6.1/2内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复