vivado如何做延时

- 0 不延时

- 1 短暂延时

- 1.1

- 1.2

- 2 长时间延时

0 不延时

assign b=a;

此时a,b的时序一样。

1 短暂延时

1.1

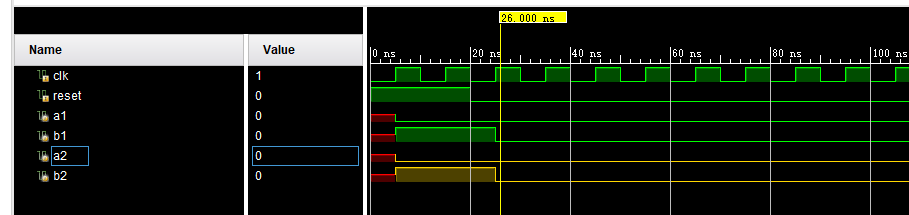

always @(posedge clk)

begin

b1<=a1;

end

always @(posedge clk)

begin

b2=a2;

end

这两种情况,b都是滞后a一个clk。也就是说,只要用到了always @(posedge clk),那么b读取到的值是a上一时刻的值。

1.2

基础知识:

(1)符号“=”用于阻塞的赋值(如:b = a;)。阻塞赋值“=”在 begin 和 end 之间的语句是顺序执行,属于串行语句。

(2)符号“<=”用于非阻塞赋值(如:b <= a;)。非阻塞赋值是由时钟节拍决定,在时钟上升到来时,执行赋值语句右边,然后将 begin-end 之间的所有赋值语句同时赋值到赋值语句的左边。注意:是 begin—end 之间的所有语句,一起执行,且一个时钟只执行一次,属于并行执行语句。

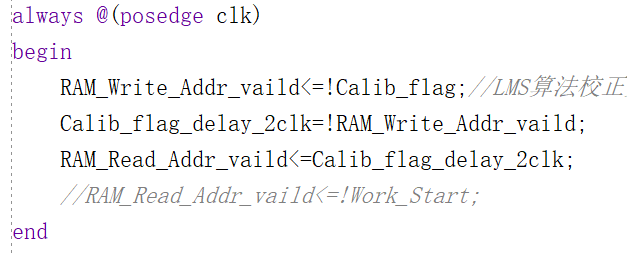

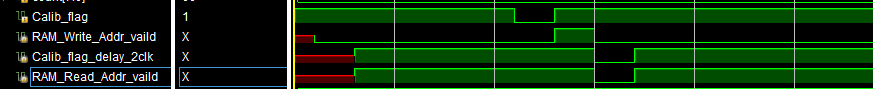

RAM_Write_Addr_vaild信号滞后于Calib_flag一个周期。

Calib_flag_delay_2clk信号滞后于RAM_Write_Addr_vaild一个周期;相当于Calib_flag_delay_2clk信号滞后于Calib_flag两个周期。

RAM_Read_Addr_vaild和Calib_flag_delay_2clk信号同步。

2 长时间延时

第一种方法

if(!empty)

begin

if(count_empty<8'd30)

begin

count_empty<=count_empty+1'b1;

end

else if(count_empty==8'd30)

begin

wr_en <= 1'b0;//写使能无效

rd_en <= 1'b1;//读使能有效

ST_fifo <= 4;

end

else

begin

wr_en <= 1'b0;//写使能无效

rd_en <= 1'b0;//读使能无效

ST_fifo <= 0;

end

end

第二种方法

//模块功能:Calib_State=0后,延时一定时间,然后将Work_Start拉低

reg [7:0] Calib_State_delayCount;

reg [3:0] ST_Calib_State;//状态机

reg Calib_State_delay50clk;

always @(posedge clk)

begin

if(reset)

begin

Calib_State_delayCount<=8'd0;//计数器

ST_Calib_State<=4'd0;//状态0

Calib_State_delay50clk<=1'b0;

end

else

begin

case(ST_Calib_State)

0://进入状态0

if(!Calib_State)//完成LMS校正

begin

Calib_State_delayCount<=Calib_State_delayCount+1'b1;

ST_Calib_State<=4'd1;

end

1:

if(Calib_State_delayCount==8'd50)

begin

ST_Calib_State<=4'd2;

Calib_State_delayCount<=Calib_State_delayCount;//停止计数

end

else

begin

ST_Calib_State<=4'd0;

end

2:

Calib_State_delay50clk=1'b1;

default :

ST_Calib_State<=4'd0;

endcase

end

end

assign Work_Start=!Calib_State_delay50clk;

最后

以上就是神勇大山最近收集整理的关于vivado如何做延时0 不延时1 短暂延时2 长时间延时的全部内容,更多相关vivado如何做延时0内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复