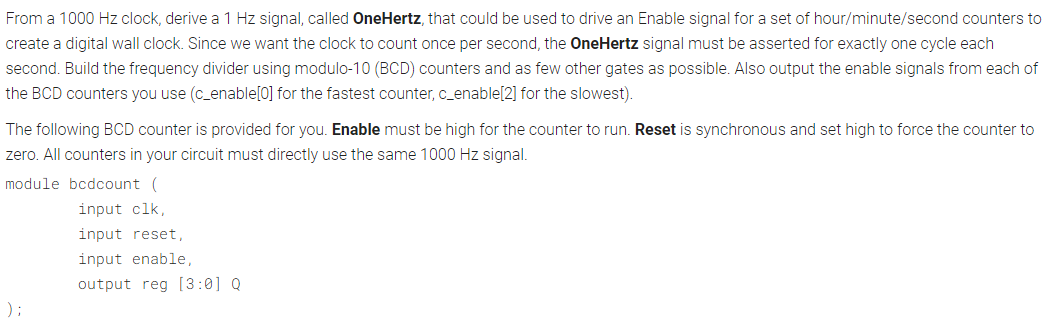

From a 1000 Hz clock, derive a 1 Hz signal, called OneHertz, that could be used to drive an Enable signal for a set of hour/minute/second counters to create a digital wall clock. Since we want the clock to count once per second, the OneHertz signal must be asserted for exactly one cycle each second. Build the frequency divider using modulo-10 (BCD) counters and as few other gates as possible. Also output the enable signals from each of the BCD counters you use (c_enable[0] for the fastest counter, c_enable[2] for the slowest).

The following BCD counter is provided for you. Enable must be high for the counter to run. Reset is synchronous and set high to force the counter to zero. All counters in your circuit must directly use the same 1000 Hz signal.

做这道题时可以说没有完全看懂,只知道做个分频器,由1000Hz转变到1Hz,给的子函数完全不知道怎么用,做这个题首先要明白子函数的作用。

子函数的作用:子函数就是一个0-9计数器,高电平使能和复位,当enable高电平时,Q计数+1,Q计数到9之后自动恢复为0.

那么使用三个这样的子函数分别作为个、十、百位,从0计数到999就可以了

bcdcount counter0 (clk, reset, c_enable[0], Q0);

//个位计数

bcdcount counter1 (clk, reset, c_enable[1], Q1);

//十位计数

bcdcount counter2 (clk, reset, c_enable[2], Q2);

//百位计数接下来的关键就是c_enable[0],c_enable[1],c_enable,[2]这三个使能值什么时候为高电平,c_enable[0]为个位计数,来一个时钟,计数就加一。

c_enable[1]为十位,当个位计数到9,十位就要加一。

c_enable[2]当个位和十位都要到9时,百位加一。

当个位、十位、百位都为9时,OneHertz变为高电平。

代码如下所示

assign c_enable[0] = 1;

assign c_enable[1] = Q0==9;

assign c_enable[2] = (Q0==9&Q1==9);

assign OneHertz = (Q0==9&Q1==9&Q2==9);最后

以上就是娇气小蝴蝶最近收集整理的关于HDL Bits刷题记录,counter1000,1Hz计数器的全部内容,更多相关HDL内容请搜索靠谱客的其他文章。

发表评论 取消回复