Verilog学习之路(9)—计数器和移位寄存器

一、前言

计数器是应用最广泛的逻辑部件之一。计数器可以统计输入脉冲的个数,具有计时、计数、分频、定时、产生节拍脉冲等功能。

计数器的种类繁多,根据计数器中触发器时钟端的链接方式,分为同步计数器和异步计数器;根据计数方式,分为二进制计数器、十进制计数器和任意进制计数器;根据计数器中的状态变化规律,分为加法计数器、减法计数器和加/减计数器。

移位寄存器可以用来实现数据的串并转换,也可以构成移位行计数器,进行计数、分频,还可以构成序列码发生器、序列码检测器等,它也是数字系统中应用非常广泛的时序逻辑部件之一。

二、二进制计数器

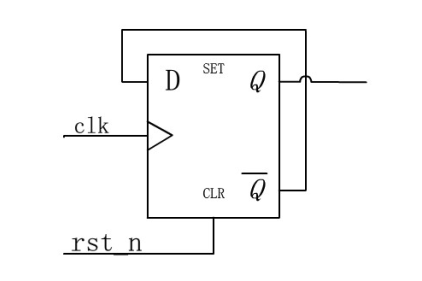

由D触发器实现的二进制计数器的VerilogHDL程序代码如下:

module comp2bit(Q, clk, rst_n);

output reg Q;

input clk, rst_n;

always@(posedge clk or negedge rst_n) begin

if(!rst_n)

Q <= 1'b0;

else

Q <= ~Q;

end

endmodule

其电路图如下所示

三、任意进制计数器

在数字电路系统中,经常会使用任意进制计数器,VerilogHDL可以很好地支持不同进制计数器的设计。

以11进制计数器为例,最少需要4个触发器。采用反馈清零法设计的11进制计数器的VerilogHDL程序代码如下所示:

module comp_11(cnt, clk, rst_n);

output reg [3:0] cnt;

input clk, rst_n;

always@(posedge clk) begin

if(!rst_n)

cnt <= 4'd0;

else if(cnt == 4'd10)

cnt <= 4'd0;

else

cnt <= cnt+4'd1;

end

endmodule

编写测试代码tb.sv如下所示

module tb;

reg clk, rst_n;

wire [3:0]cnt;

comp_11 dut(cnt, clk, rst_n);

always#5 clk = ~clk;

initial begin

clk = 0; rst_n = 0;

#20 rst_n = 1;

#200;

$stop;

end

endmodule

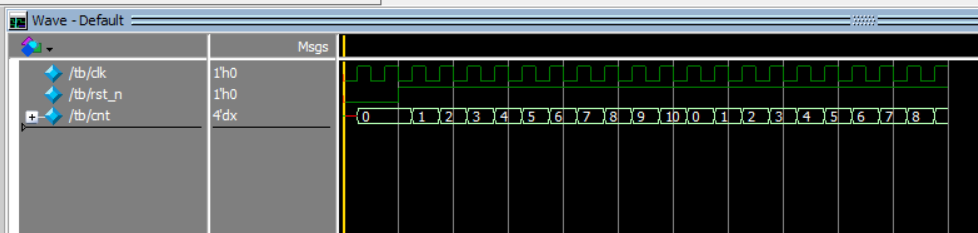

可得仿真波形如下所示,可以看到,该计数器在0~10共11个数之间循环计数

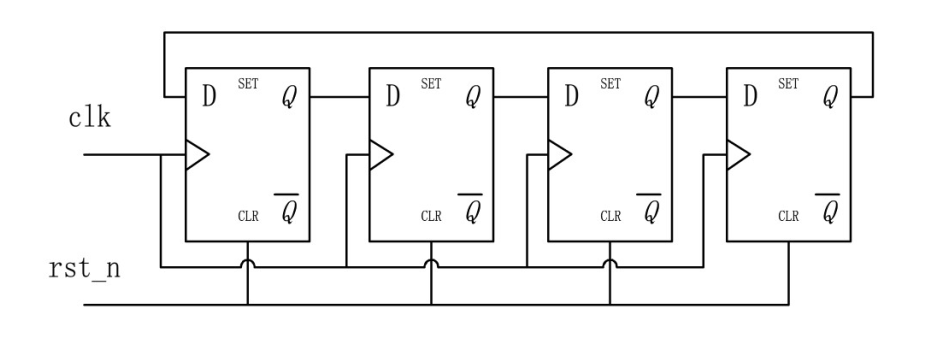

四、移位寄存器

N位环形移位寄存器由N个移位寄存器组成

一个参数化的移位寄存器如下所示,可通过参数来设置该移位寄存器位宽

module shiftregister(D, clk, rst_n);

parameter reg_width = 4;

output reg [reg_width-1:0] D;

input clk,rst_n;

always@(posedge clk) begin

if(!rst_n)

D <= 4'b0001;

else

D <= { D[reg_width-2:0], D[reg_width-1] };

end

endmodule

编写测试代码tb.sv如下所示

module tb;

reg clk, rst_n;

wire [3:0]cnt;

shiftregister dut(cnt, clk, rst_n);

always#5 clk = ~clk;

initial begin

clk = 0; rst_n = 0;

#20 rst_n = 1;

#200;

$stop;

end

endmodule

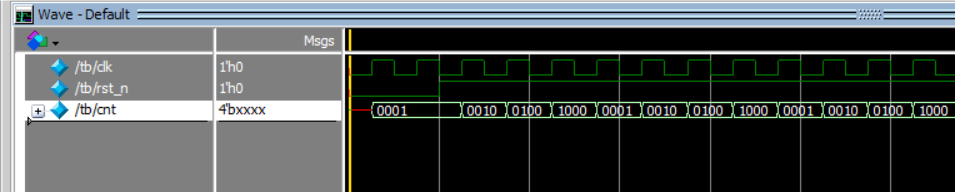

可得仿真波形如下所示,

五、附录

上一篇:Verilog学习之路(8)— 时序电路的设计

下一篇:

最后

以上就是爱笑黄蜂最近收集整理的关于Verilog学习之路(9)—计数器和移位寄存器Verilog学习之路(9)—计数器和移位寄存器的全部内容,更多相关Verilog学习之路(9)—计数器和移位寄存器Verilog学习之路(9)—计数器和移位寄存器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复