写在前面

本文是本系列的第三篇,本文主要介绍FPGA常用运算模块-乘加器,xilinx提供了相关的IP以便于用户进行开发使用。

乘加器

乘加器核提供使用DSP片的乘加实现。它执行两个操作数的乘法,并将全精度乘积加(或减)到第三个操作数,执行P = C +/- A * B的操作。乘加器模块对有符号或无符号数据进行操作。该模块可以流水线化。支持二补符号和无符号操作。支持从1到52位无符号或2到53位有符号的乘数输入和从1到105位无符号或2到106位有符号的加减操作数输入。可选时钟启用和同步清除。

乘加器IP在许多配置中比单独的乘和加操作更有效,因为它使用DSP48原语。可以在许多应用程序中使用这个IP,特别是那些基于多项式算法的应用程序,如FIR和IIR实现。

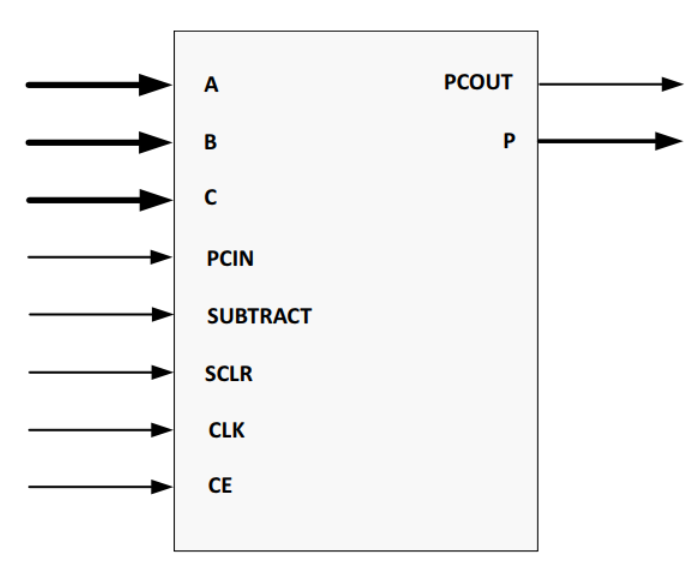

IP核图示以及端口介绍

| Name | I/O | Description |

|---|---|---|

| A[N:0] | Input | A输入(乘法操作数1) |

| B[M:0] | Input | B输入(乘法操作数2) |

| C[L:0] | Input | C输入(加减操作数) |

| PCIN | Input | 级联输入 |

| SUBTRACT | Input | 控制加/减操作(1=减法,0=加法) |

| CE | Input | 时钟使能 (高有效) |

| CLK | Input | 时钟信号,上升沿有效 |

| SCLR | Input | 同步复位,高有效 |

| PCOUT | Output | 输出级联 |

| P[Q:0] | Output | 输出端口 |

操作指南

流水操作

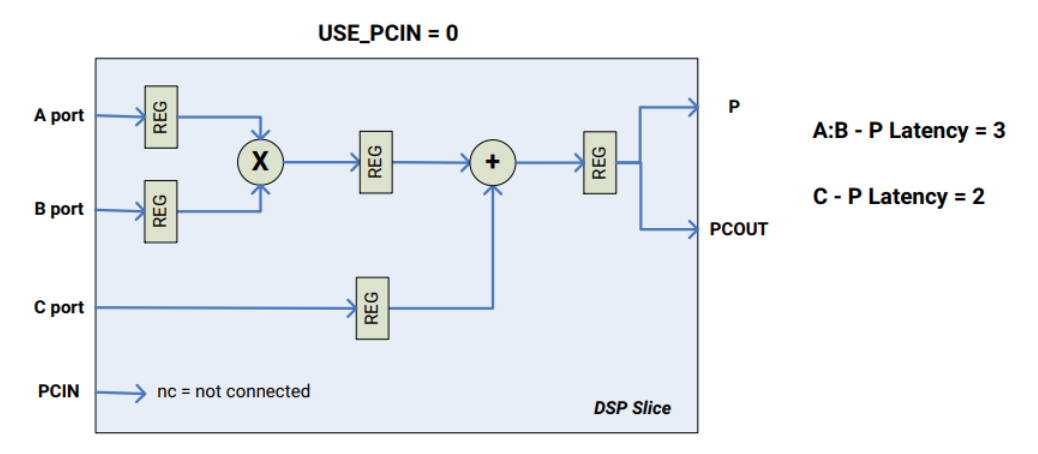

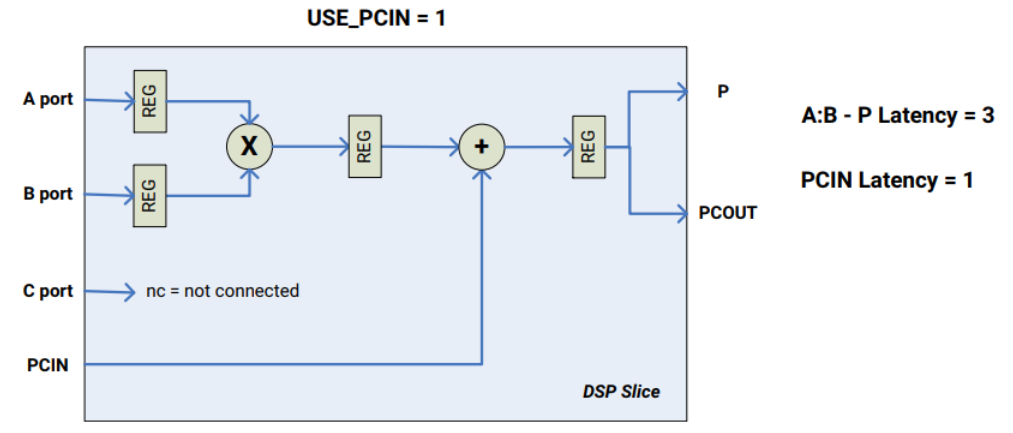

乘法器核心考虑了两种不同的延迟路径;一个是从A和B输入到P输出,另一个是从C/PCIN输入到P输出。这些延迟被定义为A:B - P延迟和C - P延迟。

这些延迟只能采用两个值:0 表示无延迟或 -1 表示最大/最佳延迟。 如果这两个延迟中的任何一个指定为 -1,则它们都被视为 -1; 对于完全组合的设计,两者都必须设置为 0。

级联的PCIN端口的使用也会影响延迟。

不用级联输入:

使用级联输入:

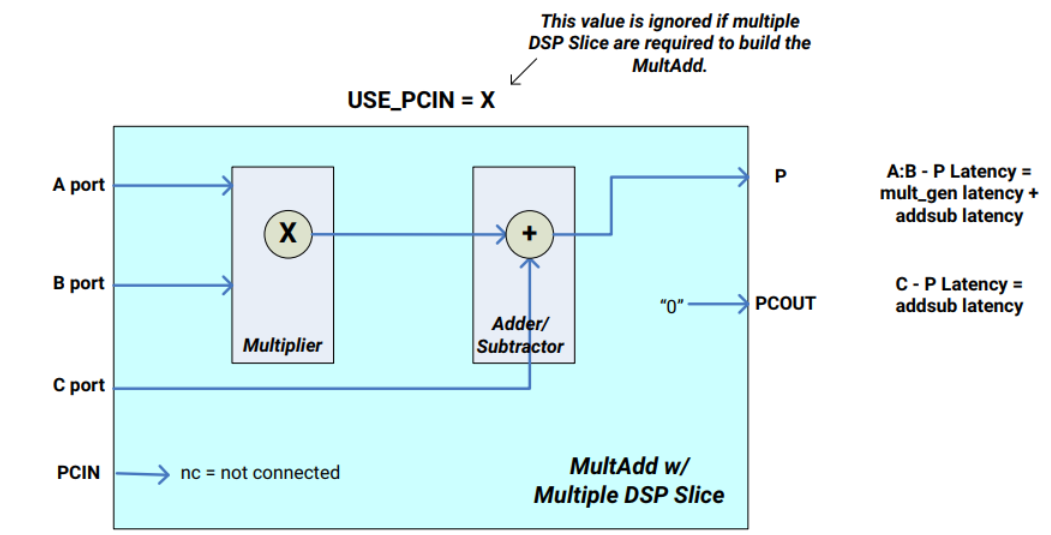

下图显示了乘加器的内部结构,在内部相当于引用了一个乘法器和一个加减法器。从该结构中可以清楚的看出,A:B - P 延时和C - P延时路径。

数据调整

当传递给IP输入时,所有输入都是右对齐的。必须设置输入的正确 LSB 或 MSB 填充或符号扩展(相当于二进制小数点)。

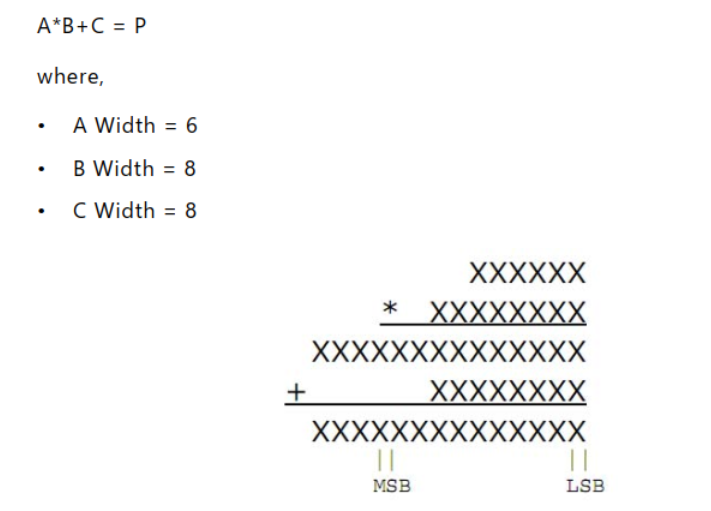

在乘法加法器中,乘法器输出没有截断或舍入;这是一个完整的精确结果。 C 输入被添加到乘积中。下面的例子实现了切片操作的功能。切片选取输出的0到11位。

向量相乘的例子

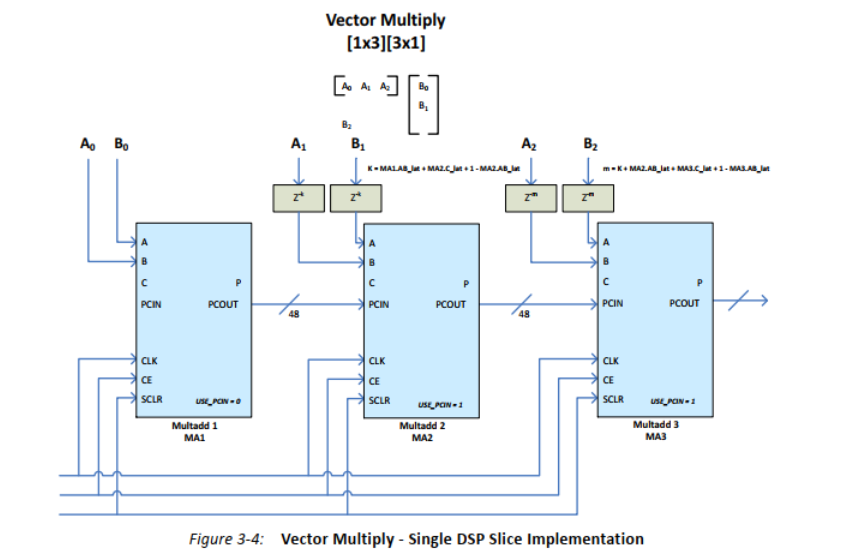

图3-4(单DSP片实现)和图3-5(多DSP片实现)实现了一个简单的矢量乘法。在3-4图中,如果使用单DSP片实现向量相乘,则按照该图示连接进行实现。采用级联操作,将级联是输入输出相互连接。此时不能进行设置C的输入。

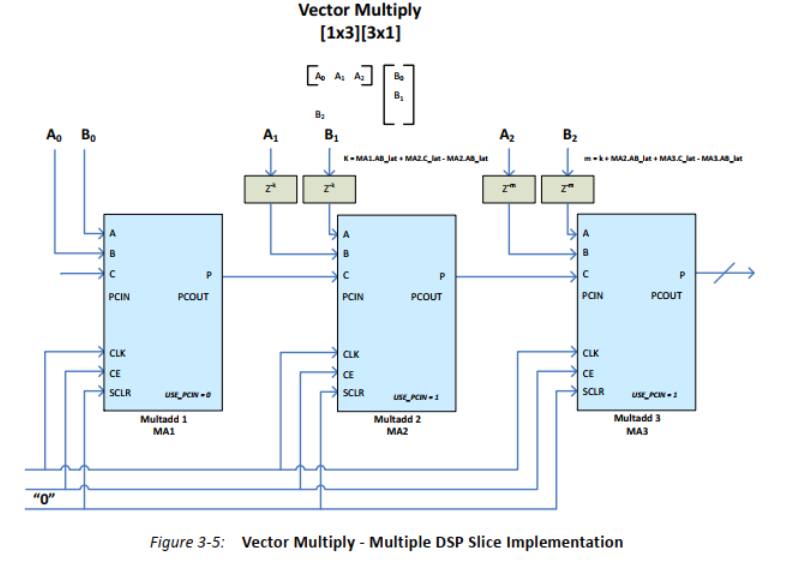

在3-5图中,如果使用多DSP片实现,则按照该图示连接进行实现。此时可以进行设置C的输入,级联操作通过连接P和C端相互连接。

乘加器IP配置

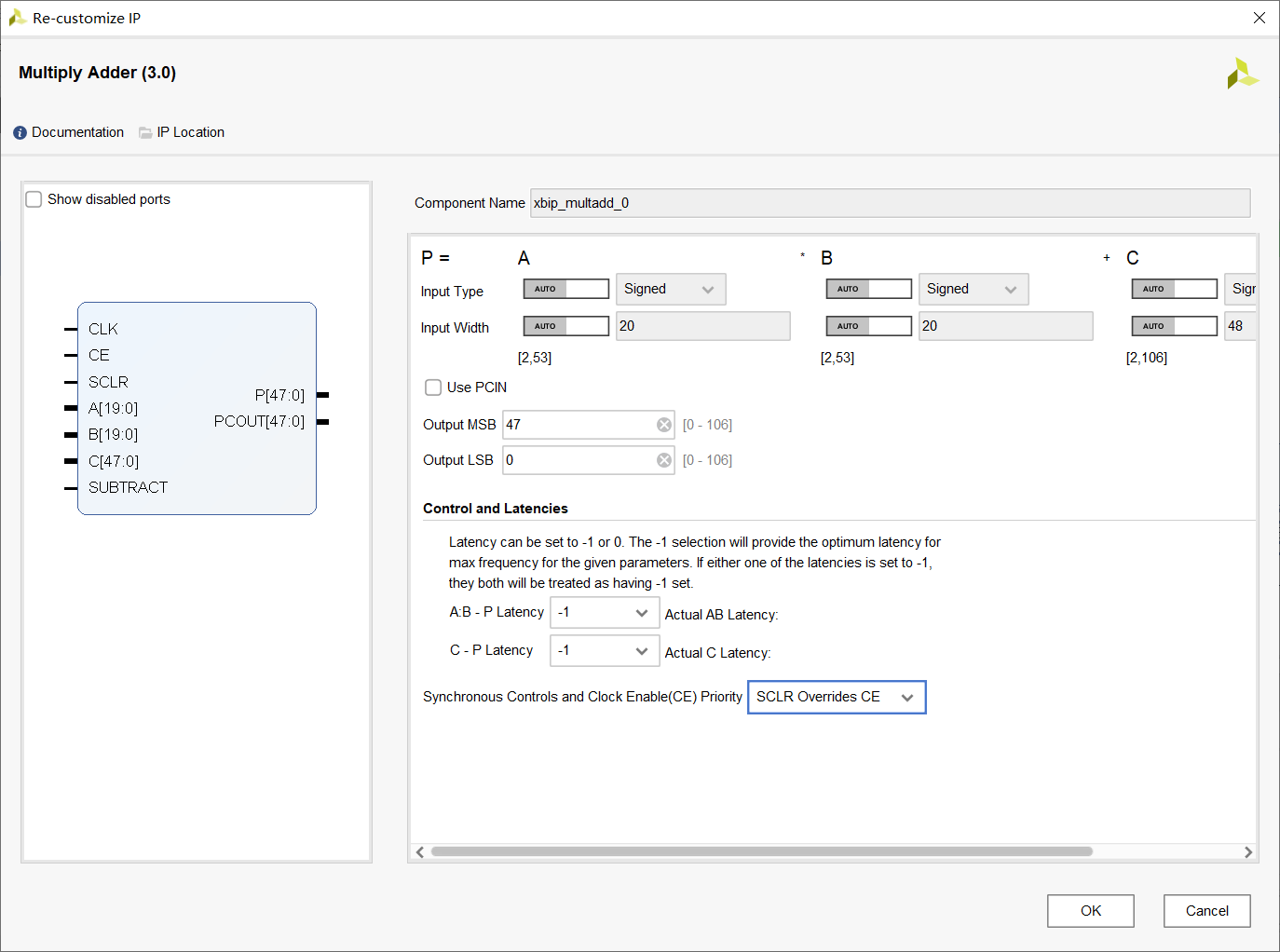

在乘加器IP配置界面,可以对输入输出的位宽进行配置,以及相关IP的配置。

A/B Input Width :设置端口A或者B输入的宽度。有效的范围是1 ~ 52无符号和2 ~ 53有符号。默认值为18。该值在IP中自动设置,可以手动设置。

C Input Width :设置端口C(加/减操作数)输入的宽度。有效的范围是1到105无符号和2到106有符号。默认值为48。该值在IP中自动设置,可以手动设置。

A/B/C Input Type :设置端口A、B 、C数据的类型。0表示有符号,1表示无符号。默认值为0。该值在IP中自动设置,可以手动设置。

Output MSB / Output LSB :设置输出的切片位宽范围。

Use PCIN :当该参数设置为1时,使用PCIN 端口。 PCIN 端口是

加法器/减法器操作数的级联输入端口。设置为0时,PCIN 端口为

忽略。设置为 1 时,C 输入宽度限制为 48 位。

Sync Control CE Priority :此参数控制 SCLR和CE信号的优先级当该信号为0时,Sync Control CE Priority。当该信号为1时,SCLR 仅在 CE 为高电平时有效。这默认值为0。

A:B - P Latency : A、B端口到输出端口P的时延。取值如下: -1, 0。默认值为-1。

C - P Latency :从 C 或 PCIN 端口到输出端口 P 的延迟。取值如下: -1, 0。默认值为-1。

References

- PG192

最后

以上就是复杂星月最近收集整理的关于数字信号处理-03- FPGA常用运算模块-乘加器写在前面乘加器References的全部内容,更多相关数字信号处理-03-内容请搜索靠谱客的其他文章。

发表评论 取消回复