目录

0.参考手册

1.DSP48总结

1.1 Spartan3硬件乘法器 DSP48A

1.2 Spartan-6 FPGA DSP48A1

1.3 V4系列 DSP48

1.4 V5硬件乘法器 DSP48E

1.5 7系列FPGA乘法器 DSP48E1

1.7 UltraScale Architecture DSP Slice ——DSP48E2

2.接触过的用到DSP48的IP核

2.1 复数乘法器IP核

2.2 FFT IP核

0.参考手册

下面对乘法器的介绍主要来自手册

| DSP48A | XtremeDSP DSP48A for Spartan-3A DSP FPGAs UG431 (v1.3) July 15, 2008 |

| DSP48A1 | Spartan-6 FPGA DSP48A1 Slice UG389 (v1.2) May 29, 2014 |

| DSP48 | XtremeDSP for Virtex-4 FPGAs UG073 (v2.7) May 15, 2008 |

| DSP48E | Virtex-5 FPGAXtremeDSP Design Considerations UG193 (v3.6) July 27, 2017 |

| DSP48E1 | 7 Series DSP48E1 Slice UG479 (v1.9) September 27, 2016 |

| DSP48E2 | UltraScale Architecture DSP Slice UG579 (v1.9) September 20, 2019 |

| DSP48 LogiCORE IP | DSP48 Macro v3.0 PG148 November 18, 2015 |

1.DSP48总结

1.1 Spartan3硬件乘法器 DSP48A

1)简介

DSP48A Slice是Spartan™-3A DSP系列FPGA所独有的。每个XtremeDSP slice都包含一个DSP48A slice,构成了通用的粗粒度DSP体系结构的基础。许多DSP设计采用加法运算。在Spartan-3A DSP器件中,这些元件在专用电路中受支持。

DSP48A Slice支持许多独立的功能,包括乘法器,乘法累加器(MACC),预加法器/减法器,后跟乘法累加器,乘法器后跟加法器,宽总线多路复用器,幅度比较器或宽计数器。该架构还支持连接多个DSP48A Slice,以形成广泛的数学功能,DSP滤波器和复杂的算术,而无需使用常规的FPGA结构。

所有Spartan-3A DSP系列成员均可使用的DSP48A Slice支持新的DSP算法和比FPGA中以前可用的更高级别的DSP集成。最小程度地使用常规FPGA架构可实现低功耗,超高性能和高效的芯片利用率。

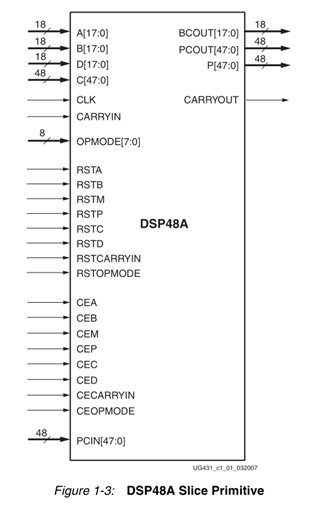

2)DSP48A Slice原语

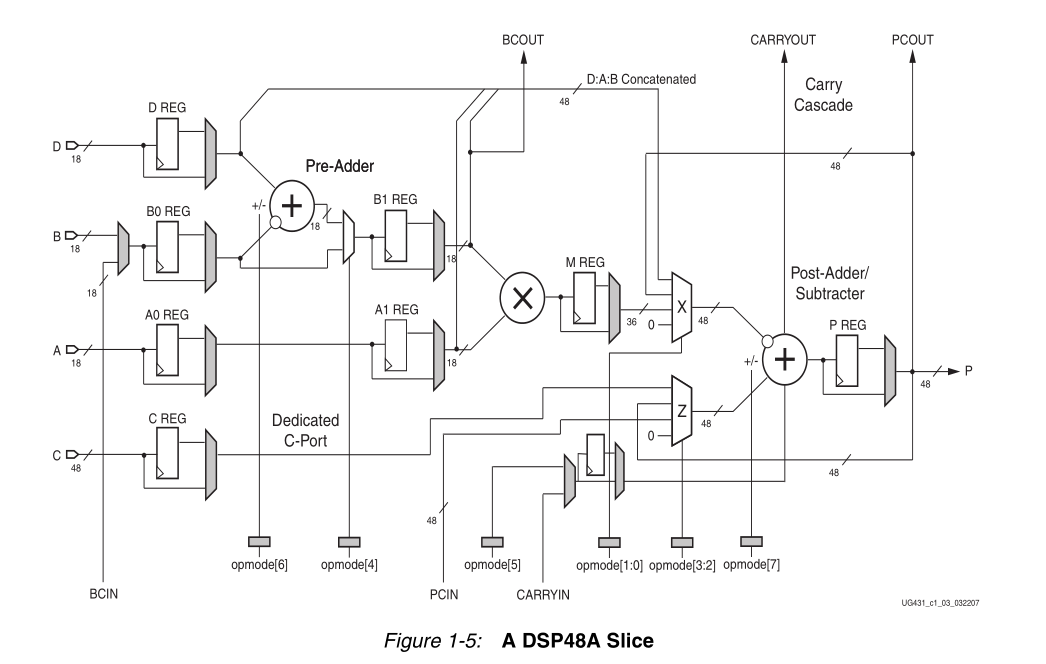

3)电路映射

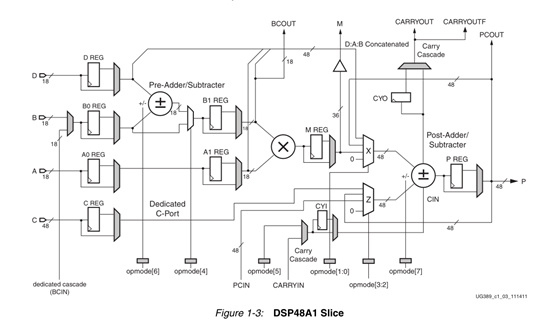

dsp48a的运算部分包括一个18位的预加器,其后是一个18×18的二进制补码乘法器,再后面通过两个48位数据通路多路复用器(x,z)连接二输入的48位加法器/减法器。数据和控制输入端口可直接输入dsp48a的运算单元,也可通过1级或2级流水寄存器输入,该结构有助于实现不同的及高速流水运作的dsp应用。a,b数据输入端口支持1级或2级流水寄存输入,其他数据或控制端口可寄存一次。当使用流水寄存器时,dsp48a的全速率为250 MHz。

在最基本的操作模式中,加法器/减法器的输入可来自于上级的多路复用器,进位选择逻辑和乘法器。式(11-3)描述了加法器/减法器的输出。carryin和x的输出总是相加,其结果可与z的输出相加或减:

adder out=(z ± (x + carryin))![]() (11-3)

(11-3)

式(11-4)描述了一种典型的使用乘法器的情况。a和b输入数据相乘,然后结果和c输入相加/减。当使用乘法功能时,加法器/减法器的输入将使用x多路复用器的输出,乘法器36位乘积在输出给乘法器之前将符号扩展为48位:

adder out=c±(a×b+carryin)![]() (11-4)

(11-4)

式(11-5)描述了b,d输入通过预加器相加减的情况。预加器的结果和a相乘,再与c相加。该方程可有效实现对称型的滤波器:

adder out=c±(a×(d±b)+carryin)![]() (11-5)

(11-5)

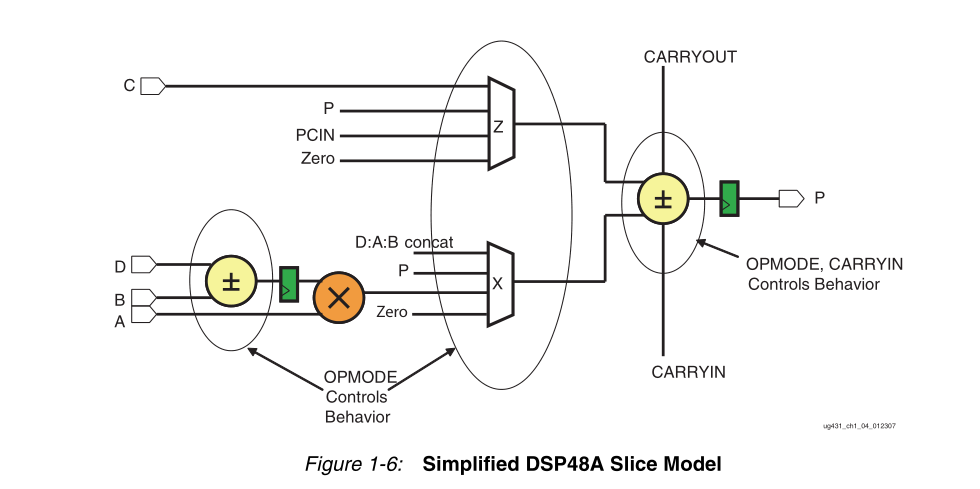

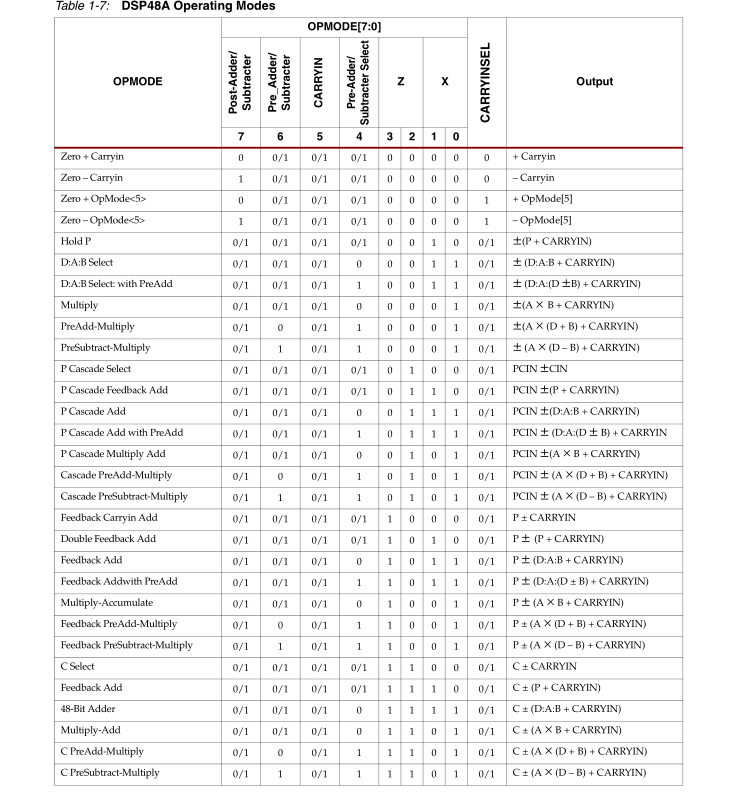

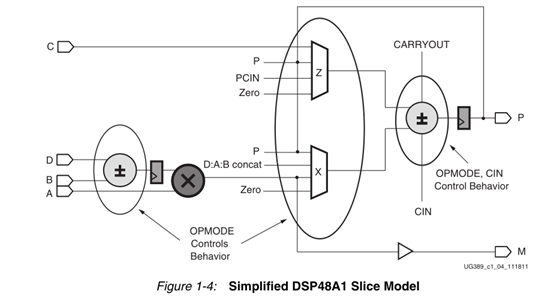

4)简化的DSP48A Slice模型

下图为dsp48a的简化形式,8位opmode控制二输入加/减法器的数据来源以及预加器和加法器/减法器的功能。在任何情况下,36位的数据经过多路复用器符号扩展为48位数据输入给后面的加法器/减法器。基于36位操作数和48位累加器输出,保证位(保证不溢出的位数)的位数为12。这样在溢出发生前可进行的乘累加的次数为4096次,组合opmode,carryinsel和carryin可控制预加器及加法器/减法器的功能。

5)DSP48A切片和互联

DSP48A切片垂直堆叠在DSP48A列中。 DSP48A Slice的高度与四个CLB相同,并且与一个Block RAM的高度匹配。 这种“规律性”增强了宽数据路径的路由。较小的Spartan-3A DSP(XC3SD1800A)系列成员具有四个DSP48A列。DSP48A Slice的高度与四个CLB相同,并且与一个Block RAM的高度匹配。 这种“规律性”增强了宽数据路径的路由。较小的Spartan-3A DSP(XC3SD1800A)系列成员具有四个DSP48A列,而较大的Spartan-3A DSP(XC3SD3400A)系列成员具有五个DSP48A列

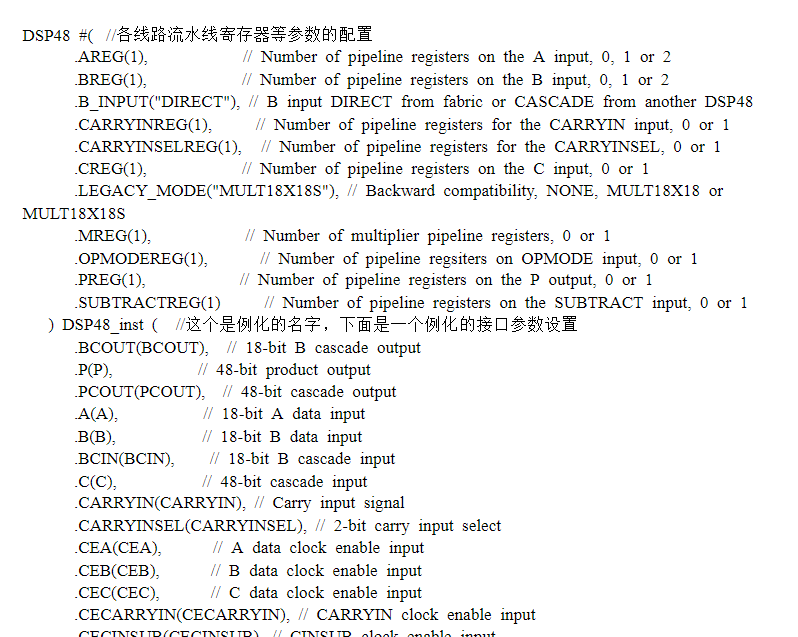

6)调用DSP48 Slice

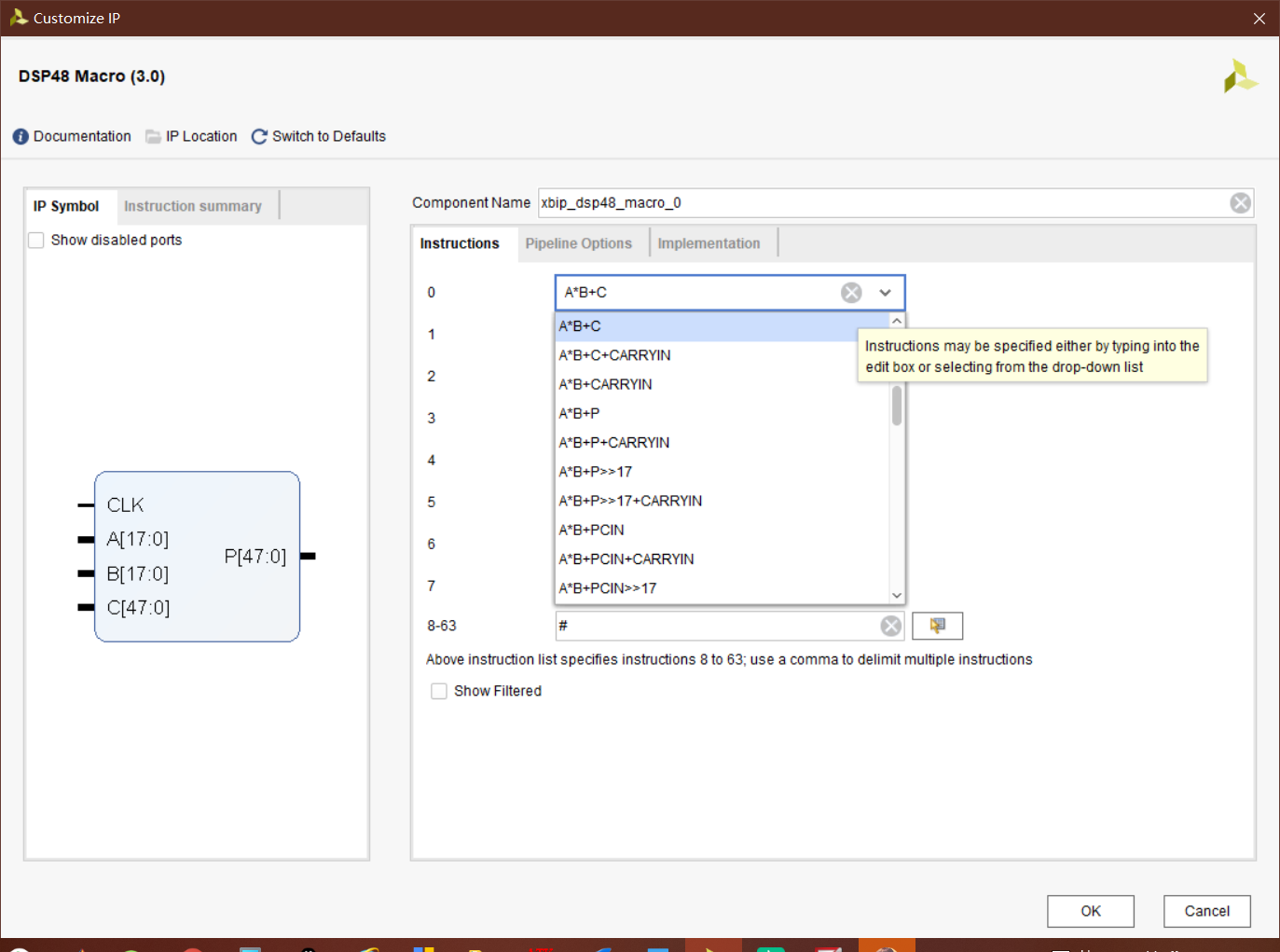

可以用原语实现,也可通过core generator调用。

1.2 Spartan-6 FPGA DSP48A1

1)点路映射

@)

@)

2)简化模型

3)最大运行频率

1.3 V4系列 DSP48

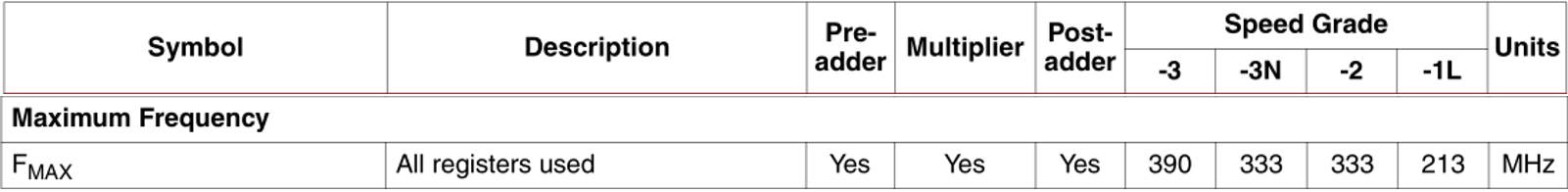

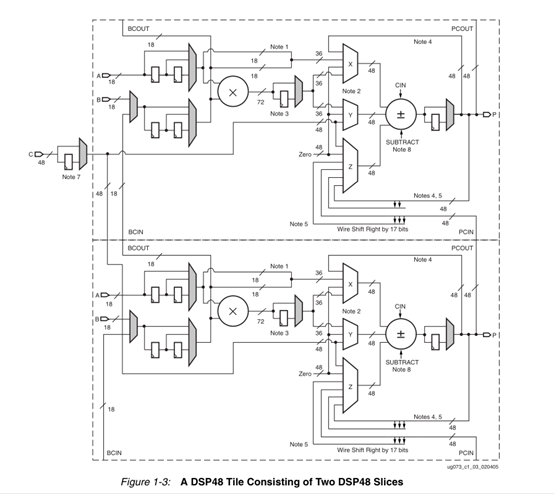

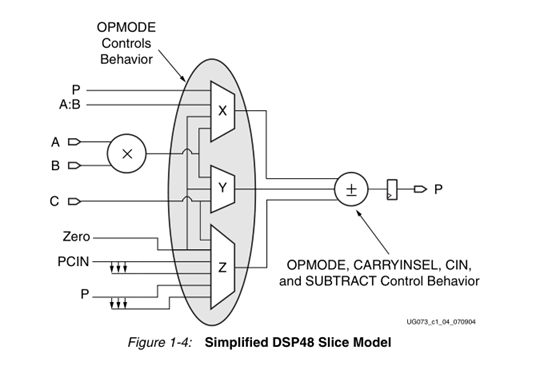

DSP48 Slice的数据和控制输入直接馈入算术部分,或者可选地注册一两次,以帮助构建不同的高度流水线的DSP应用解决方案。 数据输入A和B可以注册一次或两次。 其他数据输入和控制输入只能注册一次。 使用流水线寄存器时,全速运行为500 MHz。

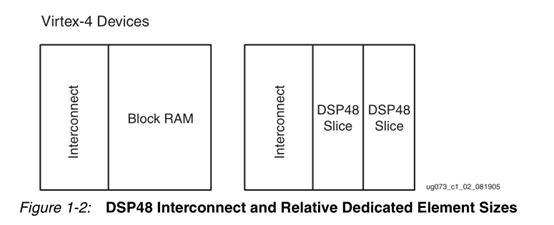

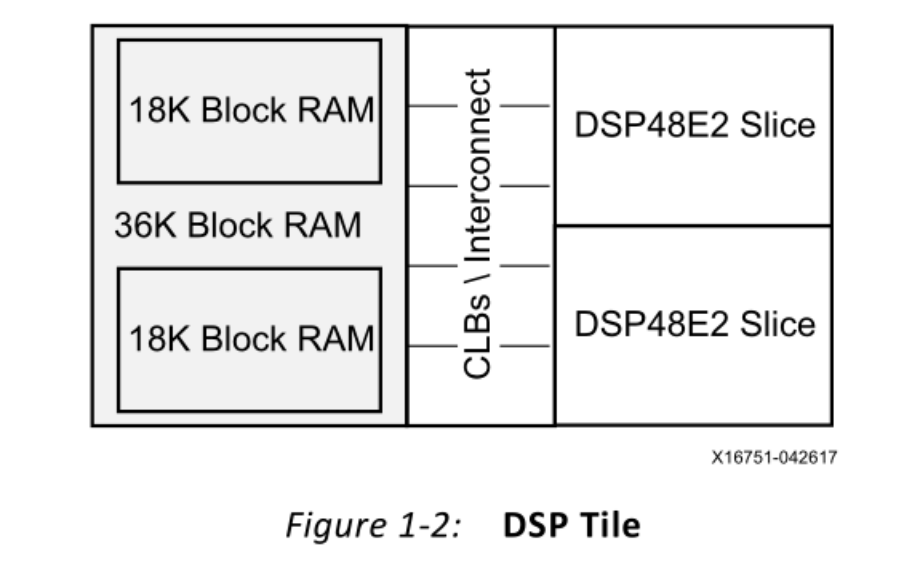

DSP48 tile的高度与四个CLB相同,并且与一个Block RAM的高度匹配。

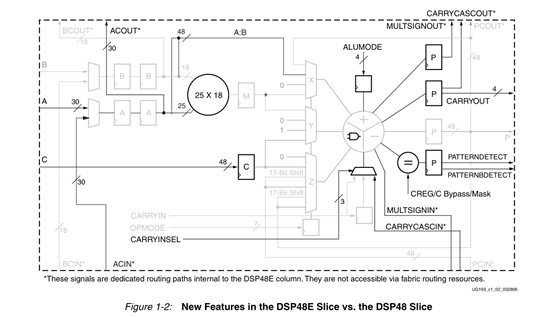

1.4 V5硬件乘法器 DSP48E

1)简介

Virtex-5 FPGA DSP48E Slice包括Virtex-4 FPGA DSP48的所有功能以及各种新功能。这些新功能包括一个更宽的25 x 18乘法器和一个加/减功能,该功能已扩展为逻辑单元。不使用乘法器时,该逻辑单元可以执行许多按位逻辑运算。 DSP48E Slice包括一个模式检测器和一个模式条检测器,可用于收敛舍入,用于饱和算术的上溢/下溢检测以及自动复位计数器/累加器。 加法器/减法器/逻辑单元的单指令多数据(SIMD)模式也是DSP48E Slice的新功能。 不使用乘法器时,此模式可用。 Virtex-5 DSP48E Slice还具有新的级联路径。

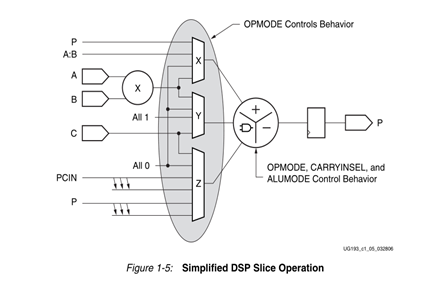

2)简化模型

![]()

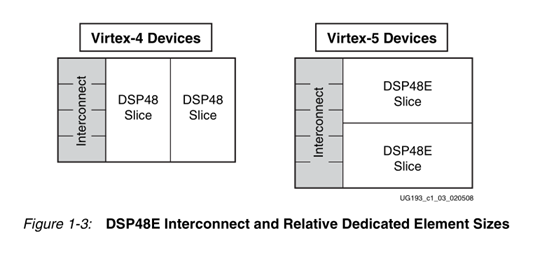

3)DSP48E平铺和互连

两个DSP48E Slice和专用互连形成一个DSP48E Tile(见图1-3)。 DSP48E tile垂直堆叠在DSP48E列中。 DSP48E tile的高度与五个可配置逻辑模块(CLB)相同,并且与一个模块RAM的高度匹配。Virtex-5器件中的Block RAM可以分为两个18K Block RAM。 每个DSP48E Slice均与18K Block RAM水平对齐。 Virtex-5系列成员具有一,二,六或十个DSP48 Ecolumn。

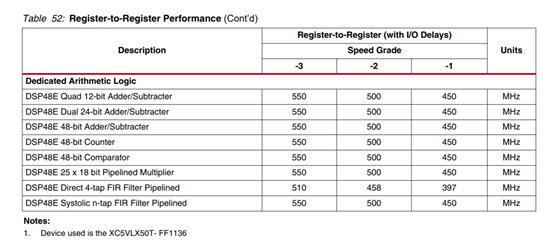

4)最大运行频率

使用流水线寄存器时,全速运行为550 MHz

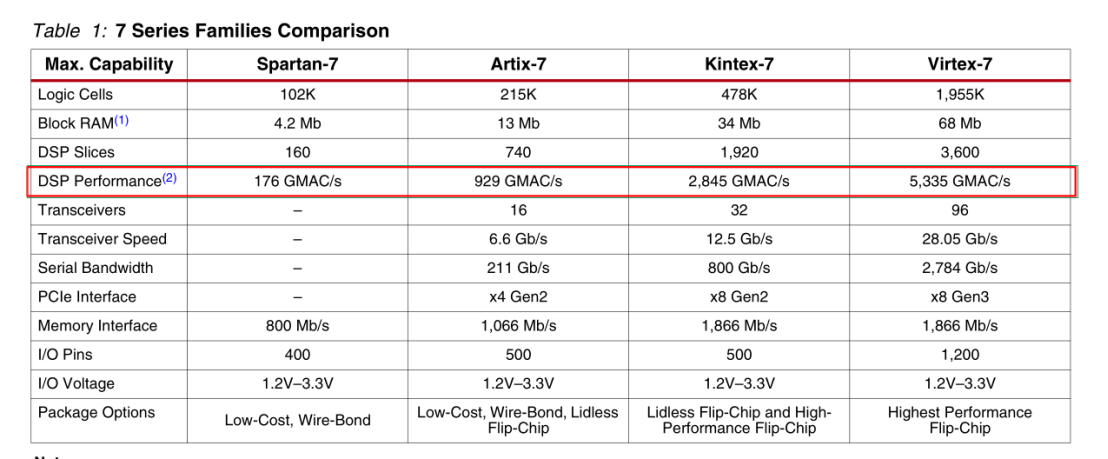

1.5 7系列FPGA乘法器 DSP48E1

1)简介

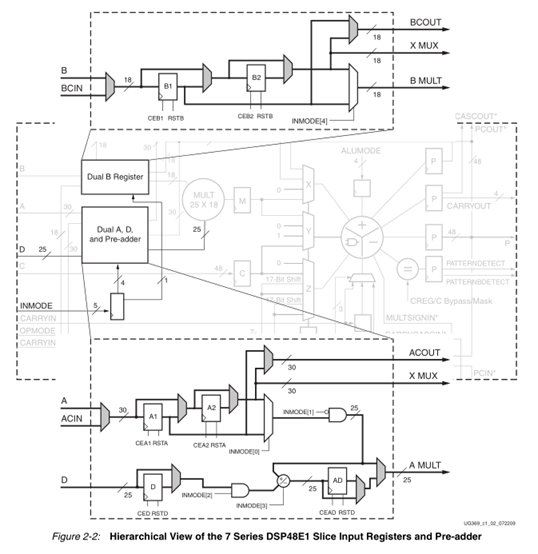

7系列FPGA DSP48E1 Slice在功能上等效于Virtex-6 FPGA DSP48E1。 7系列FPGA DSP48E1 Slice在A寄存器之后有一个预加器,带有一个称为D的25位输入向量。D寄存器可用作预加器寄存器或乘法器的备用输入。

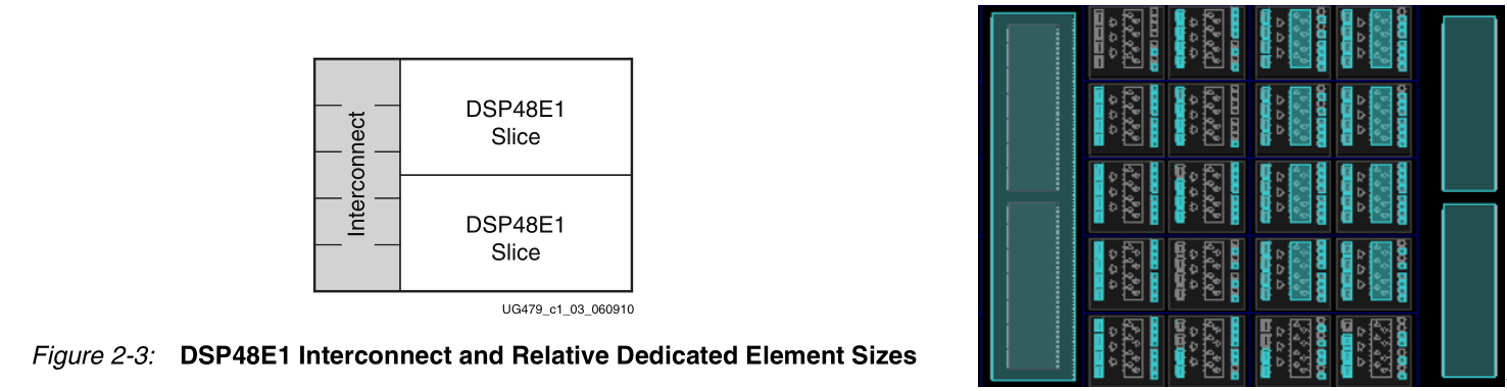

2)DSP48E1 Tile and Interconnect

两个DSP48E1 Slice和专用互连形成一个DSP48E1 tile(见图2-3)。 DSP48E1磁贴垂直堆叠在DSP48E1列中。 DSP48E1磁贴的高度与五个可配置逻辑模块(CLB)相同,并且与一个模块RAM的高度匹配。 7系列设备中的Block RAM可以分为两个18K Block RAM。 每个DSP48E1 Slice均与18K Block RAM水平对齐。 7系列器件具有多达20个DSP48E1列。

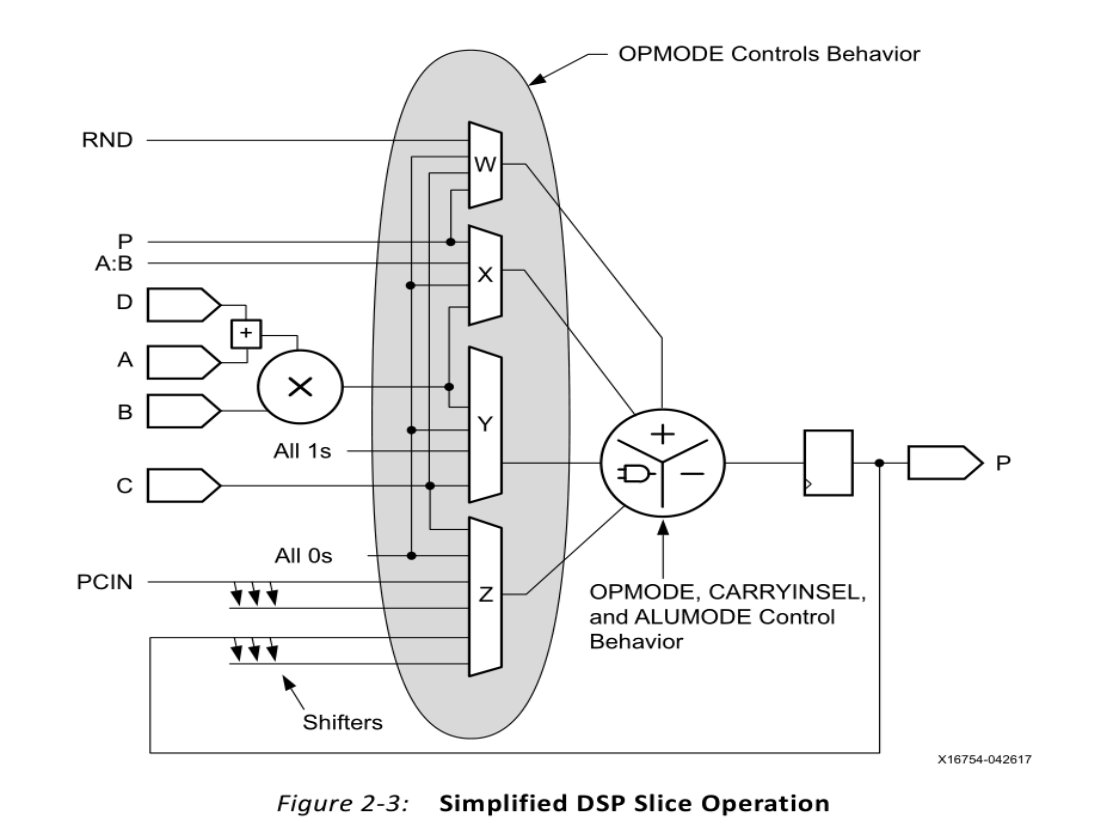

其实从框图我们就能知道。首先,有4个输入,分别是A、B、C、D。一个输出P。从输入得到输出,我们用一个函数公式表达:

P=(D±A)*B±C![]()

请把这个公式背下来,之后的变形使用也靠它了。这里面A是30bit,B是18bit,C是48bit,D是25bit。(D±A)出来是25bit,乘法就是25*18bit。P是48bit。

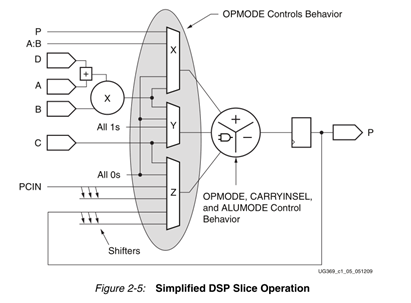

DSP48E1 Slice的数学部分包括一个25位预加器,一个25位乘18位的2的补码乘法器,以及随后的三个48位数据路径多路复用器(输出X,Y和Z)。 随后是三输入加法器/减法器或两输入逻辑单元(见图2-5)。 使用两输入逻辑单元时,不能使用乘法器。

3)fmax

每个DSP Slice基本上都由一个专用的25×18位二进制补码乘法器和一个48位累加器组成,两者均能够以高达741 MHz的频率工作。 可以动态旁路乘法器,并且两个48位输入可以提供一个单指令多数据(SIMD)运算单元(双24位加/减/累加或四通道12位)

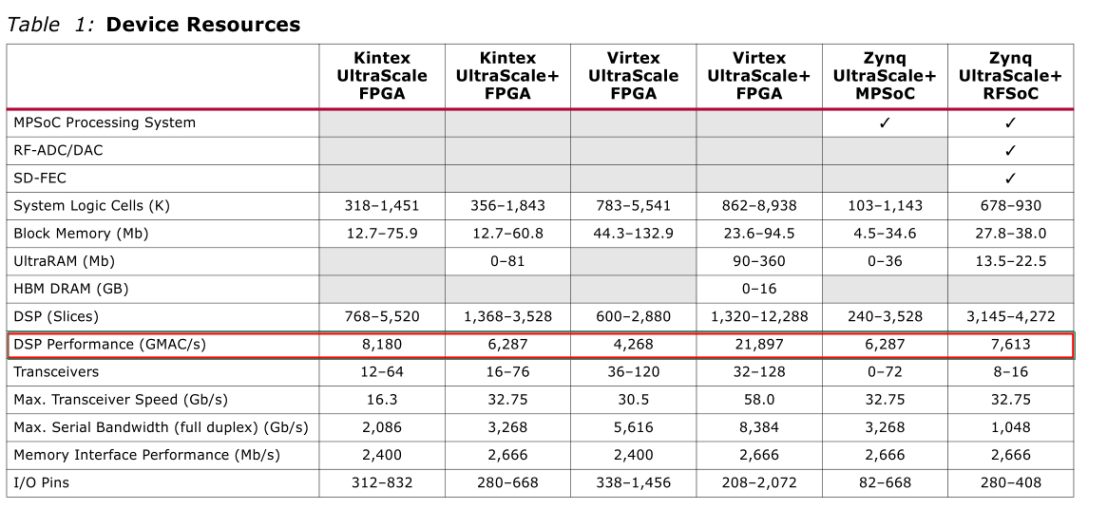

1.7 UltraScale Architecture DSP Slice ——DSP48E2

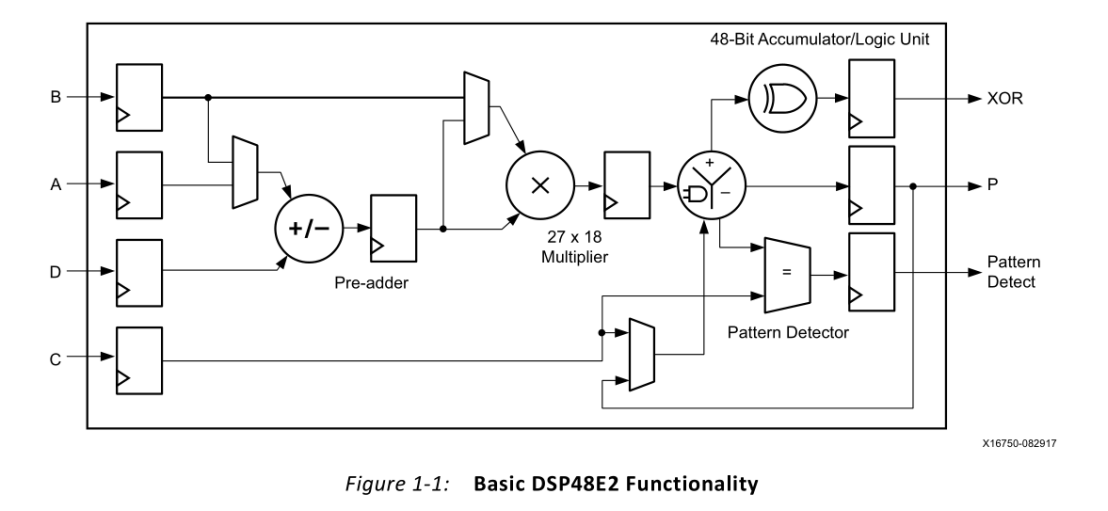

可编程逻辑器件可以实现定制的完全并行算法,因此对于数字信号处理(DSP)应用非常有效。 DSP应用程序使用许多二进制乘法器和累加器,最好在专用DSP资源中实现它们。 UltraScale器件具有许多专用的低功耗DSP Slice,在保持系统设计灵活性的同时,兼顾了高速与小尺寸。 DSP资源提高了数字信号处理之外的许多应用程序的速度和效率,例如宽动态总线移位器,存储器地址生成器,宽总线多路复用器和存储器映射的I / O寄存器。 UltraScale架构中的DSP Slice是使用DSP48E2原语定义的,在Xilinx工具中,该Slice被称为DSP或DSP48E2。 DSP48E2 slice的基本功能如图1-1所示。

![]()

与DSP48E1 slice相比,DSP48E2具有更广泛的功能:

乘法器宽度从DSP48E1中的25 x 18改进为DSP48E2中的27 x 18;

预加器从25位增加到27位:D输入和寄存器到预加法器增加到27位;预加器的AD寄存器结果增加到27位

预加器具有更大的灵活性:

可以选择A或B作为预加器的输入;

预加器的输出可以平方。

2.接触过的用到DSP48的IP核

2.接触过的用到DSP48的IP核

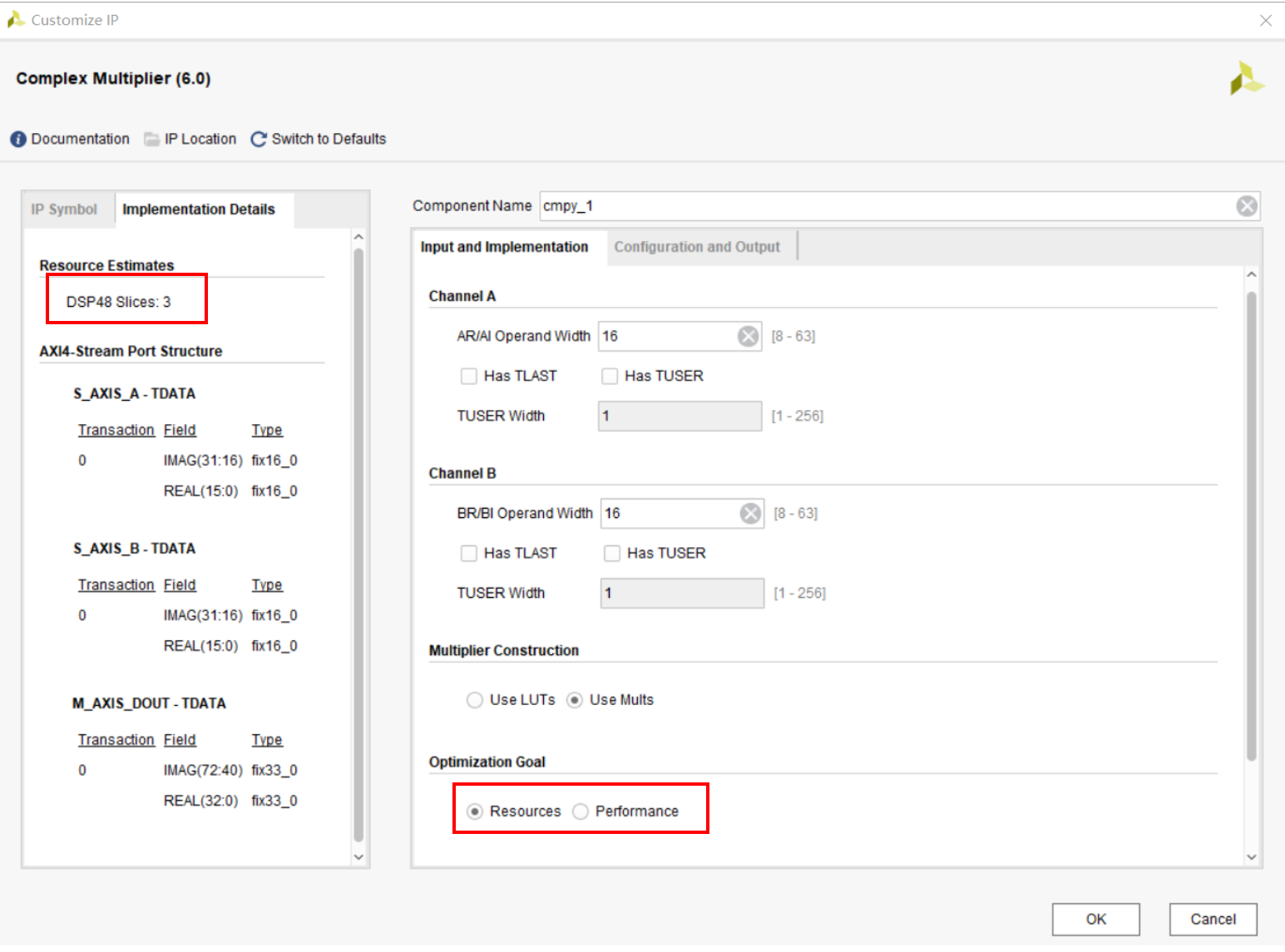

2.1 复数乘法器IP核

选resources时 ,用到的DSP48 Slices是3个,输出延时为6个CLK。选performance时,用到的DSP48 Slices是4个,输出延时为4个CLK。

Resources和performance是一对矛盾的统一体。

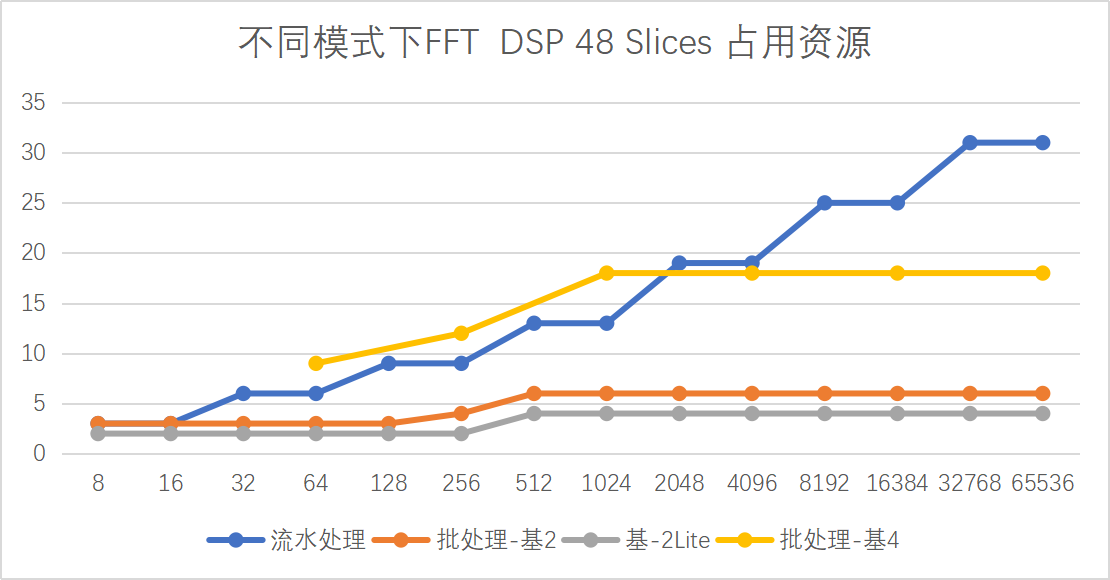

2.2 FFT IP核

- 同FFT点数(64~65536)下流水处理占用的DSP48最多,

- 1024点之后,随着点数增加,基2基4所用DSP48不再增加,流水处理所用DSP48随点数增加而增加。

最后

以上就是腼腆战斗机最近收集整理的关于FPGA 乘法器 (DSP48)总结0.参考手册1.DSP48总结2.接触过的用到DSP48的IP核的全部内容,更多相关FPGA内容请搜索靠谱客的其他文章。

发表评论 取消回复