一、概述

本文基于上一篇文章设计的频率调制(frequency modulation,FM,简称调频)工程进行 Testbench 仿真验证。

二、Testbench 代码

测试程序很简单,我们只需要给出一个 1 MHz 的时钟,并将相位控制字参数(Phase Offset Programmability,相位偏移可编程性)配置给例化好的 FM 调制解调顶层即可。

这里的相位控制字参数的计算公式可以通过 Xilinx DDS IP 核的用户手册(DDS Compiler v6.0 LogiCORE IP Product Guide)中查到,它可以表示为:

其中, 表示相位累加器位宽,

表示载波频率。在本工程中,我们设置的相位累加器位宽是 16 比特,载波频率是 0.1 MHz,因此可以计算出相位控制字为 6554。

`timescale 1ns / 100ps

//

// Company: UESTC

// Engineer: chylinne

//

// Create Date: 2022/08/15 14:22:38

// Design Name: fm

// Module Name: fm_tb

// Project Name: fm

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module fm_tb();

reg rst_n;

reg clk;

parameter CLK_PERIOD = 'd1000; //1MHz

initial begin

clk <= 1'b0;

rst_n <= 1'b0;

#(10 * CLK_PERIOD)

rst_n <= 1'b1;

end

always #(CLK_PERIOD/2) clk = ~clk;

/* Phase Offset Programmability

poff = 2^N * f_carrier

= 2^16 * 100 kHz

= 2^16 * 0.1 MHz

= 6554

*/

fm_top # (

.POFF('d6554)

) u_fm_top (

.clk(clk),

.rst_n(rst_n)

);

endmodule三、结果分析

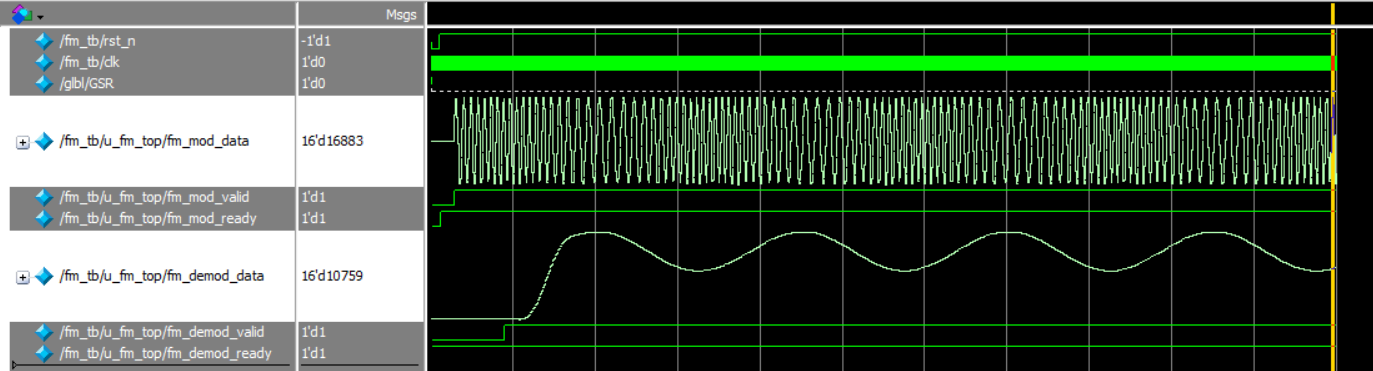

运行 Testbench 程序后,我们能得到下图波形数据。图中,fm_mod_data 是 FM 已调信号,我们能看到明显的疏密间隔;fm_demod_data 是解调后的信号(即原始消息信号),我们能明显观察到它的波形和上方的 FM 已调信号的疏密程度是一一对应的,说明了解调的正确性。

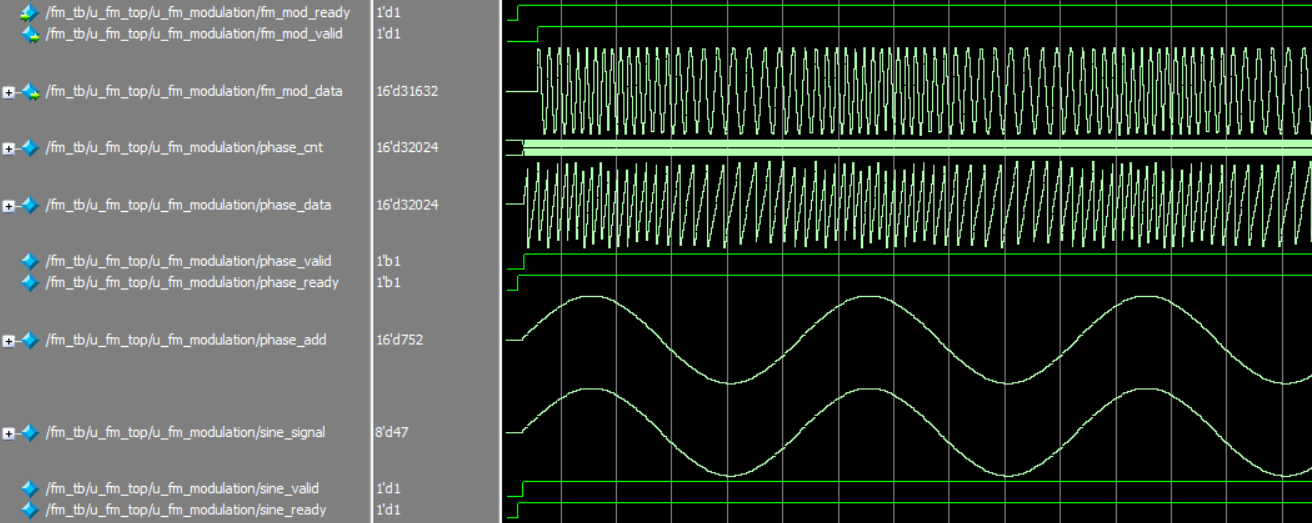

然后,我们可以观察一下内部的信号。下图所示为 FM 调制模块的内部信号波形。

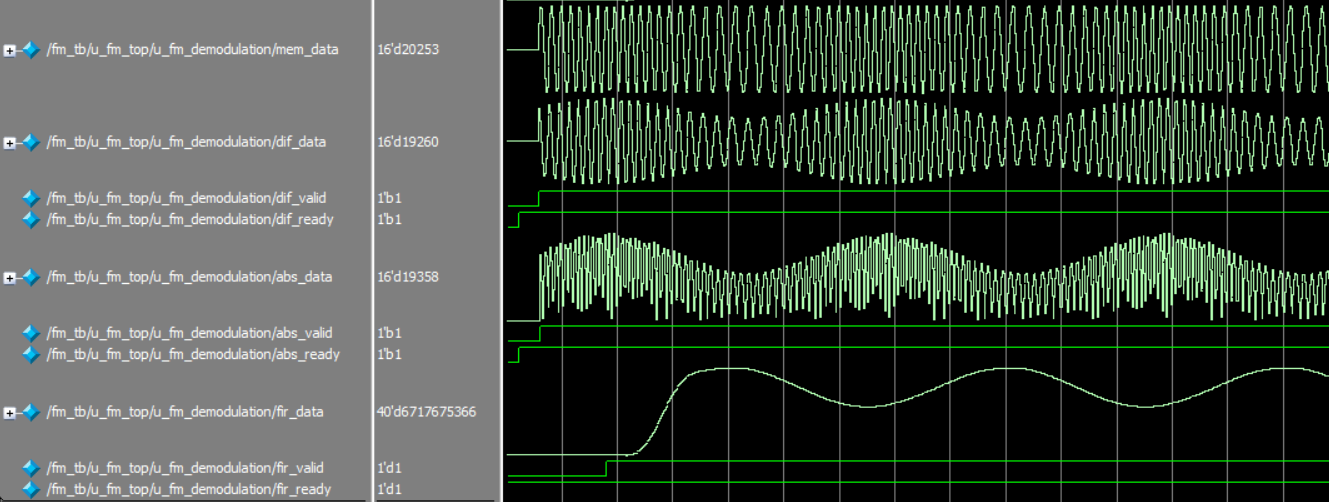

下图所示为 FM 解调模块的内部信号波形。

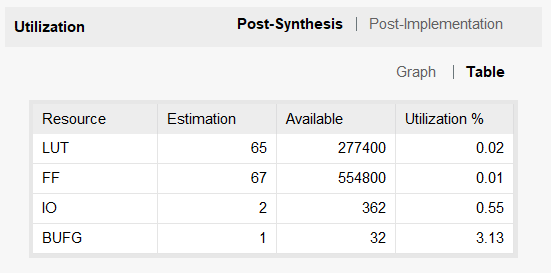

附录 VIVADO 综合布线 FPGA 资源使用情况

最后

以上就是甜蜜小猫咪最近收集整理的关于基于 VIVADO 的 FM 调制解调(下)测试篇的全部内容,更多相关基于内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复