文章目录

- Analog Subsystem模拟子系统

- 12.1 Introduction简介

- 12.1.1 Features特性

- 12.1.2 Block Diagram 系统方框图

- 12.2 Optimizing Power-Up 优化供电使能时间

- 12.3 Digital Input on ADC Pins ADC引脚上的数字输入(AIO)

- 12.4 Digital Inputs and Outputs on ADC Pins ADC引脚上的数字输入和输出(AGPIO)

- 12.5 Essential Information

- 总结

Analog Subsystem模拟子系统

Analog Subsystem是F280049C上的唯一模拟系统,理解该模块有助于后续ADC,PGA,DAC以及CMPSS模块的学习。

12.1 Introduction简介

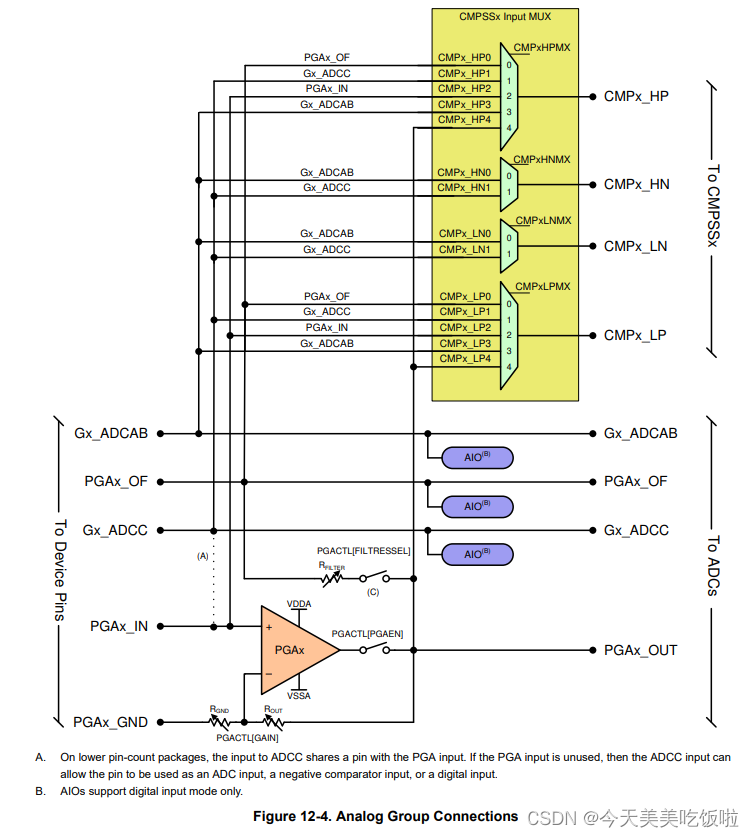

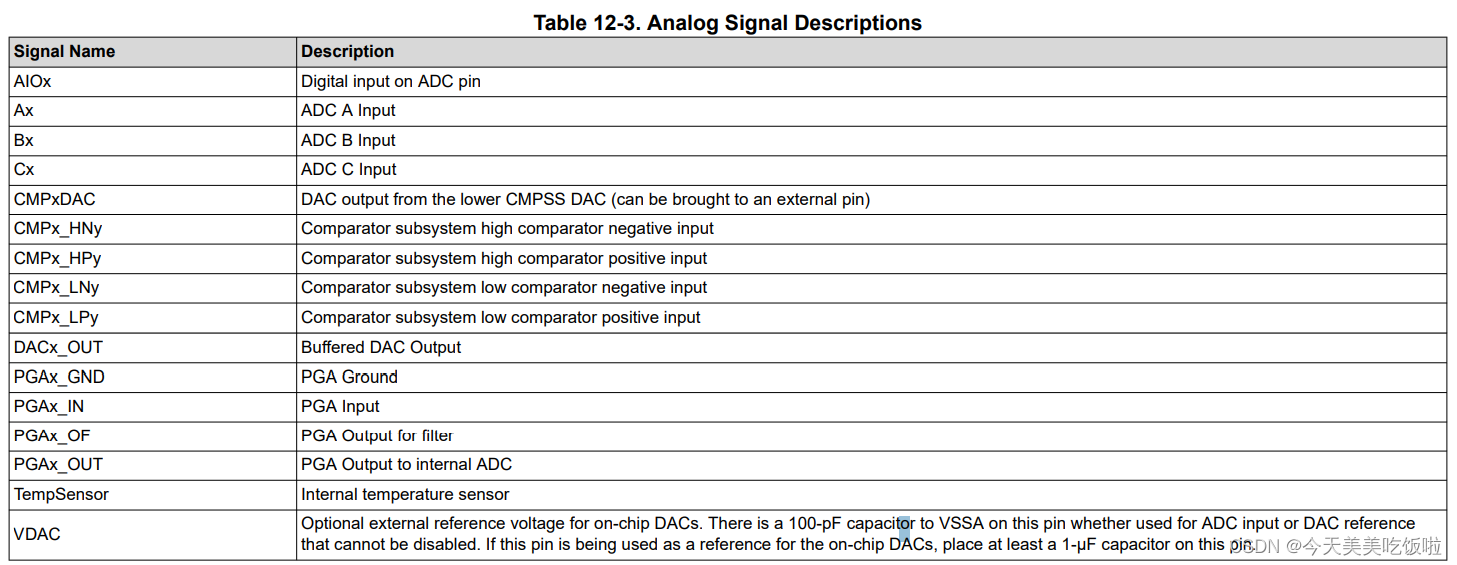

该设备上的模拟模块包括模数转换器(ADC)、可编程增益放大器(PGA)、温度传感器、缓冲数模转换器(DAC)和比较器子系统(CMPSS)

12.1.1 Features特性

该模块具有如下几个特点:

- 灵活的电压参考

- ADC参考VREFHIx和VSSA引脚

- VREFHIx引脚电压可以由外部驱动,也可以由内部带隙电压参考生成

- 内部电压参考范围可以选择为0V至3.3 V或0V至2.5V

- 缓冲DAC参考VREFHIC和VSSA

- 或者,这些DAC可以参考VDAC引脚和VSSA

- 比较器DAC参考VDDA和VSSA

- 或者,这些DAC可以引用VDAC引脚或VSSA•

- ADC参考VREFHIx和VSSA引脚

- 灵活的引脚使用

- 缓冲DAC输出、比较器子系统输入、PGA功能、,数字输入与ADC输入复用

- 所有ADC上VREFLO的内部连接,用于偏移自校准

12.1.2 Block Diagram 系统方框图

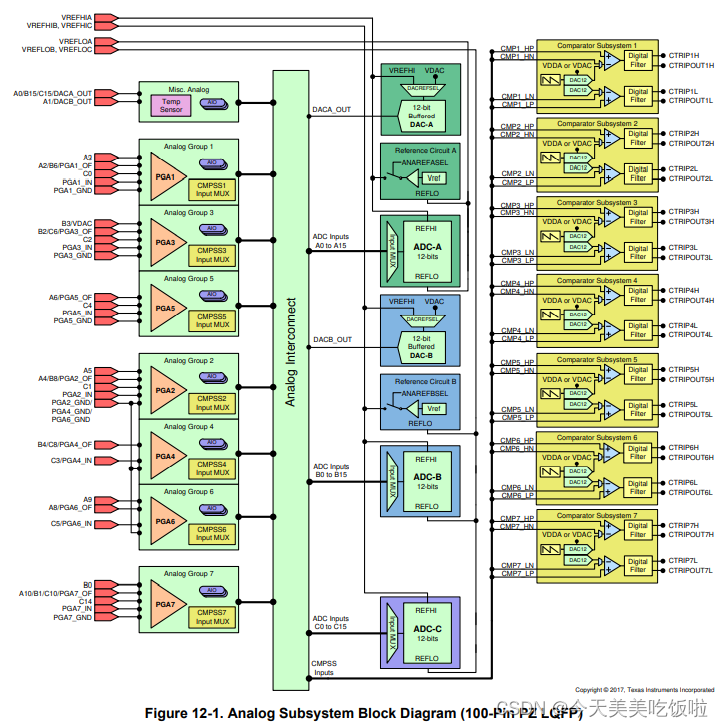

以下模拟子系统框图显示了不同集成模拟模块与设备引脚之间的连接。这些引脚分为两类:模拟模块输入/输出和参考引脚。

模拟引脚围绕PGA和CMPSS模块组织成模拟组。框图显示了哪些引脚连接到每组,但没有显示从引脚到ADC、DAC、CMPSS或PGA模块的特定连接。

VDAC参考引脚可用于设置DAC A、DAC B和CMPSS模块内DAC的替代范围(默认情况下,CMPSS DAC参考VDDA和VSSA)。使用此引脚作为参考可防止通道用作ADC输入(但如果需要,ADC可用于采样VDAC电压)。每个CMPSS或缓冲DAC的参考选择可按模块进行配置,并使用模块的配置寄存器进行选择。

以下注释适用于所有的封装:

- 并非所有设备上都有模拟引脚。请参阅设备数据手册以确定哪些引脚可用。 •请参阅设备数据手册,以确定VREFHI和VREFLO的允许电压范围。

- VREFHI引脚上需要一个外部电容器。有关所需的具体值,请参阅设备数据手册。

- 对于缓冲DAC模块,无论选择VREFHIx或VDAC作为高参考,VSSA都是低参考。

- 对于CMPSS模块,无论选择VDAC或VDDA作为高参考,VSSA都是低参考。

12.2 Optimizing Power-Up 优化供电使能时间

模数转换器(ADC)和缓冲数模转换器(DAC)共用参考电路。如果需要,使用这些模块中的一个或多个的应用程序可以利用共享引用优化通电时间。一旦在内部参考模式中初始化了使用共享参考的模块之一,可以通过从最小通电时间要求中减去参考通电时间来优化后续模块的通电时间。

12.3 Digital Input on ADC Pins ADC引脚上的数字输入(AIO)

端口H上的GPIO(GPIO224–GPIO253)与模拟引脚复用。这些也被称为AIO。这些引脚只能在输入模式下工作。默认情况下,这些引脚用作模拟引脚,GPIO处于高阻抗状态。GPHAMSEL寄存器用于为数字或模拟操作配置这些引脚。

12.4 Digital Inputs and Outputs on ADC Pins ADC引脚上的数字输入和输出(AGPIO)

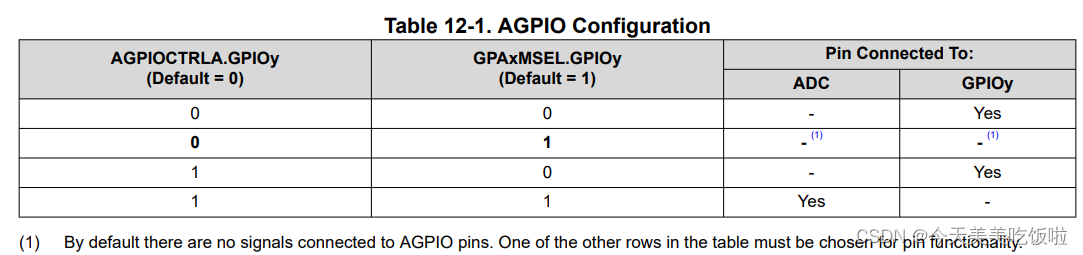

该设备上的一些GPIO与模拟引脚复用。这些也被称为AGPIO。与AIO不同,AGPIO具有完全的输入和输出能力。

默认情况下,AGPIO未连接,必须进行配置。

12.5 Essential Information

总结

感觉这一节就是连接前后的数模系统的,没什么重要的干货

最后

以上就是执着西装最近收集整理的关于F280049C Analog SubsystemAnalog Subsystem模拟子系统总结的全部内容,更多相关F280049C内容请搜索靠谱客的其他文章。

发表评论 取消回复