思考1:同步和异步的定义及区别么?

当两个时钟信号间的相位差是固定的时候,则称为同步时钟;当两个时钟信号间的相位差无法固定的时候,则称为异步时钟。

思考2:为什么要异步FIFO?

前面我们使用同步时钟设计了FIFO,读写操作都是受控与同一个时钟clk,但在实际IC设计中,不同信号间的传输是受控于不同的时钟信号的。所以对于跨时钟域的信号传输则要进行“同步”处理。

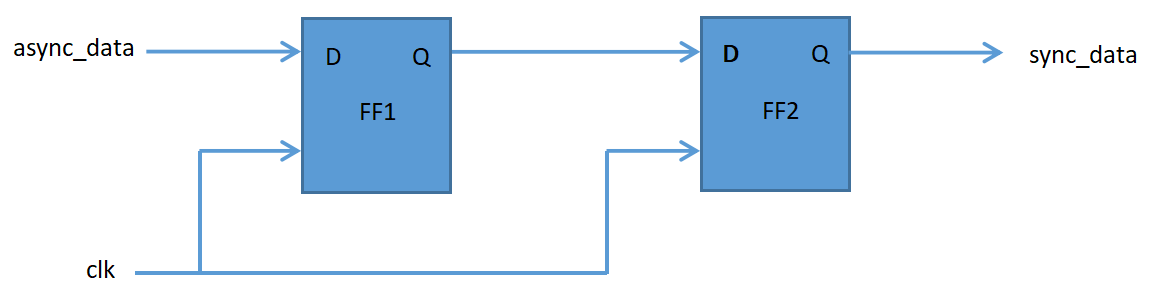

思考3:单bit怎么做同步处理?

对于单bit信号的同步操作——采用“同步器”操作,由2~3级FF组成(2到3级的触发器,作delay效果),它第一级采集到的数据无法确定是0或是1,但输出肯定是有定值了,第二级触发器再采的时候肯定可以采集到一个确定的值。

图1 电路结构图

最后

以上就是简单路人最近收集整理的关于(3)异步FIFO设计及仿真验证(上)的全部内容,更多相关(3)异步FIFO设计及仿真验证(上)内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

![[UVM]UVM TLM FIFO使用方法總結 UVM TLM FIFO用法總結](https://www.shuijiaxian.com/files_image/reation/bcimg26.png)

发表评论 取消回复