我是靠谱客的博主 内向香氛,这篇文章主要介绍Xilin常用原语(primitive)之IO ComponentsXilin常用原语(primitive)1.IO Component,现在分享给大家,希望可以做个参考。

Xilin常用原语(primitive)

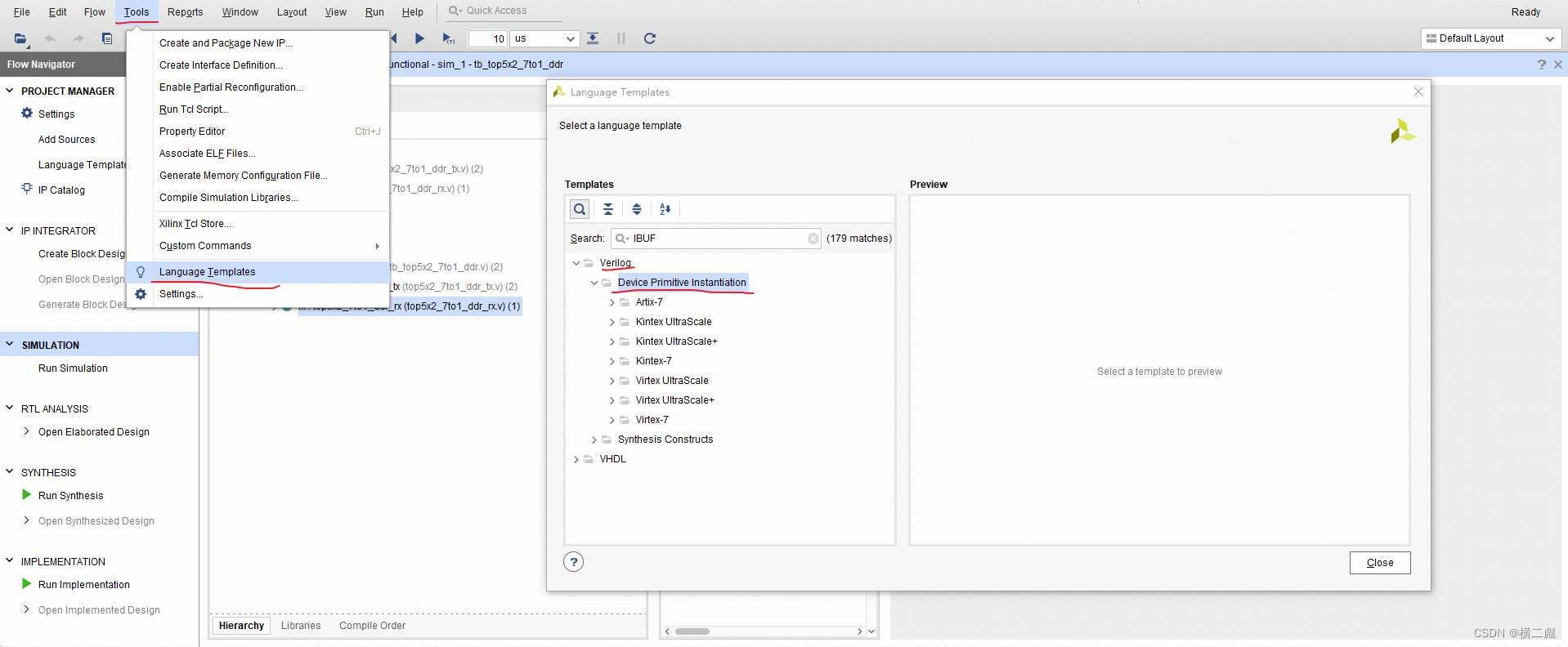

Xilinx所有原语例化模板均可在Vivado中Tools-Language Templates中找到。如下图

1.IO Component

1.1 IBUF

1.1.1 作用

IBUF是输入缓存,一般vivado会自动给输入信号加上.所有从全局时钟管脚输入的信号必须经过IBUF,否则在布局布线时会报错。

1.1.2 端口列表

1.1.3例化模板

(以K7系列FPGA为例)

// IBUF: Single-ended Input Buffer

// Kintex-7

// Xilinx HDL Language Template, version 2018.2

IBUF #(

.IBUF_LOW_PWR("TRUE"), // Low power (TRUE) vs. performance (FALSE) setting for referenced I/O standards

.IOSTANDARD("DEFAULT") // Specify the input I/O standard

) IBUF_inst (

.O(O), // Buffer output

.I(I) // Buffer input (connect directly to top-level port)

);

1.2 IDELAYCTRL

1.2.1 作用

在电压、温度等因素变化时,可能会影响到系统的时序,此时IDELAYCTRL模块就可以连续补偿时钟域内所有个体的delay taps (IDELAY/ODELAY)。如果使用了IOB上的IDELAY或ODELAY资源,那么就必须使用IDELAYCTRL资源。请注意,整个IO BANK里面只有一个IDELAYCTRL。

IDELAYCTRL很重要的一个输入项就是参考时钟REFCLK,补偿时钟域内所有模块的时序参考,这个时钟必须由BUFG或BUFH驱动。REFCLK必须保证在FIDELAYCTRL_REF+IDELAYCTRL_REF_PRECISION(MHz)ppm才能保证IDELAY/ODELAY的延时分辨率:

(TIDELAYRESOLUTION=1/(32x 2 x FREF))

参考原文链接:https://blog.csdn.net/haoxingheng/article/details/50320145

1.2.2 端口列表

1.2.3例化模板

(以K7系列FPGA为例)

// IDELAYCTRL: IDELAYE2/ODELAYE2 Tap Delay Value Control

// Kintex-7

// Xilinx HDL Language Template, version 2018.2

(* IODELAY_GROUP = <iodelay_group_name> *) // Specifies group name for associated IDELAYs/ODELAYs and IDELAYCTRL

IDELAYCTRL IDELAYCTRL_inst (

.RDY(RDY), // 1-bit output: Ready output

.REFCLK(REFCLK), // 1-bit input: Reference clock input

.RST(RST) // 1-bit input: Active high reset input

);

最后

以上就是内向香氛最近收集整理的关于Xilin常用原语(primitive)之IO ComponentsXilin常用原语(primitive)1.IO Component的全部内容,更多相关Xilin常用原语(primitive)之IO内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复