五 FIFO IP核

FIFO的完整英文拼写为First In First Out,即先进先出。FPGA或者ASIC中使用到的FIFO一般指的是对数据的存储具有先进先出特性的一个存储器,常被用于数据的缓存或者高速异步数据的交互。

FIFO结构

FIFO从大的情况来分,有两类结构:单时钟FIFO(SCFIFO)和双时钟FIFO(DCFIFO),其中双时钟FIFO又可以分为普通双时钟(DCFIFO)和混合宽度双时钟FIFO (DCFIFO_MIXED_WIDTHS)。三种FIFO结构的英文含义如下所示:

• SCFIFO: single-clock FIFO

• DCFIFO: dual-clock FIFO (supports same port widths for input and output data)

• DCFIFO_MIXED_WIDTHS: dual-clock FIFO (supports different port widths for input and output data)

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-f5dl7BpM-1613898302614)(C:UsersLiu JunyongAppDataRoamingTyporatypora-user-imagesimage-20201130144244446.png)]](https://www.shuijiaxian.com/files_image/20230507/20210221170606547.png)

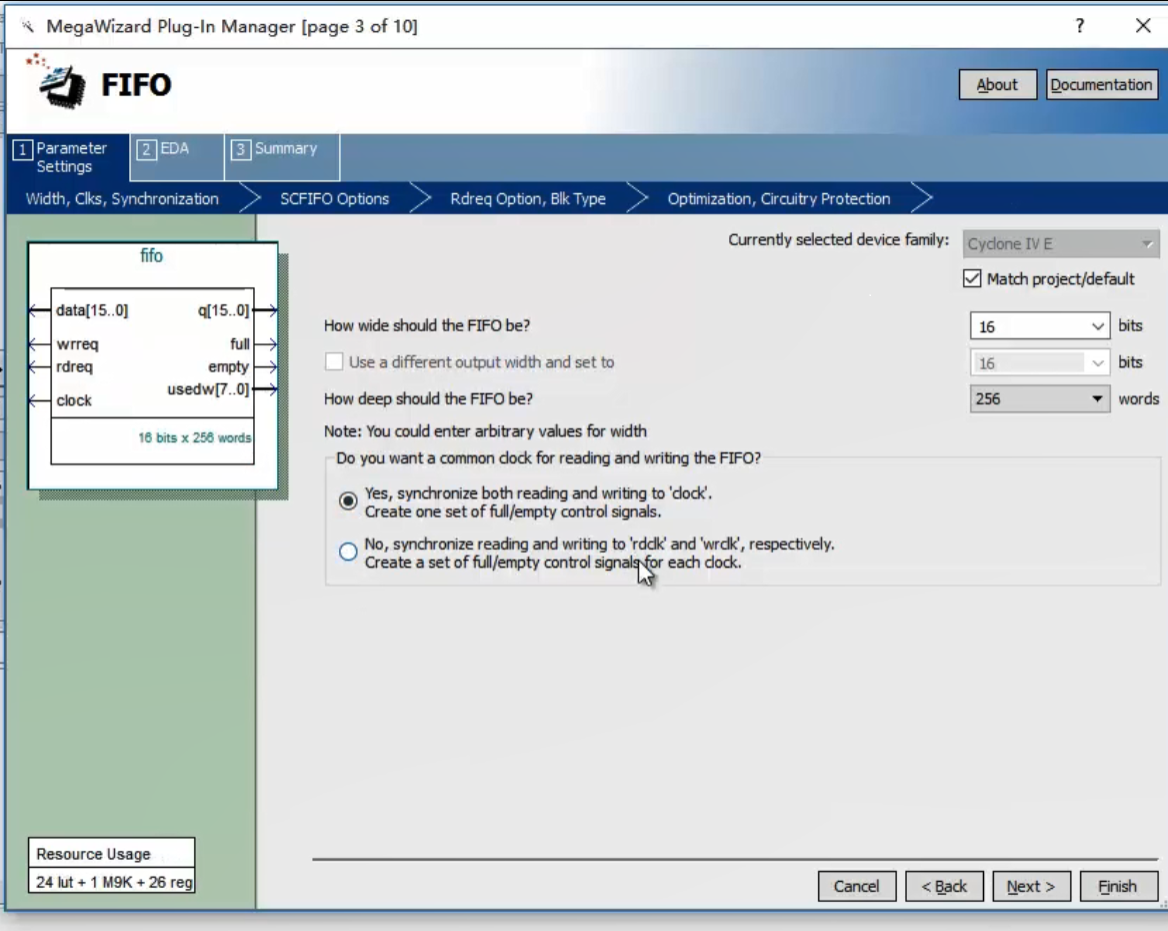

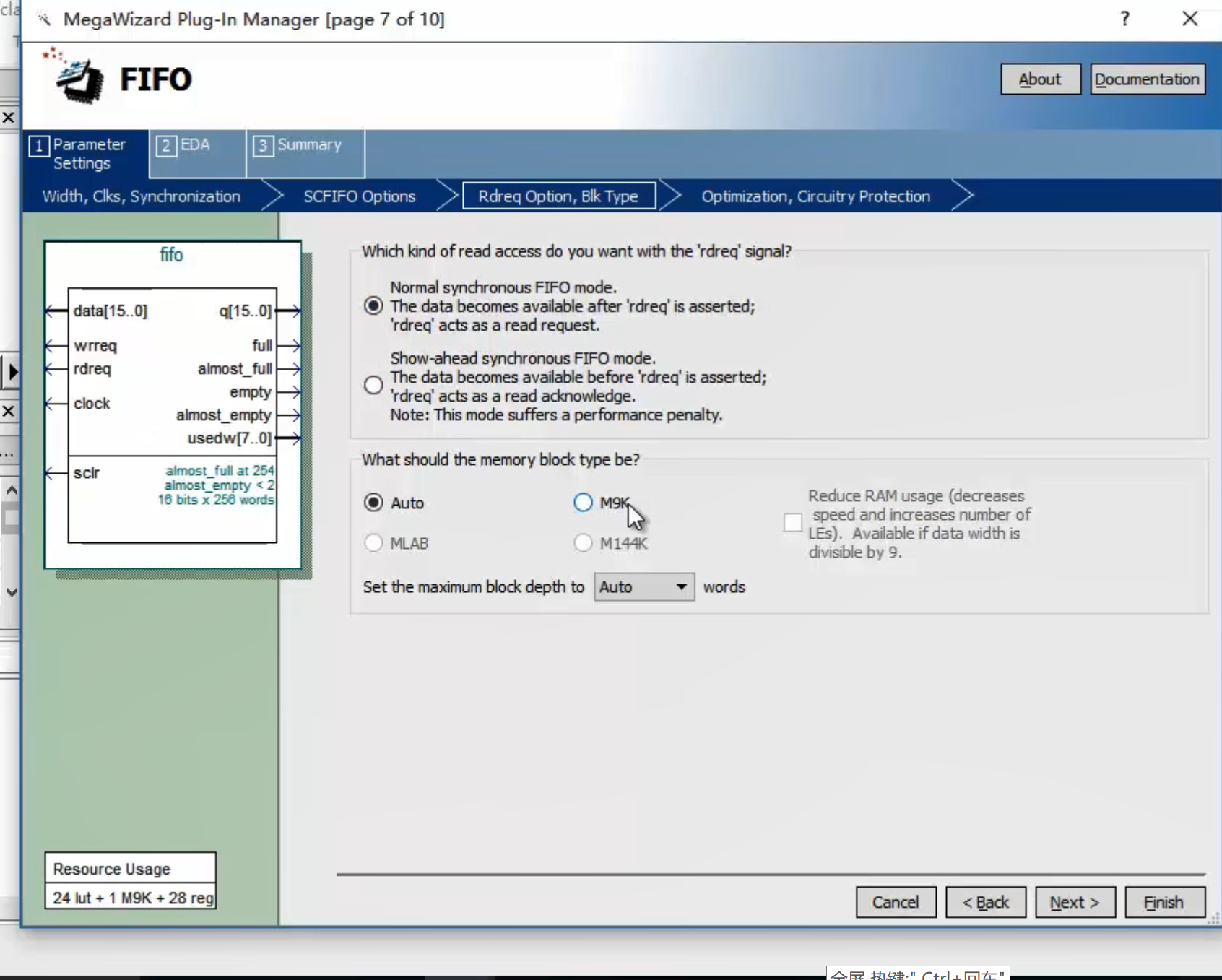

SCFIFO

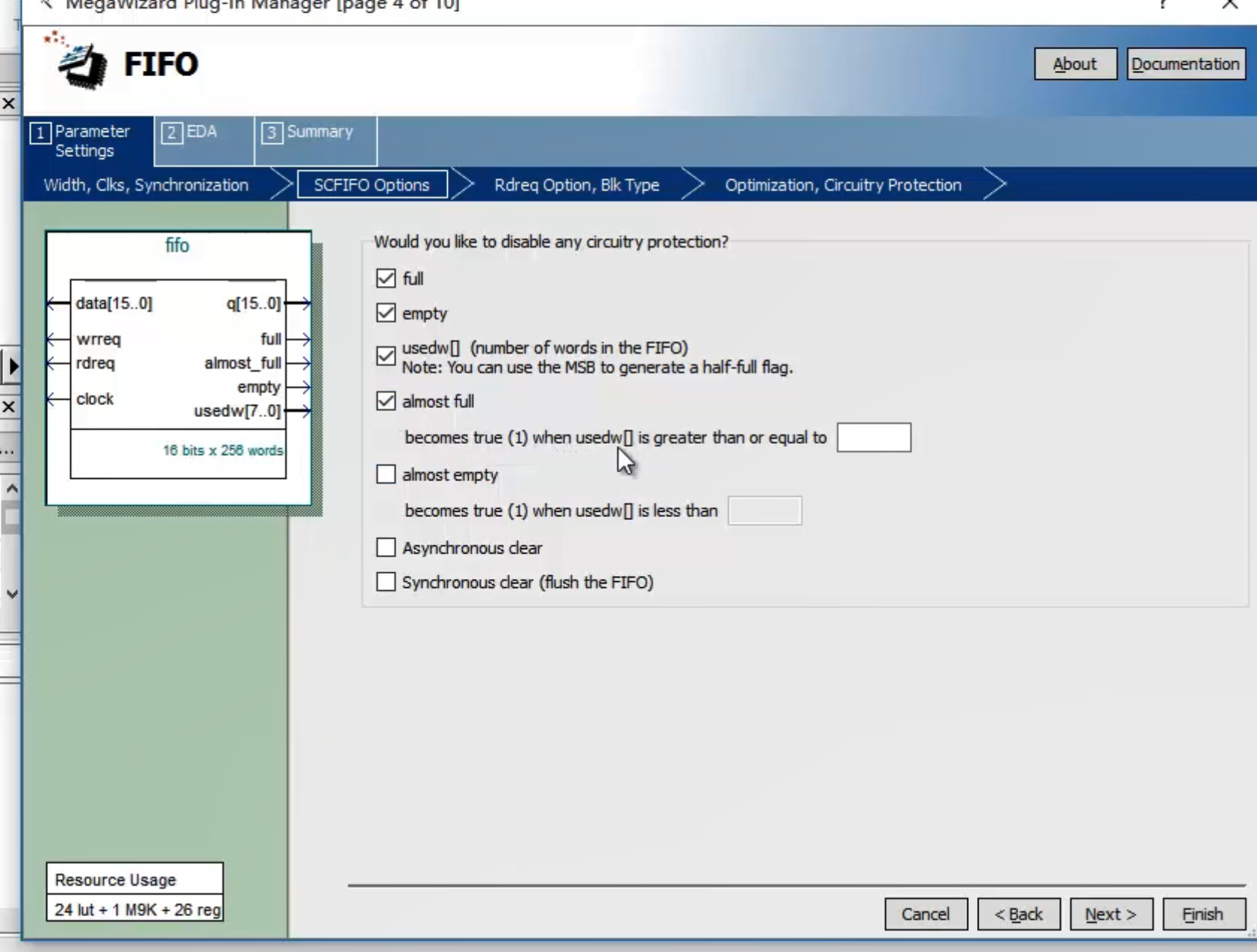

data[]要输入数据,wrreq写使能,rdreq使能读,clock时钟信号,q[]输出信号,full满信号,almost_full接近满信号,empty空信号,almost_empty接近空信号,usedw[]剩余多少数据,sclr同步清零,aclr异步清零

DCFIFO

data[]输入数据,wrreq写使能,wrclk写时钟,wrfull写满,wrempt写空,wusedw[]写入了多少数据,aclr异步时钟清零

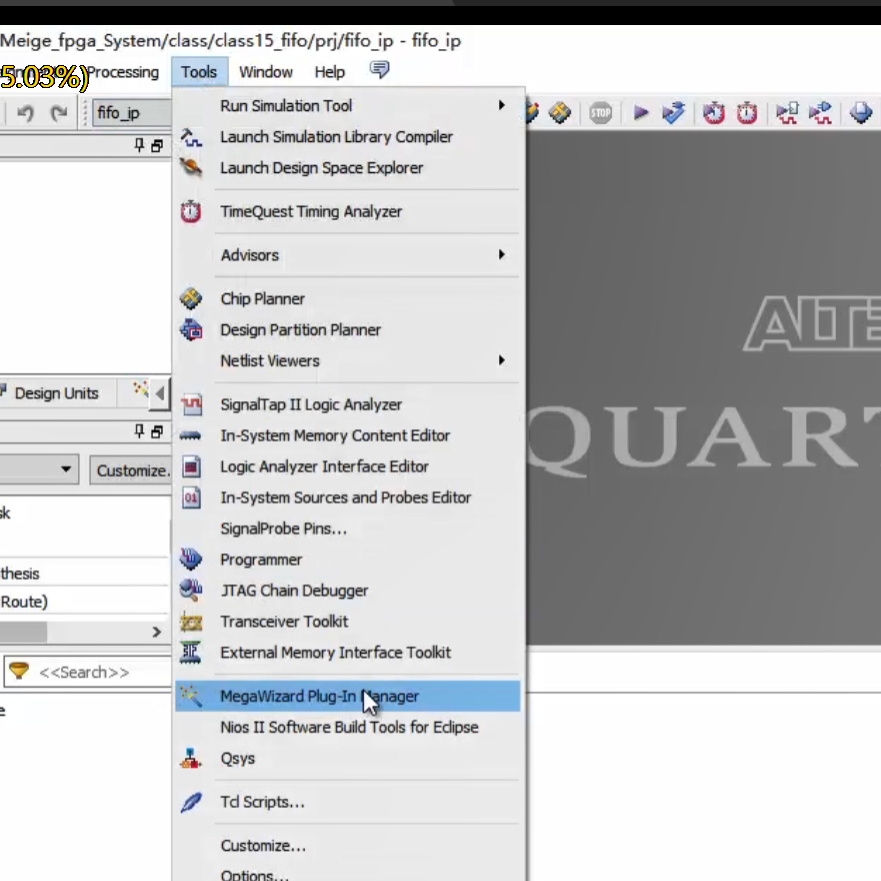

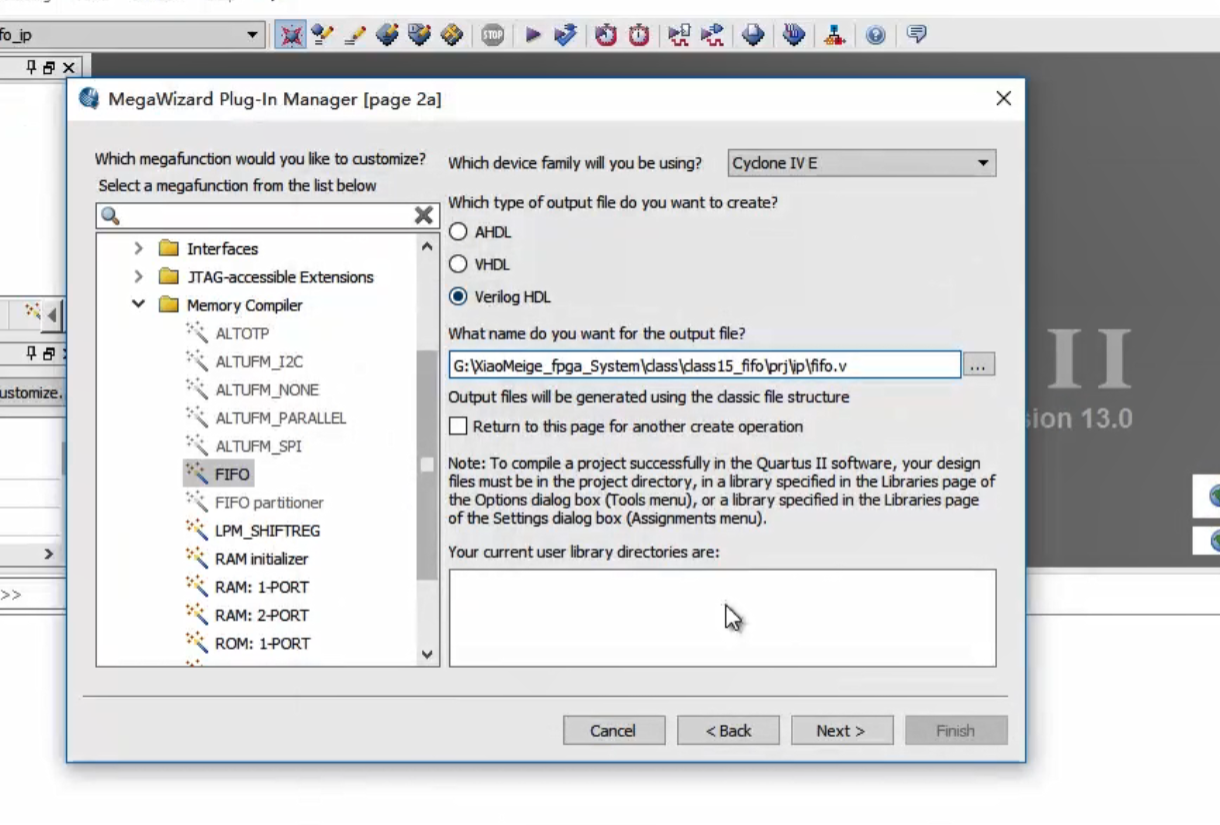

FIFO IP核 创建

记得放到ip文件夹下

16位宽,存256字节数据,下面是选择单/双端口。

可以添加或减少数据

上面普通模式需要手动激发,下面自动填充

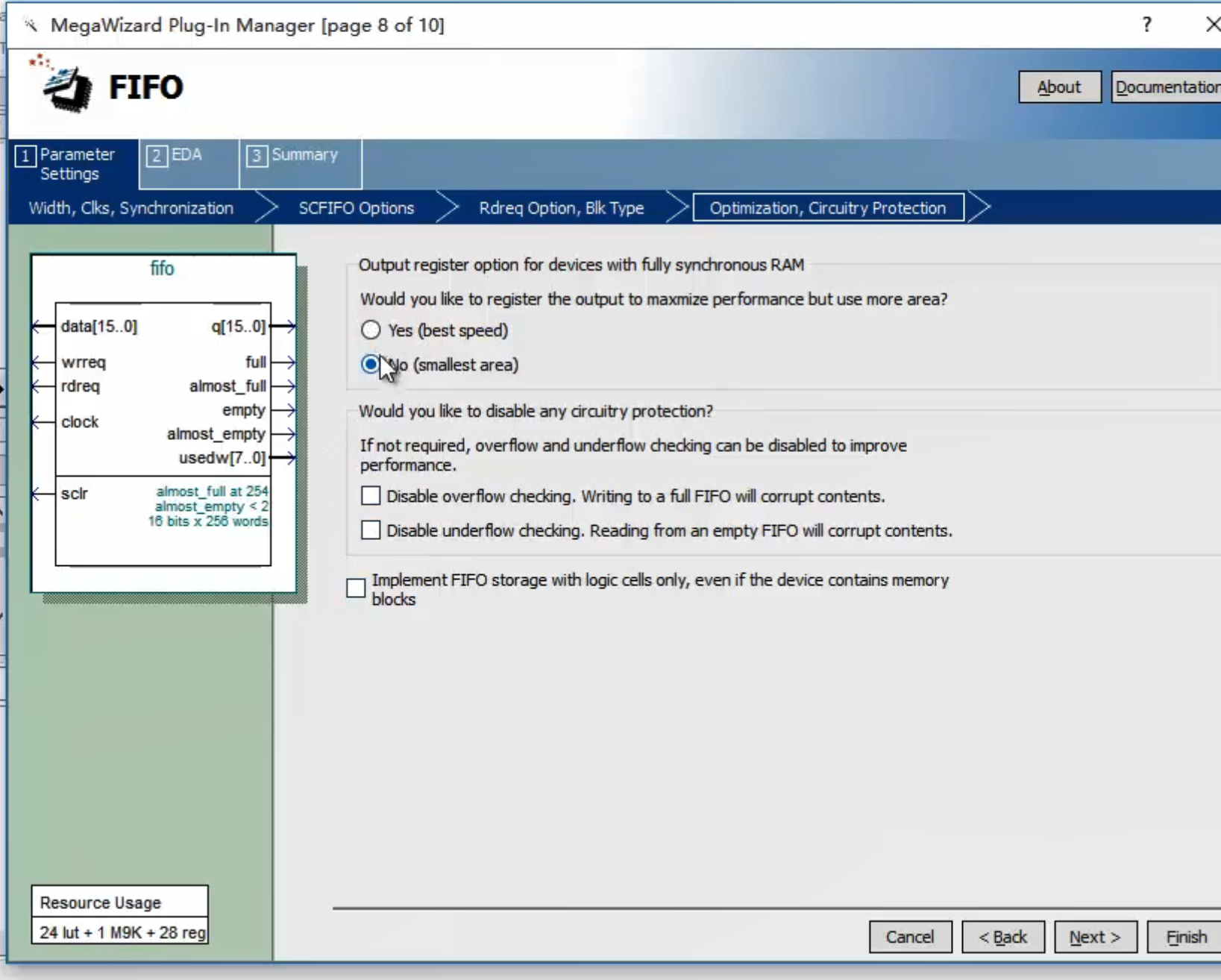

速度优先/面积优先

在系统中直接进行调用就行

最后

以上就是超级樱桃最近收集整理的关于FPGA学习---5.FIFO IP核的全部内容,更多相关FPGA学习---5.FIFO内容请搜索靠谱客的其他文章。

发表评论 取消回复