目录

眼图:

锁相环法位同步原理:

程序设计:

测试:

在现代通信系统中,位时钟同步技术即在通信码元中提取时钟信息,是精准判断通信数据的基础。例如在光通信发送端和接收端之间,时钟不会单独传送,只能从信号中提取(恢复),如果时钟有偏差,就会直接导致误码率的增大。在接收端进行位同步处理,对时钟纠偏,恢复同步时钟;据此作为最佳采样脉冲,对接收信号进行提取操作,能够准确地恢复原始发送数据。同步性能的好坏直接影响通信系统的性能。出现同步误差或失去同步,就会导致通信系统性能下降或通信中断。

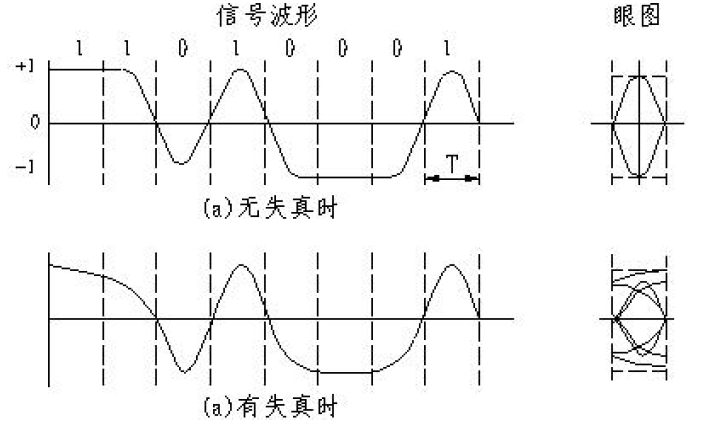

数字基带信号在有信道噪声的信道中进行传输,此时在接收端进行位同步,用示波器进行观测的时候产生的波形看起来像是一只眼睛,所以我们称之为眼图。

眼图:

在信号的传输过程中,无论是否会出现失真的现象,我们都可以在接收端通过一定的方法看到眼图。眼图是在数字信号经过低通滤波器之后借助示波器或者光谱仪等仪器观察到的。信号收到不一样的干扰的时候,眼图的形状也是不一样的。而且,不同进制的基带信号所观测到的眼图也是不一样的。

理论上,只要基带传输系统特性满足奈奎斯特准则,就可以实现无码间串扰的基带信号传输。但是在实际的传输系统中,要完全消除码间串扰是非常困难的。基带传输系统特性与发送滤波器特性、信道特性和接收滤波器特性及其他因素有关,如果各滤波器部件调试不理想或信道特性发生变化,都会引起基带传输系统特性的改变,此时不再满足奈奎斯特准则,就会产生码间串扰。同

时存在码间串扰和噪声的时候,我们很难对系统的性能进行定量分析,连近似结果往往也分析不出来。而眼图的作用就是对信号畸变做一个定性或者近似的分析。同时还能通过对眼图的分析得到最佳判决时间。

眼图的形成并不是一个二进制(M 进制)数据,而是由多个二进制数据叠加而成的。对于无失真的基带信号而言,由于他们的波形是重复的所以叠加在一起,看起来像一条线。如果信号在传输过程中受到了噪声的干扰,那么他们就是多条线,根据干扰越强线条的离散程度越大,干扰越差离散程度越小。

眼图是由虚线分段的接收码元波形叠加组成的。要做说明的是眼图是为了研究的方便而做的一种变化,是将多个时间段内的电平叠加在一起而成的。眼图并不是在现实中也真实存在的一种现象,因为在实际应用中,信号经过信道传输都是会受到噪声干扰和码间串扰的影响,所以我们观察到的眼图都是失真的眼图图像。为了便于说明和定义,现将由干扰的眼图抽象成下图所示:

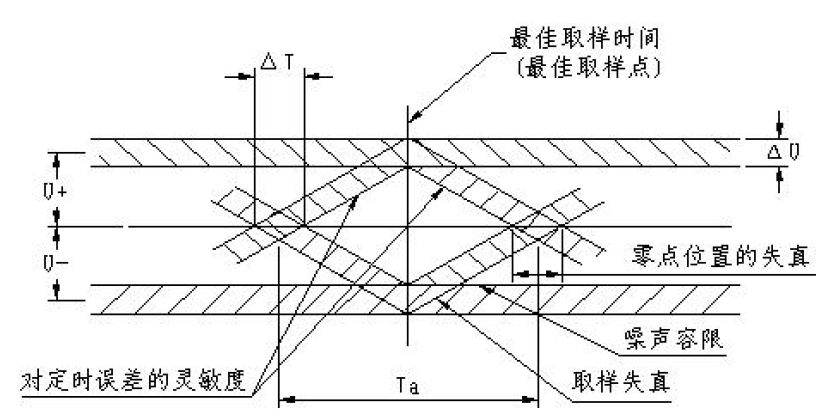

通过对眼图模型的分析,可得出以下结论:

(1)最佳抽样时刻应在“眼睛” 张开最大的时刻。

(2)对定时误差的灵敏度可由眼图斜边的斜率决定。斜率越大,对定时误差就越灵敏。

(3)在抽样时刻上,眼图上下两分支阴影区的垂直高度,表示最大信号畸变。

(4)眼图中央的横轴位置应对应判决门限电平。

(5)在抽样时刻上,上下两分支离门限最近的一根线迹至门限的距离表示各相应电平的噪声容限,噪声瞬时值超过它就可能发生错误判决。

(6)对于利用信号过零点取平均来得到定时信息的接收系统,眼图倾斜分支与横轴相交的区域的大小,表示零点位置的变动范围,这个变动范围的大小对提取定时信息有重要的影响。

锁相环法位同步原理:

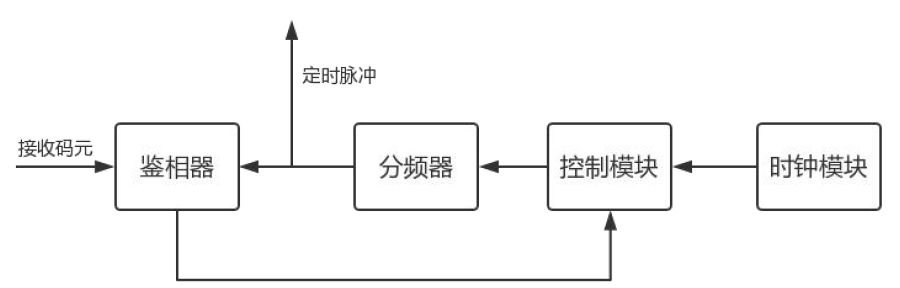

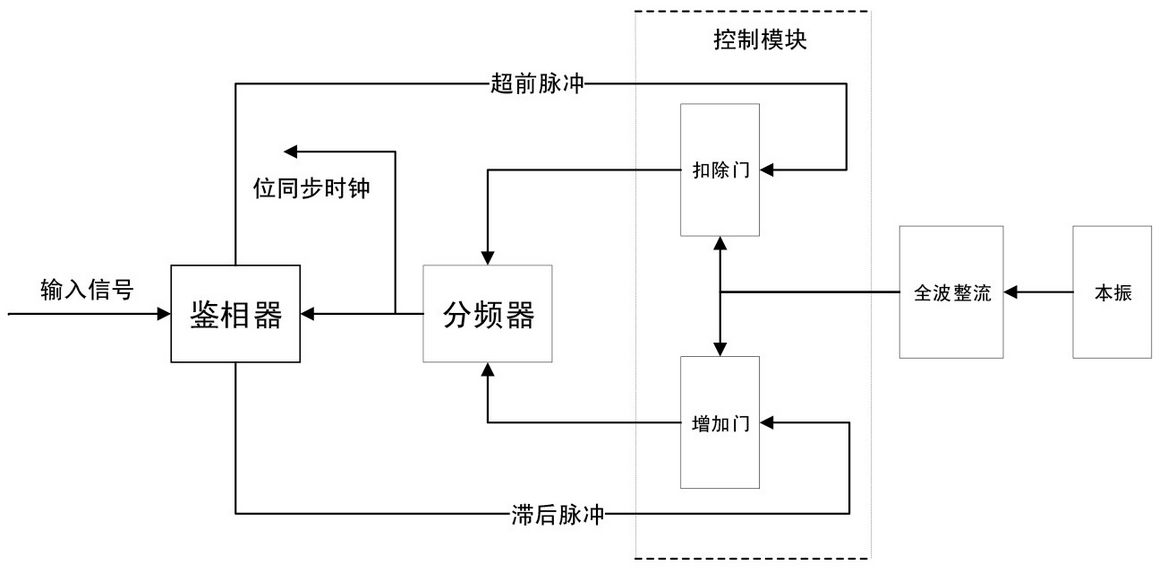

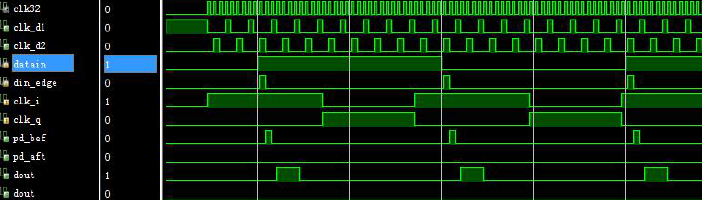

数字锁相环主要由鉴相器、控制分频器及时钟变换电路等部分组成。环路的输入信号是解调后的单比特码元序列。位同步时钟恢复设计方案的核心为三大模块,分别是双相时钟模块、微分鉴相模块和控制分频模块。

在位同步锁相环的设计中,接收端利用鉴相器对接收码元和本地产生的位同步信号的相位进行比较,若两者相位不一致(超前或滞后),鉴相器就产生误差信号去调整位同步信号的相位,通过不断的调整,直到获得准确的位同步信号为止。此时分频器的输出就是所恢复出的位同步定时脉冲。

当检测到输入数据码元的跳变沿时,作为鉴相功能的与门将输出一个高电平脉冲信号,根据输入数据与位同步信号的相位关系,或是在超前的与门输出脉冲信号,或是在滞后的与门输出脉冲信号,从而在控制器的控制作用改下实现在分频器输入信号上的加、扣脉冲操作。

控制分频模块用于完成附加、扣除脉冲的开、关门的与门功能和分频器输入信号的或门功能,以及分频信号的输出,该部分是本方案设计中的核心部分。该模块主要是通过对单稳态触发器的输出和双相时钟输出之间进行一定的与运算,对时钟脉冲进行附加和扣除,因为分频器是对时钟脉冲进行计数来产生本地时钟的。如果本地时钟超前于码元序列,则要使本地时钟的相位后移,因此扣除脉冲,反之则附加脉冲。

程序设计:

reg direct;

reg [CLK_CNT_MSB:0] clk_cnt;//分频器

always @(posedge clk_200M or negedge rst) begin

if(~rst)begin

。。。。。

。。。。

。。。

old_data <= datain ;

direct <= 1;

end else begin

old_data <= datain ;//一级寄存器缓,延迟200M的一个周期

difEdge <= datain ^ old_data ;

pre_Phase <= difEdge & I_clk ;

behind_Phase<= difEdge & Q_clk ;

pre_Phase_Stable<= pre_Phase ; //stable signal

behind_Phase_Stable<= behind_Phase ; //stable signal,稳定数据

if(pre_Phase_Stable)

to_adjust_pre_cnt <= to_adjust_pre_cnt+1 ;

if(behind_Phase_Stable)

to_adjust_behind_cnt<= to_adjust_behind_cnt+1 ;

if(pre_Phase_Stable | behind_Phase_Stable)

to_adjust_cnt <= to_adjust_cnt+1 ;

if( to_adjust_cnt >= CLEAR_CNT ) begin //Not to Adjust Phase

to_adjust_pre_cnt <= 0 ;

to_adjust_behind_cnt<= 0 ;

to_adjust_cnt <= 0 ;

clk_cnt <= clk_cnt+1;

end else //Adjust Phase

if( to_adjust_pre_cnt >= PRE_CNT_LIMIT )begin

clk_cnt <= clk_cnt;

to_adjust_pre_cnt <= 0 ;

to_adjust_behind_cnt <= 0 ;

to_adjust_cnt <= 0 ;

end else if( to_adjust_behind_cnt >= BEHIND_CNT_LIMIT )begin

clk_cnt <= clk_cnt+2;

to_adjust_pre_cnt <= 0 ;

to_adjust_behind_cnt<= 0 ;

to_adjust_cnt <= 0 ;

end else begin

clk_cnt <= clk_cnt+1;

end

I_clk <= clk_cnt[CLK_CNT_MSB];

Q_clk <= ~clk_cnt[CLK_CNT_MSB];//产生IQ两路时钟

//判断是上升沿对齐还是下降沿对齐

//延时两位

difEdge_reg[2] <= difEdge_reg[1] ;

difEdge_reg[1] <= difEdge_reg[0] ;

difEdge_reg[0] <= difEdge ;

if( difEdge_reg[2] )begin

if(I_clk)

direct <= 1;

else

direct <= 0;

end

//若是下降沿对齐,则翻转

if( direct )begin

I_clk_out <= clk_cnt[CLK_CNT_MSB];

Q_clk_out <= ~clk_cnt[CLK_CNT_MSB];

end else begin

I_clk_out <= ~clk_cnt[CLK_CNT_MSB];

Q_clk_out <= clk_cnt[CLK_CNT_MSB];

end

dataout <= old_data;

end

end

测试:

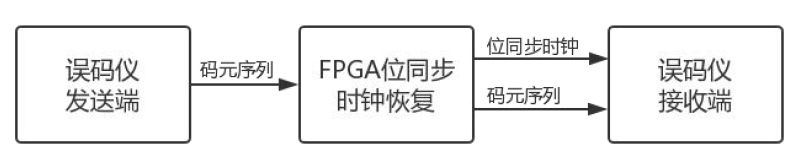

测试框图:

CDR采样时钟为数据比特率的10倍

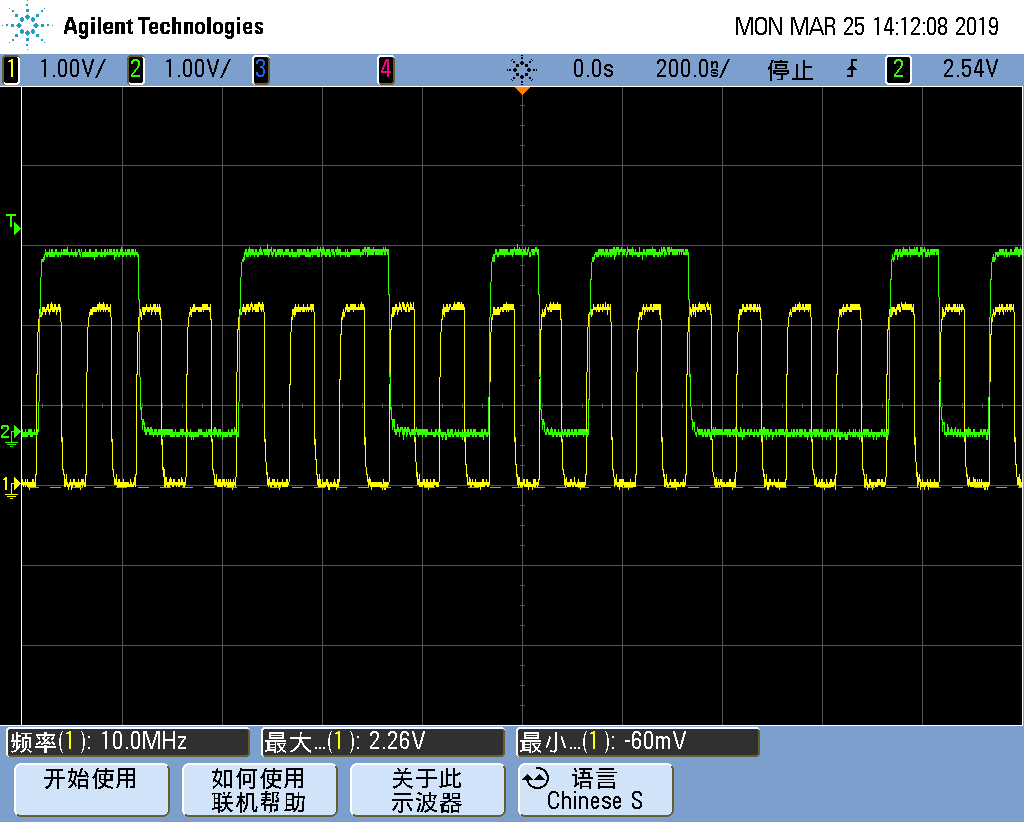

1、10Mbit输入,采样系统时钟100MHz 误码仪测试误码率为0;

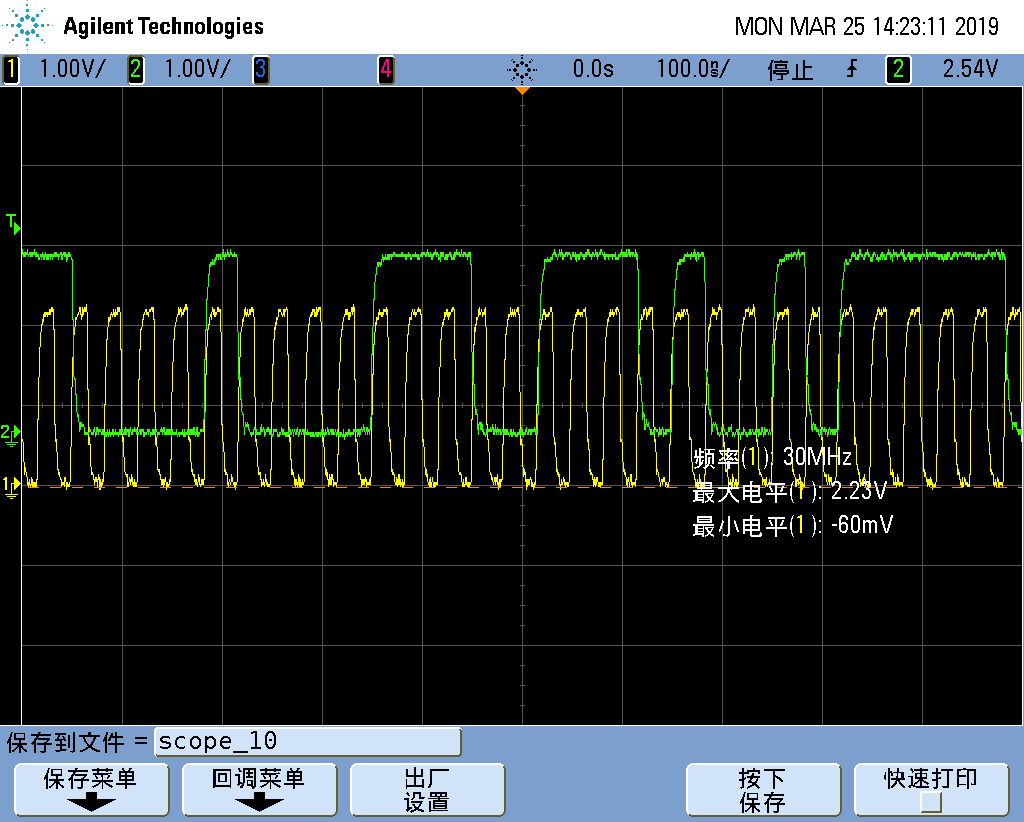

2、30Mbit输入,采样系统时钟300MHz 误码仪测试误码率为0;

最后

以上就是长情裙子最近收集整理的关于NRZ码位同步原理及FPGA实现--CDR的全部内容,更多相关NRZ码位同步原理及FPGA实现--CDR内容请搜索靠谱客的其他文章。

发表评论 取消回复