文章目录

- 功耗的分类

- 系统架构级低功耗设计

- 二、RTL级低功耗设计

- 门级

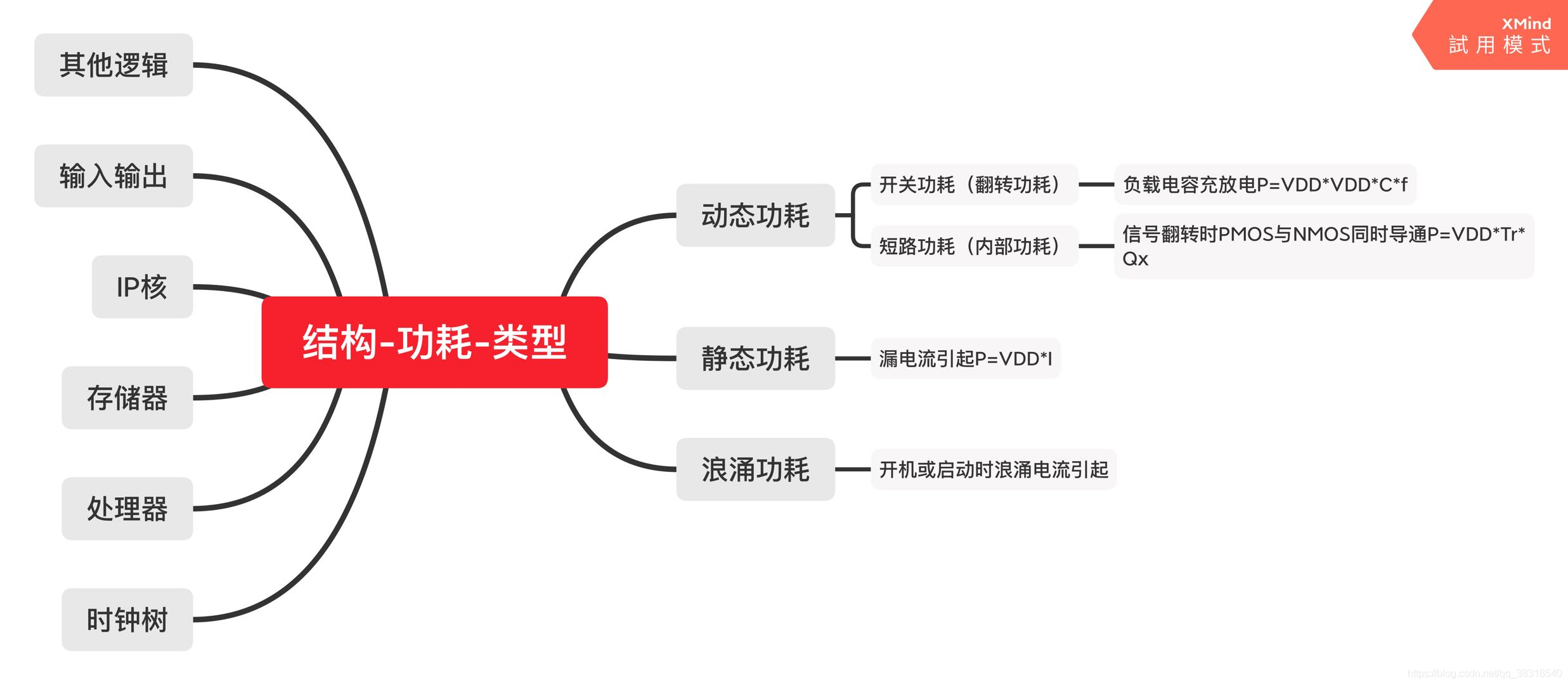

功耗的分类

三个主要的功耗源:浪涌、静态功耗和动态功耗;

其中浪涌电流指器件上电时产生的最大瞬时输入电流;浪涌电流与设备相关,不关注

1. 动态功耗包括:开关功耗(翻转功耗)

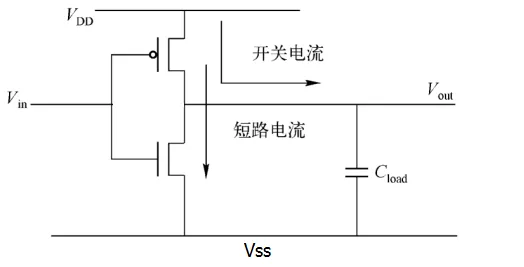

在数字CMOS电路中,对负载电容进行充放电时消耗的功耗,比如对于下面的CMOS非门中:

当Vin = 0时,上面的PMOS导通,下面的NMOS截止;VDD对负载电容Cload进行充电,充电完成后,Vout的电平为高电平。

当Vin = 1时,上面的PMOS截止,下面的NMOS导通,负载电容通过NMOS进行放电,放电完成后,Vout的电平为低电平。

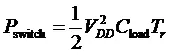

这样一开一闭的变化,电源的充放电,就形成了开关功耗,开关功耗Psitch的计算公式

在上式中,VDD为供电电压,Cload为后级电路等效的电容负载大小,Tr为输入信号的翻转率

一般情况下,信号在一个周期内平均翻转两次,即上升沿一次、下降沿一次,也就是说,Tr = 2f,因此,平均功耗就是:

Pdynamic = Vdd^2 * C * f

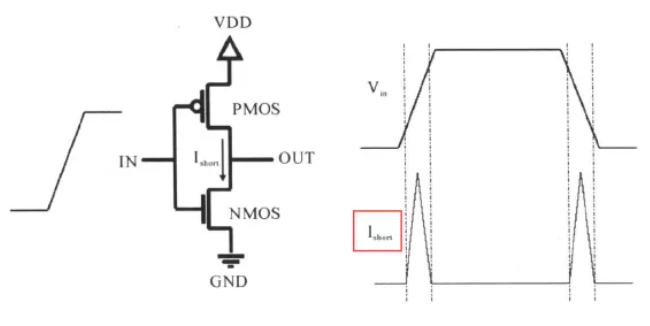

短路功耗。

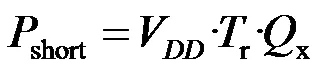

短路功耗也称为内部功耗,短路功耗是因为在**输入信号进行翻转时,信号的翻转不可能瞬时完成,**因此PMOS和NMOS不可能总是一个截止另外一个导通,总有那么一段时间是使PMOS和NMOS同时导通,那么从电源VDD到地VSS之间就有了通路,就形成了短路电流,如下面的反相器电路图所示:

上式中,Vdd为供电电压,Tr为翻转率,Qx为一次翻转过程中从电源流到地的电荷量。

动态功耗主要跟电源的供电电压、信号翻转率、时钟频率、负载等效电容有关。

(2)静态功耗

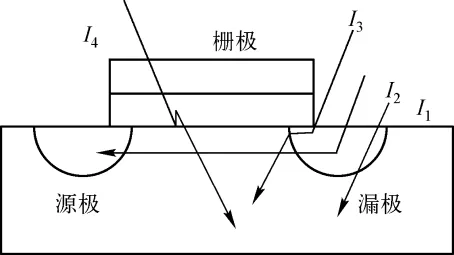

静态功耗主要是晶体管的漏电流引起的功耗,如下图所示:

PN结反向电流I1(PN-junction Reverse Current)

源极和漏极之间的亚阈值漏电流I2(Sub-threshold Current)

栅极漏电流,包括栅极和漏极之间的感应漏电流I3(Gate Induced Drain Leakage)

栅极和衬底之间的隧道漏电流I4(Gate Tunneling)

一般情况下,漏电流主要是指栅极泄漏电流和亚阈值电流(进入超深亚微米工艺之后,隧道漏电流成为主要电流之一)

栅极泄漏功耗:在栅极上加信号后(即栅压),从栅到衬底之间存在电容,因此在栅衬之间就会存在有电流,由此就会存在功耗。

亚阈值电流:使栅极电压低于导通阈值,仍会产生从FET漏极到源极的泄漏电流。此电流称为亚阈值泄漏电流。在较狭窄的晶体管中,漏极和源极距离较近的情况下会产生亚阈值泄漏电流。晶体管越窄,泄漏电流越大。要降低亚阈值电流,可以使用高阈值的器件

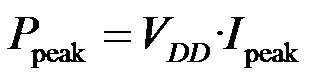

静态功耗的计算公式如下所示,Ileak为泄漏电流(Ipeak应该是Ileak):

注:

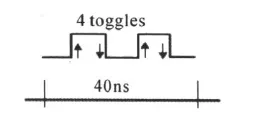

翻转率(Toggle rate,Tr):单位时间内信号(包括时钟、数据等等信号)的翻转次数。如下图所示:

信号在40ns时间内跳转了4次,翻转率为:Tr = 4/40ns = 0.1GHz

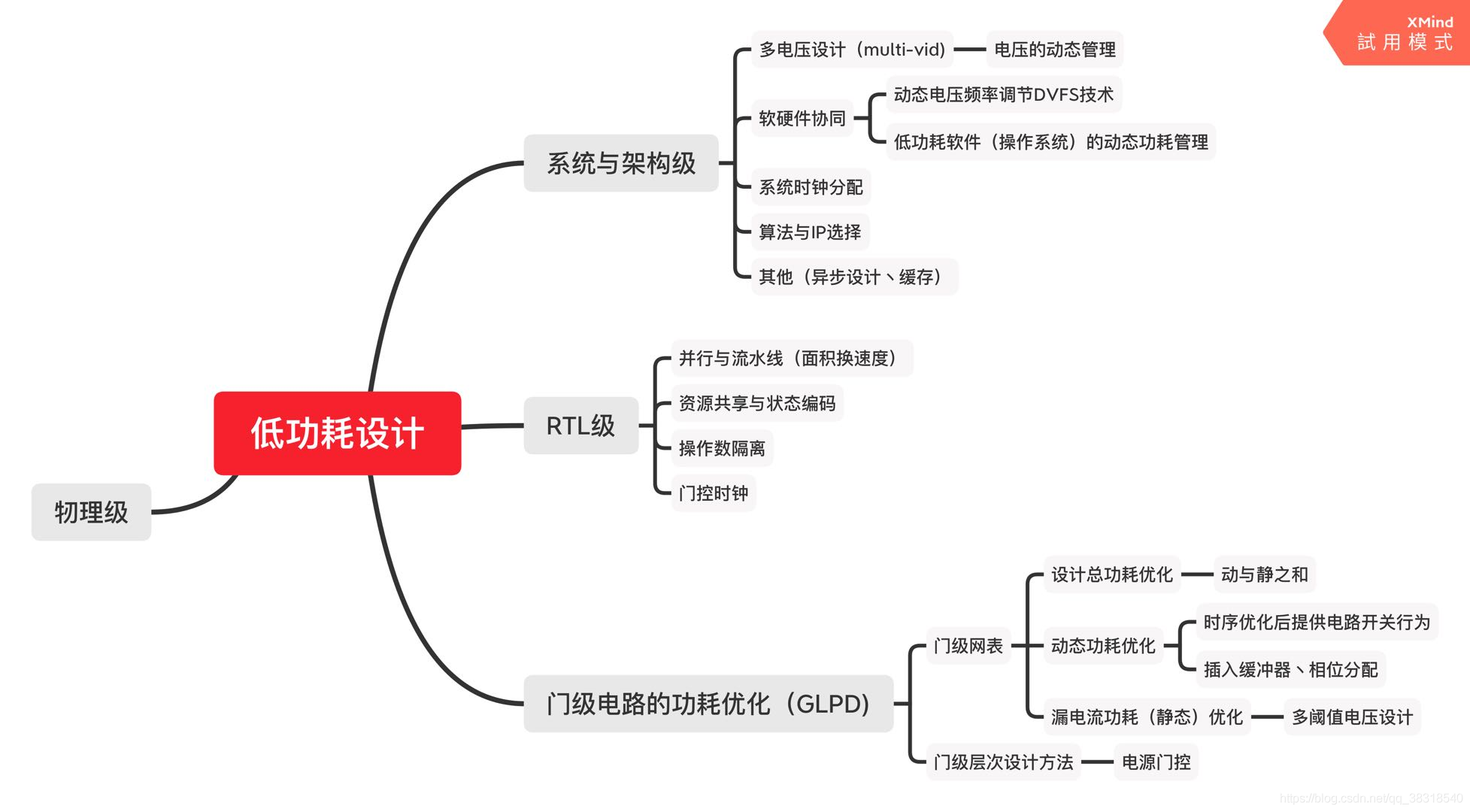

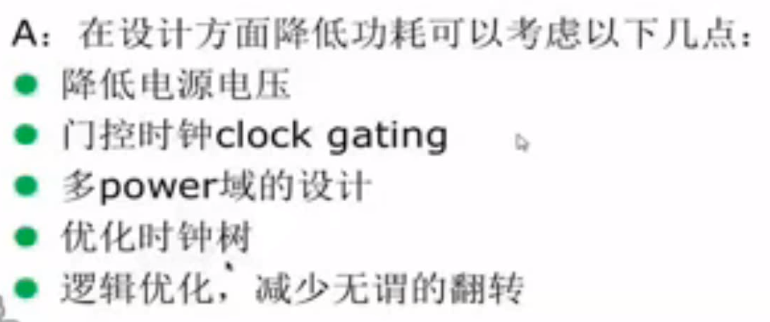

降低功耗:应当在所有设计层次上进行,即系统级、逻辑级和物理级,层次越高对功耗降低越有效; 在系统和体系结构级可以达到最大的降低效果;

系统架构级低功耗设计

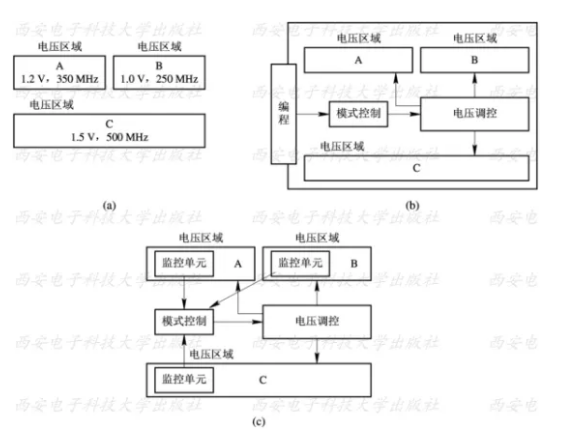

1. 多电压设计技术(Multi-VDD)

A:各电压区域有固定的电压,如上图(a)所示 ;

B:各电压区域具有固定的多个电压,由软件决定选择哪一个电压,如上图(b)所示;

C:自适应的方式,各电压域具有可变的,由软件决定选择哪一个电压,如上图(c)所示。

A是固定分配的电压;而B和C为动态电压管理,涉及到软硬件协同设计,这里我们放到后面进行介绍

包括电压控制单元:

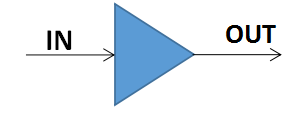

电平转换器(level shifter):把高(低)电压区域的信号转换到低(高)电压区域。信号通常包括数据、时钟、扫描链数据等。电平转换器的示意图如下所:

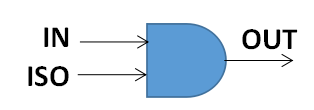

电源隔离单元(power isolation cell):主要用于模块的输入、输出。它可以关掉电源时,将信号保持为常数,从而避免单元的输入悬空。电源隔离单元如下图所示:

保持寄存器(retention register):在不工作的情况下,将寄存器的状态保留下来。

2. 动态电压频率调节DVFS技术

DVFS技术:dynamic voltage frequency scaling,动态电压频率技术,是一种通过将不同电路模块的工作电压及工作频率降低到恰好满足系统最低要求,来实时降低系统中不同电路模块功耗的方法。

电路模块中的最大时钟频率和电压紧密相关,降低时钟频率意味着可以同时降低供电电压。频率和电压同时降低,功耗就大大降低了。这个是DVFS的原理。

DVFS技术这个种方法属于电压的动态管理,可以通过软件和硬件的方式实现。

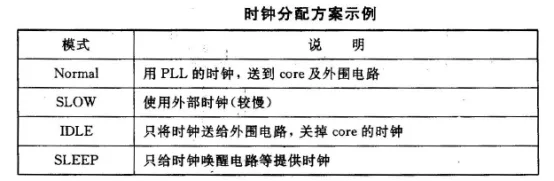

3. 系统时钟分配

时钟是系统中频率最高的信号,其功耗功之高是不容置疑的。在系统设计层面,可以考虑应用要求,**将系统设置为不同的工作模式,加入时钟控制模块,在不同的工作模式下选用不同频率的时钟,并且将一些不需要的模块时钟关闭。**时钟的分配可以使用内部的状态机实现,也可以使用软件实现。

例如,可以将系统分为4种工作模式:normal 、 slow、idle、sleep。在不同的模式下,器分频的时钟如下所示:

二、RTL级低功耗设计

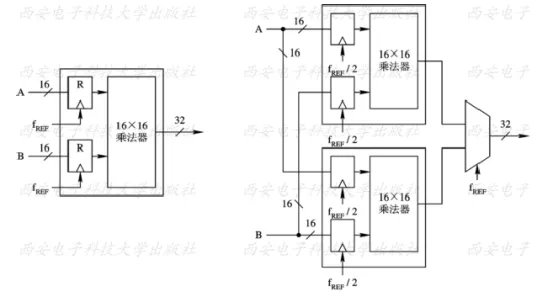

1. 并行化

面积换速度。常用于数字信号处理部分,可以降低系统工作频率,从而可能降低功耗。用两个乘法器来取代原设计中的一个乘法器。这样,时钟频率可以降低,系统的整体功耗会降低。(实际就是面积换速度)

感觉图里不太对。我理解的verilog实现方法:

原来周期5ns,一个16x16乘法器。现在周期10ns,两个16x16乘法器,A和B应该是32位的,第一个乘法器计算高16位相乘,第二个乘法器计算低16位相乘。

重点是和操作数隔离技术。

(1)并行与流水的选择

(2)资源共享与状态编码

外,对于一些变化非常频繁的信号,我们利用数据编码来降低开关活动(例如,用格雷码比用二进制码翻转更少,功耗更低)。

操作数隔离

门控时钟

门级

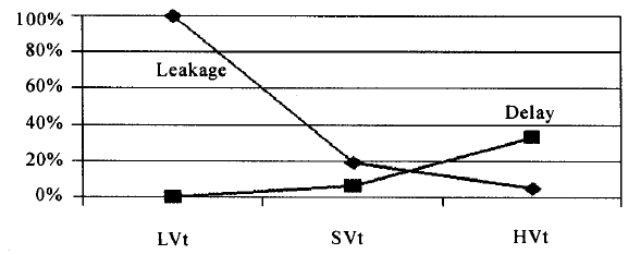

多阈值电压设计

单元门的阈值电压和漏电功耗(静态功耗)有如下图所示的关系:

由图可见,阈值电压Vt以指数关系影响着漏电功耗。阈值电压Vt与漏电功耗和单元门延迟有如下关系:

阈值电压Vt越高的单元,它的漏电功耗越低,但门延迟越长,也就是速度慢; 阈值电压Vt越低的单元,它的漏电功耗越高,但门延迟越短,也就是速度快。

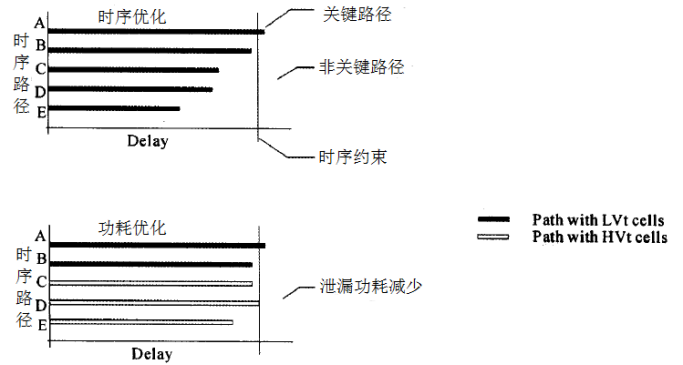

一般的设计中,一个时序路径组((timing path group)有多条时序路径,延迟最大的路径称为关键路径。根据多阈值电压单元的特点,为了满足时序的要求,关键路径中使用低阈值电压的单元(low Vt cells),以减少单元门的延迟,改善路径的时序。而为了减少静态功耗,在非关键路径中使用高阈值电压的单元(high Vt cells),以降低静态功耗。因此,使用多阈值电压的工艺库,我们可以设计出低静态功耗和高性能的设计。上面的描述如下图所示:

https://blog.csdn.net/Times_poem/article/details/73332703

最后

以上就是可爱耳机最近收集整理的关于数字IC低功耗设计的全部内容,更多相关数字IC低功耗设计内容请搜索靠谱客的其他文章。

发表评论 取消回复