Tinyriscv介绍

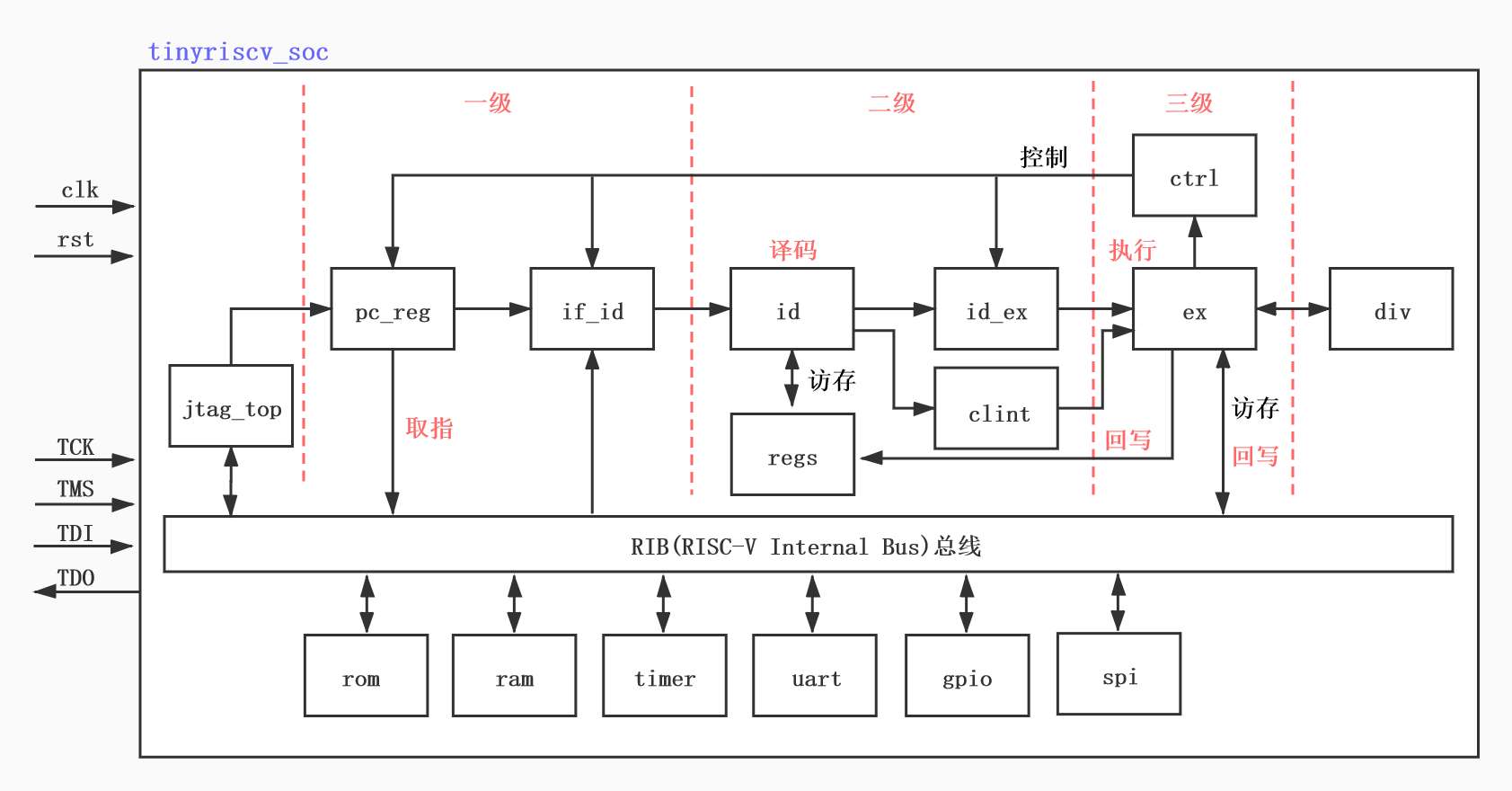

Tinyriscv: 本项目实现的是一个单核32位的小型RISC-V处理器核(tinyriscv),采用verilog语言编写。

tinyriscv有以下特点:

- 支持RV32IM指令集,通过RISC-V指令兼容性测试;

- 采用三级流水线,即取指,译码,执行;

- 可以运行C语言程序;

- 支持JTAG,可以通过openocd读写内存(在线更新程序);

- 支持中断;

- 支持总线;

- 支持FreeRTOS;

- 支持通过串口更新程序;

- 容易移植到任何FPGA平台(如果资源足够的话);

tinyriscv的整体框架如下:

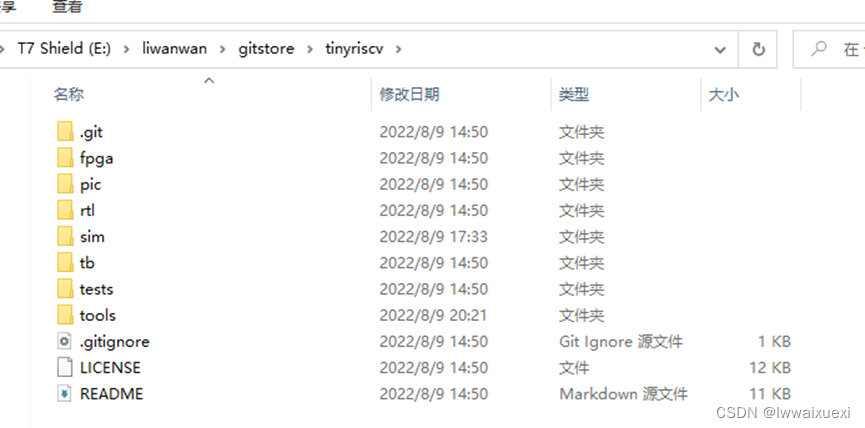

项目中的各目录说明:

rtl:该目录包含tinyriscv的所有verilog源码;

sim:该目录包含仿真批处理bat文件和脚本;

tests:该目录包含测试程序源码,其中example目录为C语言程序例程源码,isa目录为RV32指令测试源码;

tools:该目录包含编译汇编和C语言程序所需GNU工具链和将二进制文件转成仿真所需的mem格式文件的脚本,还有通过串口下载程序的脚本。

pic:存放图片;

tb:该目录包含仿真的testbench文件;

fpga:存放FPGA相关文件,比如约束文件;

在linux(ubuntu)平台上已经运行过指令测试程序通过

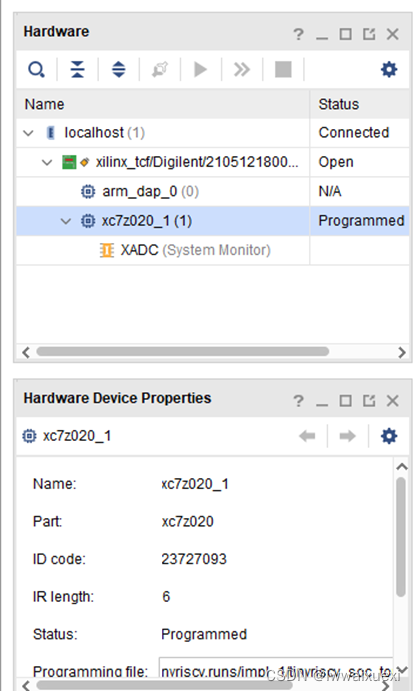

移植到FPGA ZYNQ7020

1.软件:xilinx vivado开发环境。

2.FPGA:xilinx ZYNQ7020。

3.调试上位机openOCD。

4.调试器:CMSIS-DAP。

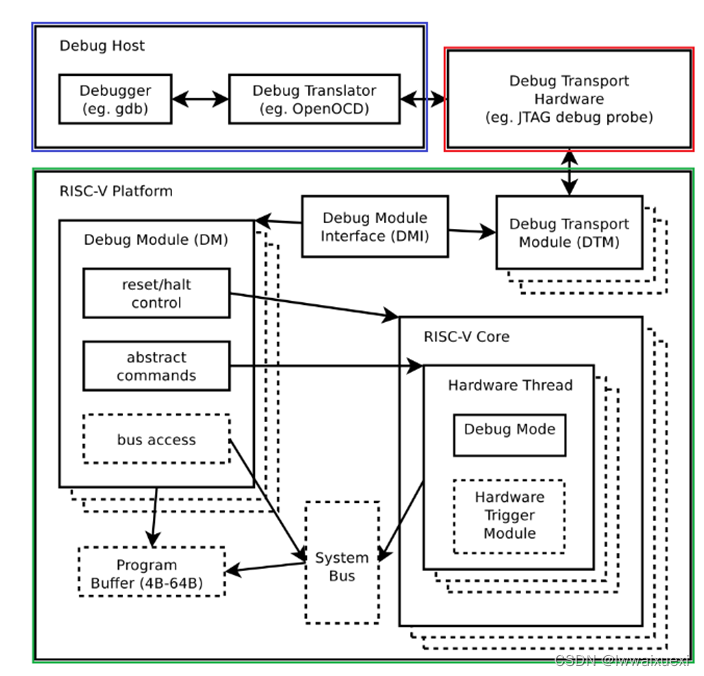

图1 RISCV调试系统框架

为与板子适配,修改源代码,修改管脚约束文件后,编译成功后,将比特流文件下载到板子中。

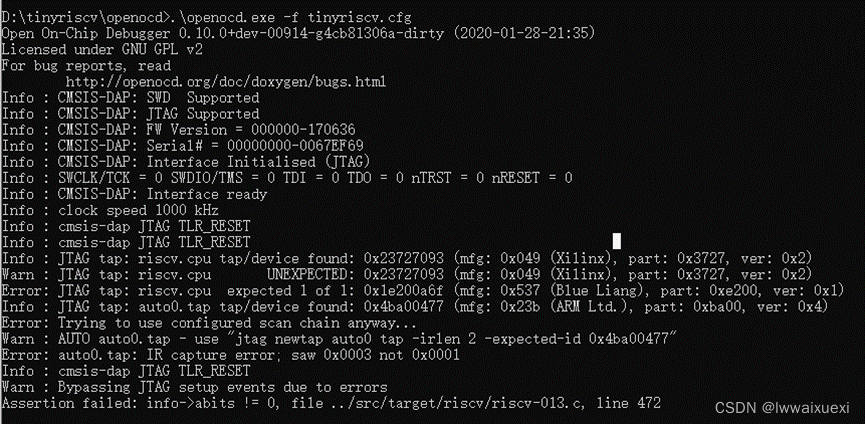

在用Jtag方式通过openocd调试tinyriscv时出现问题

一开始是调试器识别到两个jtag,后与同学讨论认为,ZYNQ7020是一块有arm硬核(PS)和可编程逻辑(PL可认为是FPGA)组成,不能直接调用jtag接口,所有的调用需要通过arm硬核来实现,上网查了很多资料未能解决。

移植到FPGA ARTY A7 100T

1.软件:xilinx vivado开发环境

2.FPGA:xilinx ARTY A7 100T

3.调试上位机openocd

4.调试器:CMSIS-DAP

参考ARTY A7 100T技术手册

https://digilent.com/reference/programmable-logic/arty-a7/reference-manual

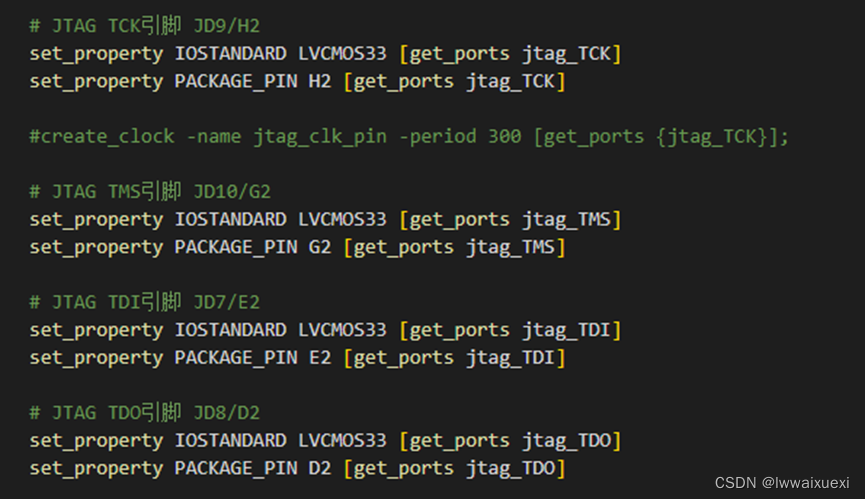

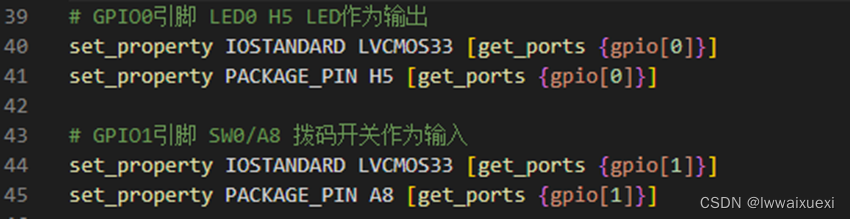

管脚约束

digilent-xdc/Arty-A7-100-Master.xdc at master · Digilent/digilent-xdc · GitHub

原理图

https://digilent.com/reference/_media/programmable-logic/arty-a7/arty-a7-e2-sch.pdf

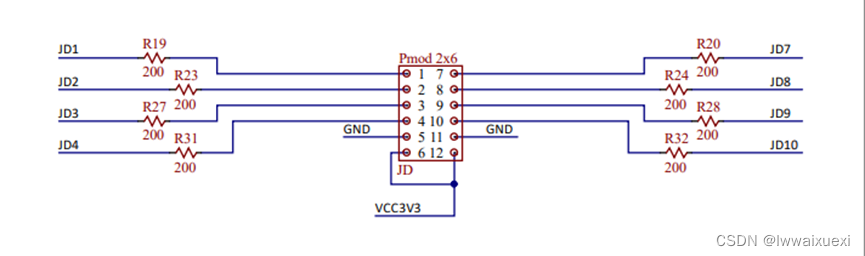

JTAG连接

和开发板上的pmod连接在一起

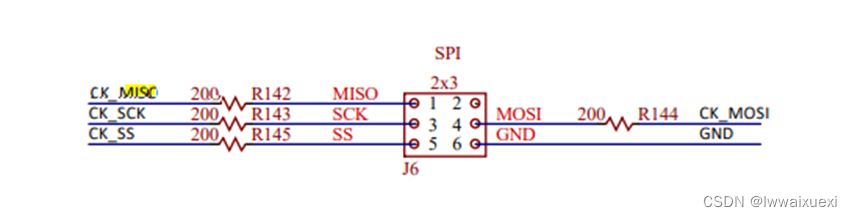

SPI

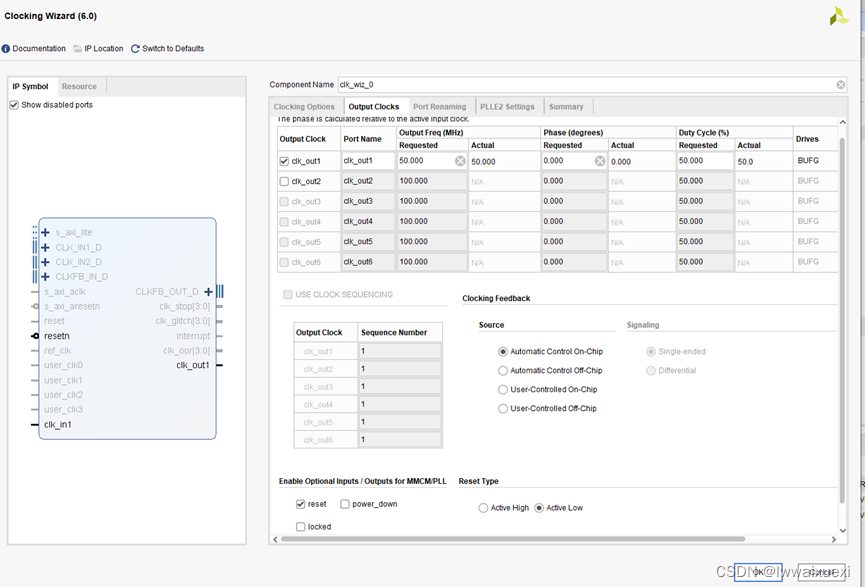

时钟约束50MHz

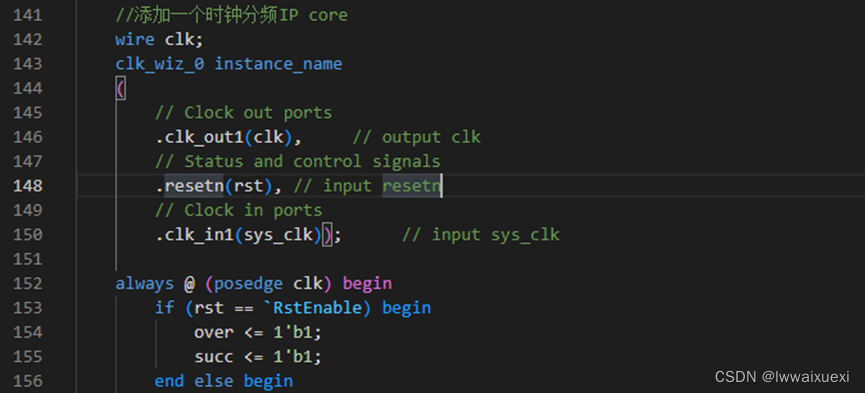

A7时钟源 是100MHz 直接接上去tinyriscv跑不了这么快 做一个时钟分频

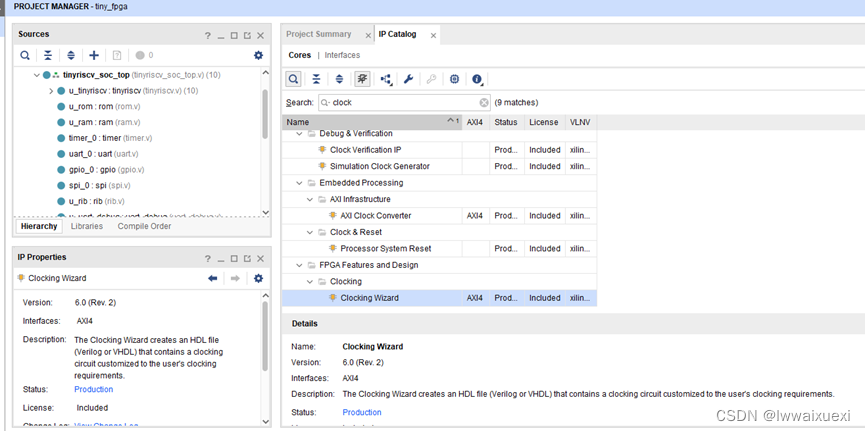

添加IP核 PLL

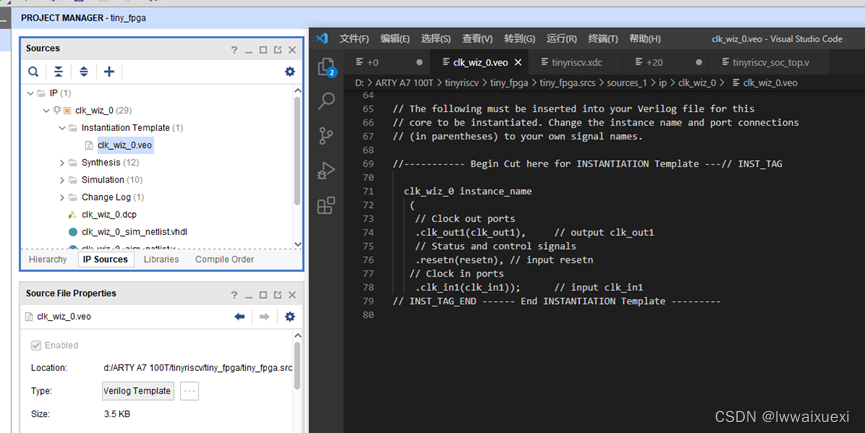

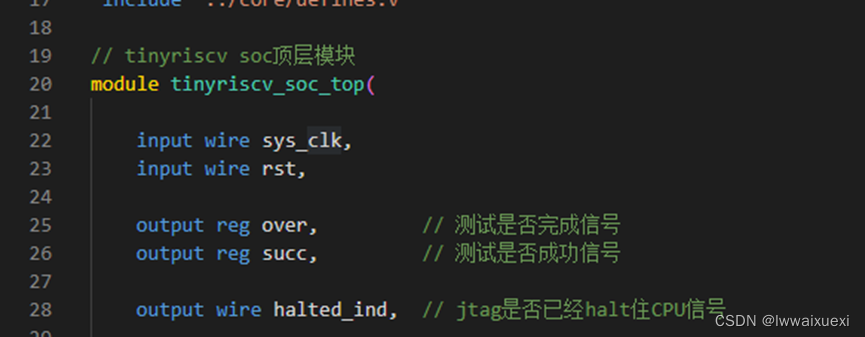

系统提供的例化模板

将例化添加到顶层文件tinyriscv_soc_top中

要注意 必须要在第一次使用时钟之前例化出来

例化模块中输入是sys_clk 输出是clk

Clk是没有声明的状态 需要声明 复位也要保持一致 rst

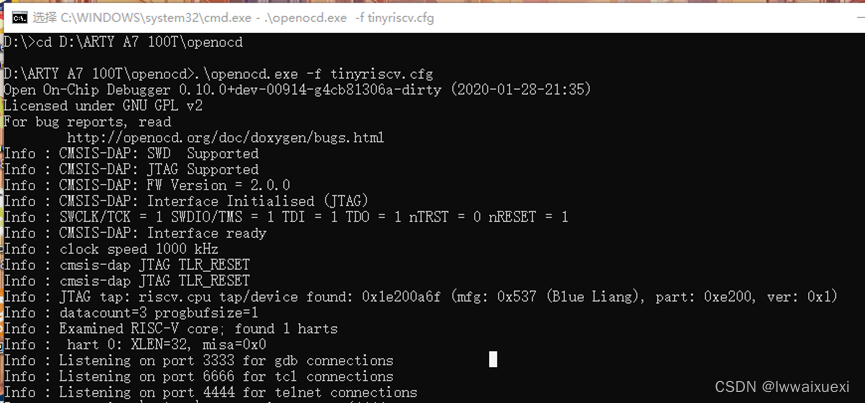

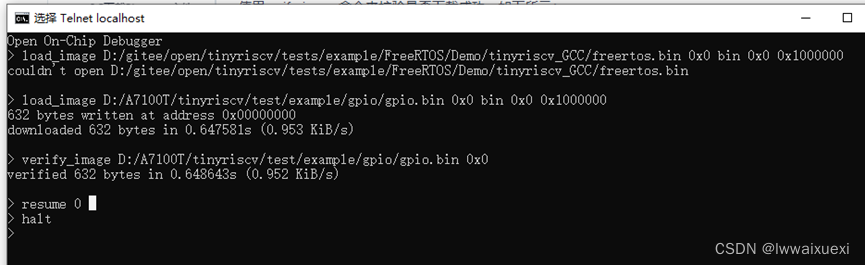

Openocd作为上位机

通过JTAG方式下载程序并让程序跑起来

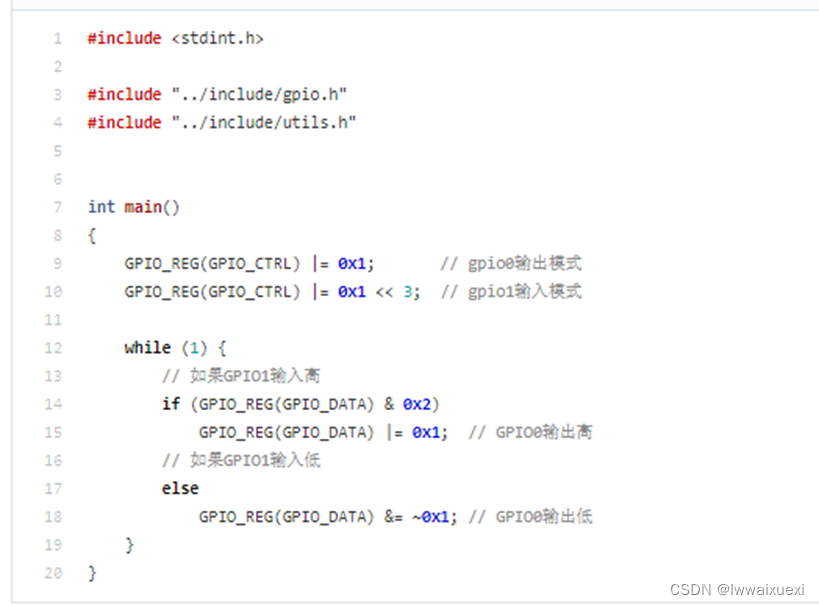

例: GPIO程序

两个GPIO口 一个输入模式 一个输出模式 关联起来

下载GPIO程序并运行 拨动拨码开关SW0 可以看到LED随之亮灭

参考

深入浅出RISC-V调试 | liangkangnan的博客

从零开始写RISC-V处理器 | liangkangnan的博客

最后

以上就是高贵心锁最近收集整理的关于Tinyriscv FPGA移植的全部内容,更多相关Tinyriscv内容请搜索靠谱客的其他文章。

发表评论 取消回复