我们知道运放的特点都是高输入阻抗,低输出阻抗;而假设的理想运放更是将输入阻抗近似到无穷大,输出阻抗趋近于零;高输入阻抗是为是减小对前级的影响,而低输出阻抗带负载能力强,所以在小信号放大电路中我们总是在前级设计一个跟随电路,提高电路的性能。

然而运放并不是理想运放,所以每个datasheet会列出它在极限条件下参数值供我们参考,在datasheet中有一个参数:开环输出阻抗(Open loop output resistance)Ro。如果没有给出这个明确值,可以参考大神的文章自己计算。运放datasheet中未给出Ro的值时,请参照Tim Green的应用文档集“运算放大器的稳定性”第三篇。

那么什么情况下我们需要考虑输出阻抗呢?

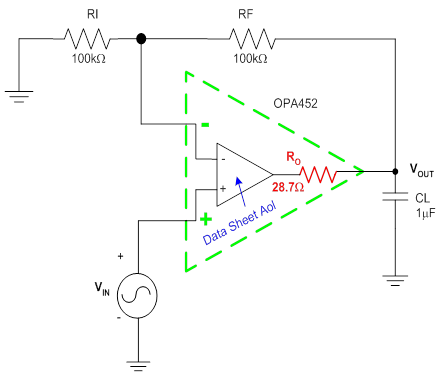

由于Ro的存在,并且不像理解运放中的为零,运放在驱动容性负载时,就会出问题了。主要问题是Ro和负载电容相互作用给放电大路的环路增益引入一个极点。

copy一个大神的帖子:https://e2echina.ti.com/question_answer/analog/amplifiers/f/52/t/23358

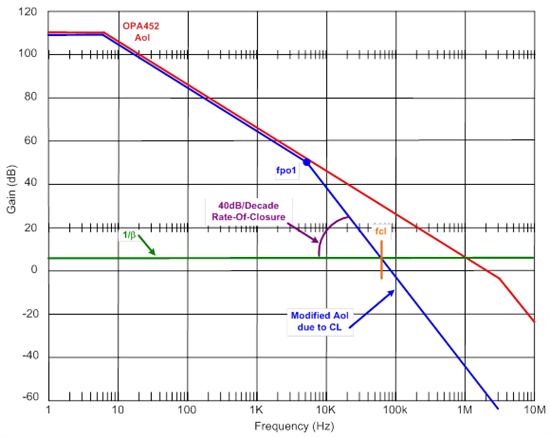

f(po1) = 1/(2ΠRC),很容及计算出这个极点f(po1) = 5.545kHz,将环路增益画成了波特图进行分析

引入的这一新的极点Fpo1使得运放的开环益在Fpo1以后以40dB/dec的速度滚降。它反馈系数倒数的直线时在相交点fcl时闭合速度为40dB/dec。这足以使放大电路不稳定了。(注:放大电路稳定性的判据为开环增益Aol曲线与反馈系数的倒数曲线在相交点fcl处的闭合速度为20dB/dec则放大电路稳定)

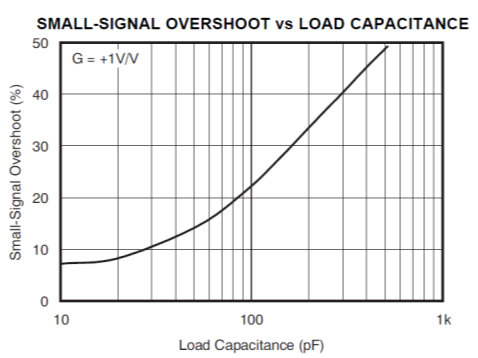

即使放大电路没有发生震荡,它也会使得放大电路对方波响应时有一个过冲。如下图,是在不同负载电路下小信号过冲的曲线。从曲线中可以看出,500pF的负载电路可以使放大电路过冲达50%。这个曲线很重要哦,在很多运放的datasheet中会给出。

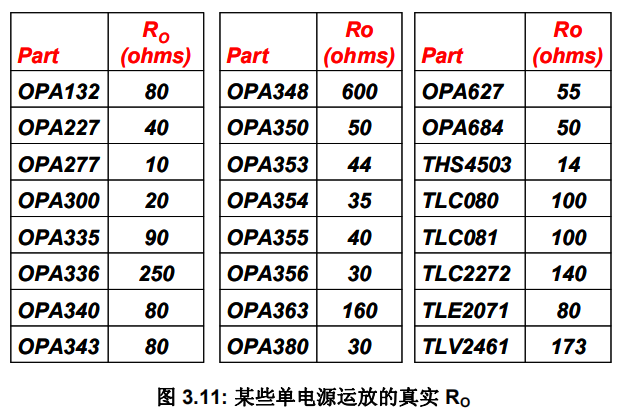

我们截取一下部分单电源运放的实测Ro,来自于“运算放大器的稳定性”

从上面一个图例我们假设一个使用环境,运放驱动一个容性负载(设置0.1uF)输出,那么极点范围主要在

2.6K~160K(Hz)间,引用一个网友的原帖:如果是要做高频信号的长线驱动,则RO的大小有影响。就是RO和输出电容CL会组成一个极点,会影响AMP的主POLE ,因为RO会随着频率的增加而增加,则POLE会左移,可能引起自激。(https://bbs.21ic.com/icview-210488-1-1.html)

文章索引:

https://e2echina.ti.com/question_answer/analog/amplifiers/f/52/t/23358

https://bbs.21ic.com/icview-210488-1-1.html

最后

以上就是痴情白昼最近收集整理的关于运放 - 输出阻抗(Open loop output resistance)Ro的全部内容,更多相关运放内容请搜索靠谱客的其他文章。

发表评论 取消回复