目录

问题:

问题分析及解决:

总结:

问题:

写状态机实现序列检测"HELLO"时,检查源代码半天都没发现错误,但观察波形图总是与预期有差距。最后发现是tb文件的错误,这里先附一下我第一次写的tb文件

always #100 clk=~clk; initial begin data = 0; clk = 0; rst_n = 0; #100; rst_n = 1; data = "b"; #100; data = "H"; #100; data = "e"; #100; data = "l"; #100; data = "b"; #100; data = "H"; #100; data = "e"; #100; data = "l"; #100; data = "l"; #100; data = "o"; #100; data = "h"; #100; data = "e"; #100; data = "l"; end endmodule之前的话一直都是让时钟信号clk每100 ns翻转一次,每100 ns数据改变一次,clk初始值为0,同时过100ns后也让复位信号rst_n失效,由0变1。相信不少的同学刚开始也跟我一样这样写。下面我们分析一下问题

问题分析及解决:

首先,输出为0的原因clk翻转的时间是和数据输入的时间相等,这里必须要使clk翻转时间必须等于数据输入的时间一半,原因是让每一次的数据输入时间等于clk的一个周期。

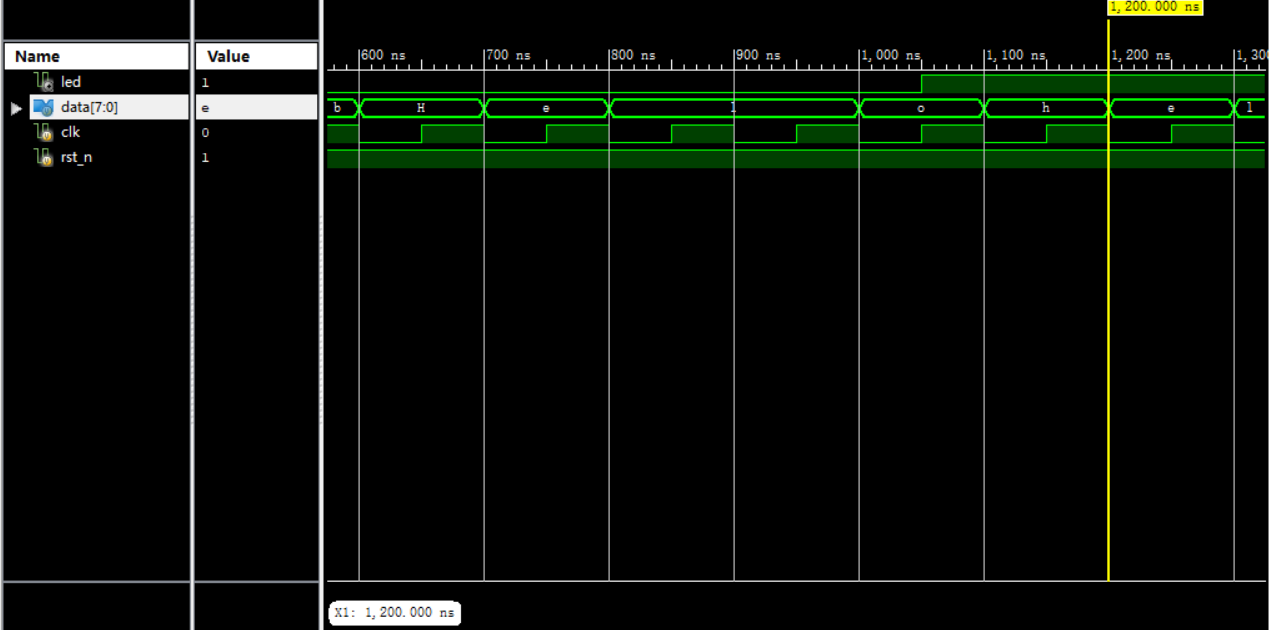

这是再去看上图仿真已经检测到了"HELLO",不过输出out的位置位于输入字母'o'的中间,这时的问题是clk=0,在输入的半个周期时出现上升沿导致输出为1,因此我们将clk改为1即可。

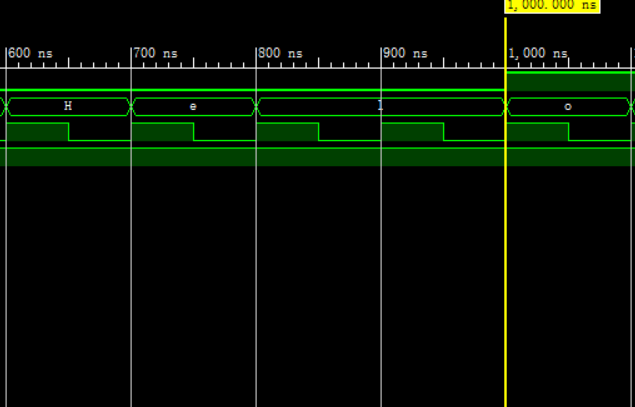

通过仿真又发现了问题,此时检测到"HELL"输出out就变成了高电平。

出现问题的是因为输入信号此时和上升沿触发信号重合,此时由于在上升沿时刚刚触发,输入并不稳定,因此我们应该给输入1ns的稳定时间。

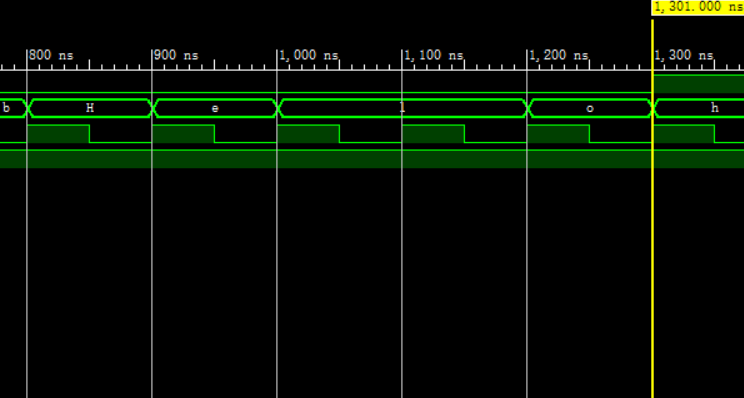

此时这个波形就达到了我们的预期。

总结:

以上是对tb文件导致仿真出错的一些问题,因此我们以后就按照下面的格式进行书写。

always #50 clk=~clk; initial begin data = 0; clk = 1; rst_n = 0; #201; rst_n = 1; #100; data = ...; #100; data = ...; . . .

最后

以上就是哭泣白羊最近收集整理的关于tb文件中的书写所出现问题Verilog的全部内容,更多相关tb文件中内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复