在使用MATLAB HDL Coder Toolbox的时候,每次新建一个Simulink模型都会重置Verilog代码生成的参数,默认生成VHDL代码,不生成Report,有时候也不需要clk_enable信号,所以需要有一个方便的办法自动批量更改一下。

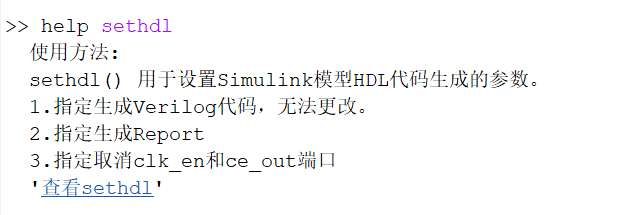

这个脚本的目的:

在MATLAB命令行输入: sethdl(),会自动获取当前活动的Simulink模型,然后将输出代码更改为Verilog,生成可跟踪的Report等,读者可以根据自己的需求更改脚本,如果没有活动的Simulink模型则无操作。

function sethdl()

% 使用方法:

% sethdl() 用于设置Simulink模型HDL代码生成的参数。

% 需要注意:模型需要保存到当前路径,否则会找不到文件!

% 1.指定生成Verilog代码,无法更改。

% 2.指定生成Report

% 3.指定取消clk_en和ce_out端口

% '<a href = "matlab:edit('sethdl')">查看sethdl</a>'

model_name = bdroot;

path_name = pwd;

filename = fullfile(path_name,model_name);

if exist(filename)

% DUTname = hdlget_param(bdroot,'HDLSubsystem');

hdlset_param(model_name,'TargetLanguage','Verilog');

hdlset_param(model_name,Traceability = 'on',TraceabilityStyle = 'Line Level');

hdlset_param(model_name,MinimizeClockEnables = 'on');

else

disp('当前没有打开的Simulink文件。')

end

end

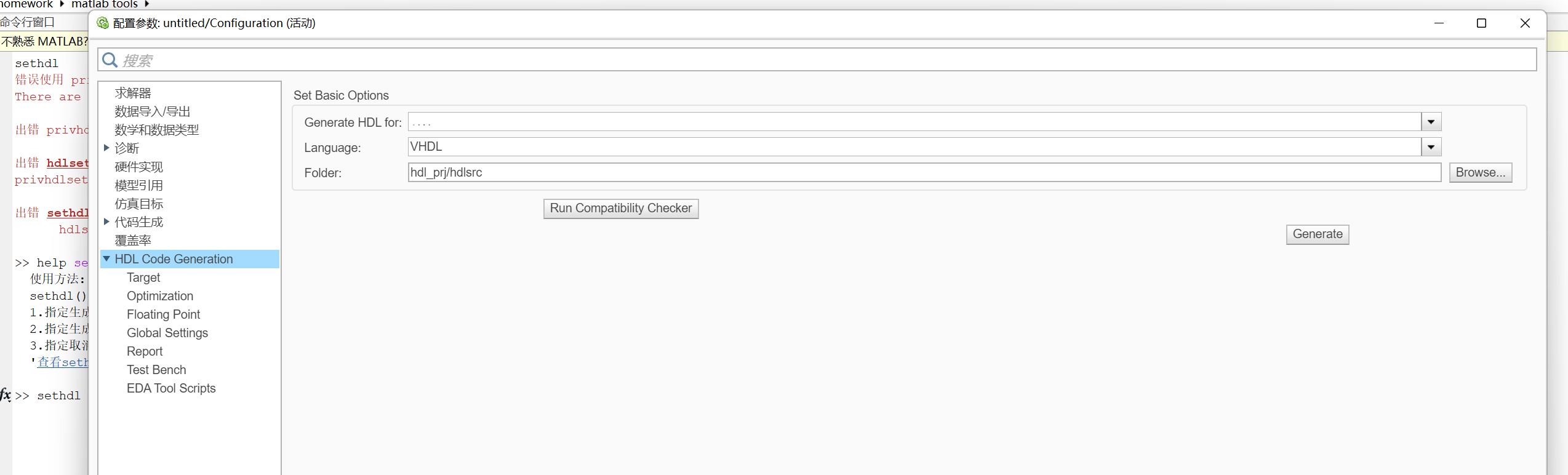

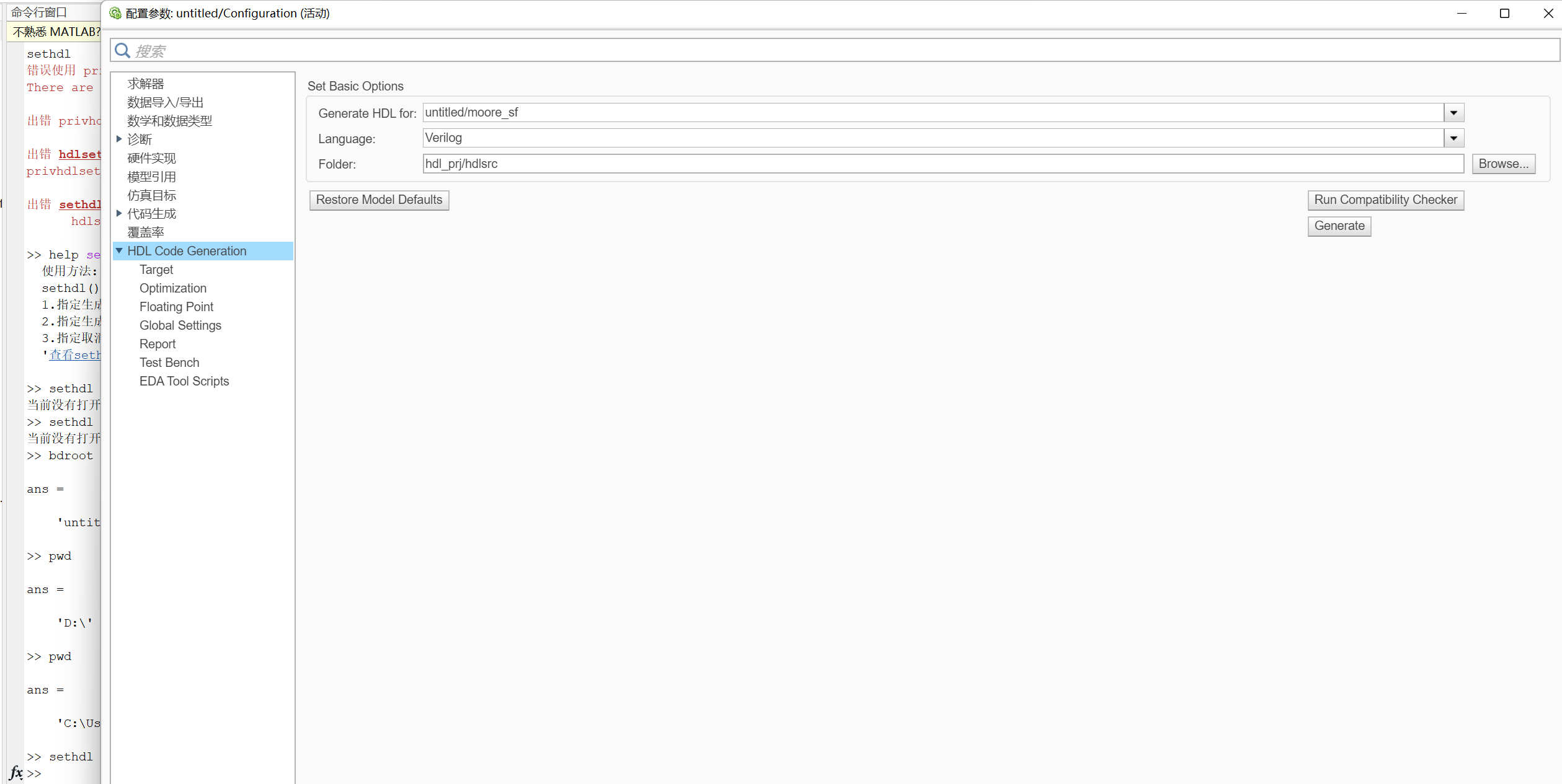

效果如下:

运行:

>>sethdl

最后

以上就是鲤鱼小伙最近收集整理的关于Simulink HDL Coder FPGA开发之 脚本自动设置HDL参数的全部内容,更多相关Simulink内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复