我是靠谱客的博主 拼搏小海豚,这篇文章主要介绍数字IC秋招面试专题(三)异步复位和同步复位前言一、同步复位二、异步复位三、同步复位和异步复位的区别四、 异步复位同步释放,现在分享给大家,希望可以做个参考。

数字IC秋招面试专题(三)异步复位和同步复位

- 前言

- 一、同步复位

- 二、异步复位

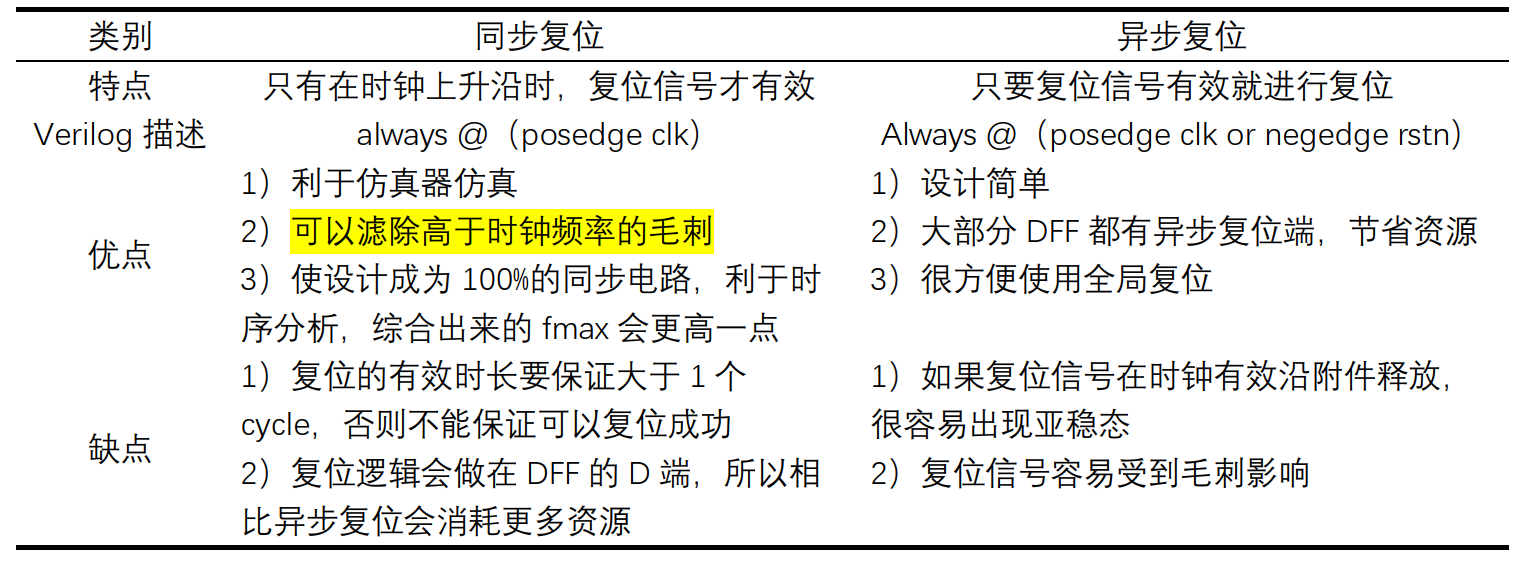

- 三、同步复位和异步复位的区别

- 四、 异步复位同步释放

????声明:

????未经作者允许,禁止转载

????推荐一个IC、FPGA新手入门的好网站:????点击进入学习吧

前言

本章解释一下同步复位和异步复位的区别,以及异步复位同步释放究竟好在哪里,需要怎么做一、同步复位

同步复位就是只有在时钟上升沿时,复位信号才有效

代码如下:

module sync_rst(

input clk,

input rstn,

input din,

output reg dout

);

always @(posedge clk)

begin

if(!rstn)

dout <= 0;

else

dout <= din;

end

endmodule

二、异步复位

只要复位信号有效就进行复位

代码如下:

module sync_rst(

input clk,

input rstn,

input din,

output reg dout

);

always @(posedge clk or negedge rstn)

begin

if(!rstn)

dout <= 0;

else

dout <= din;

end

endmodule

这里异步和同步复位在代码上的区别仅有always块内多了一个negedge rstn的信号触发

但是综合出来的电路却是完全不一样的

三、同步复位和异步复位的区别

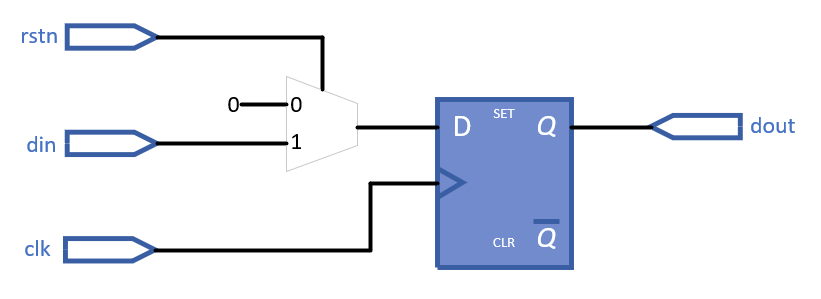

- 同步复位综合后的电路会如下所示,其复位会放在DFF外面单独做一个逻辑,这样会耗费一定的资源,因为只会在始终有效沿复位,所以异步复位可能发生的毛刺和亚稳态在此不会发生

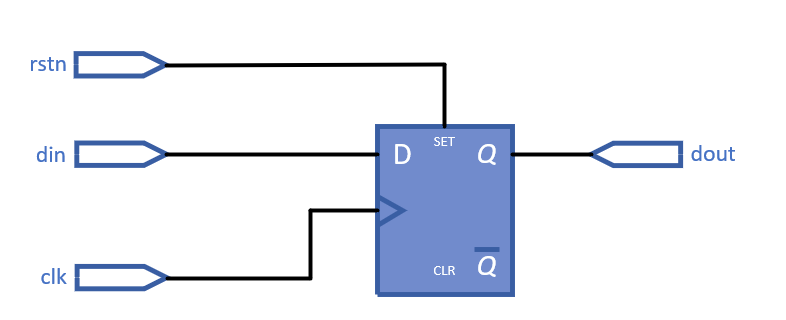

- 而异步复位可以直接用DFF的异步复位端口,其综合后的电路如下

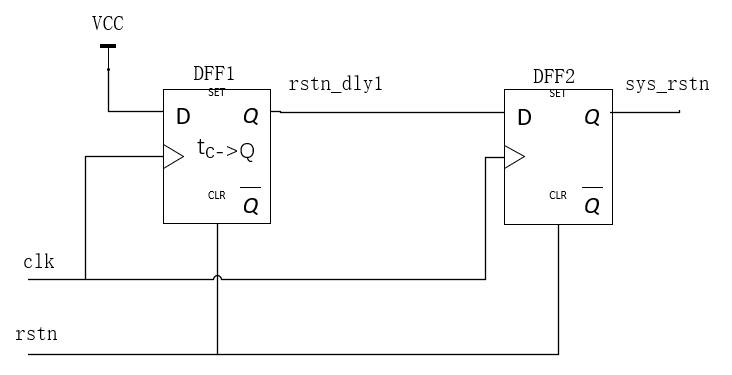

四、 异步复位同步释放

结合同步电路可以滤除毛刺,防止亚稳态和异步电路可以节省资源的优点就设计了异步复位同步释放的电路。

代码如下:

module sync_rst(

input clk,

input rstn,

input din,

output reg dout

);

reg rstn_dly1;

reg rstn_dly2;

wire sys_rstn;

assign sys_rstn = rstn_dly2;

always @(posedge clk or negedge rstn)

begin

if(!rstn) begin

rstn_dly1 <= 1'b0;

rstn_dly2 <= 1'b0;

end

else begin

rstn_dly1 <= 1'b1;

rstn_dly2 <= rstn_dly1;

end

end

always @(posedge clk or negedge sys_rstn)

begin

if(!sys_rstn)

dout <= 0;

else

dout <= din;

end

endmodule

这里用到了避免亚稳态的同步器设计,对复位信号进行异步复位,并用同步器打两拍,这样复位信号只会在时钟有效沿才释放,并且避免了亚稳态,在这段代码中,对rstn做了异步复位同步释放,后续所有的电路只需要用sys_rstn作为复位信号即可。

- 在实习面试的时候,被问到过异步复位,同步释放这种电路形式;大致知道但是最后没敢说出口;

- 此处画图总结一下,加深印象

这里可以看出rstn一旦拉低,sys_rstn就会拉低,这就达到异步复位的要求;

而同步复位为什么要一个缓冲器来完成呢?

- 没有缓冲器,rstn刚好释放在有效沿,sys_rstn就会发生亚稳态;

- 而有一级缓冲器,即使释放在有效沿,sys_rstn也会采样rstn_dly1的值,最多就是没有晚一拍释放,但亚稳态概率会大大降低;

- 而这个释放拉高的功能就需要DFF的D端和高电平相连完成了。

最后

以上就是拼搏小海豚最近收集整理的关于数字IC秋招面试专题(三)异步复位和同步复位前言一、同步复位二、异步复位三、同步复位和异步复位的区别四、 异步复位同步释放的全部内容,更多相关数字IC秋招面试专题(三)异步复位和同步复位前言一、同步复位二、异步复位三、同步复位和异步复位的区别四、内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复