在数字电路中组合逻辑电路可能会产生竞争与冒险,时序电路有产生亚稳态的风险。在时序电路中,对于边沿触发的触发器来说,其有两个状态即高和低。如果在数据传输中不满足触发器的set up time和 hold up time(ps:触发器的建立时间和保持时间在时钟上升沿左右定义了一个时间窗,如果触发器数据输入端口上的数据在这个时间窗内发生了变化,那么就会产生时序违规。当建立时间和保持时间要求被违反了,此时触发器内部逻辑状态也许是高电平状态也许是低电平状态,状态不确定,从而导致数字部件逻辑混乱)。复位过程中复位信号的释放相对于有效时钟沿的恢复时间(recovery time)不满足也会产生亚稳态,造成复位失败。

1 理论分析

1.1 信号传输中的亚稳态原因

在同步系统中(通俗就是只有一个时钟驱动fpga系统。ps:有相位关系的时钟算一个时钟,比如分频得到的时钟:),输入信号总是与系统时钟同步,亚稳态不会产生。通常亚稳态发生在一些跨时钟信号传输以及异步信号采集上。

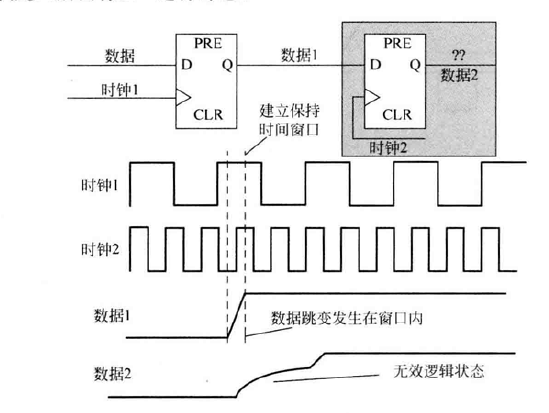

(1)在跨时钟域信号传输时,由于源寄存器时钟和目的寄存器时钟相移未知,所以另一个时钟域发送数据,数据可能在任何时间到达异步时钟域目的寄存器,无法保证目的寄存器的建立时间和保持时间的要求。如下图:

1.2 处理亚稳态的经典方法(双触发)

设计中任何寄存器都会指定一个建立和保持时间,在这个时钟上升沿前后的这个时间段内输入的数据禁止发生任何变动。当在两个时钟域传输信号时,需要考虑的一个问题是:是否需要采样另一个时钟传输过来的所有值。因此就有两种情况,允许丢失部分信号采样值和不允许丢失采样值。

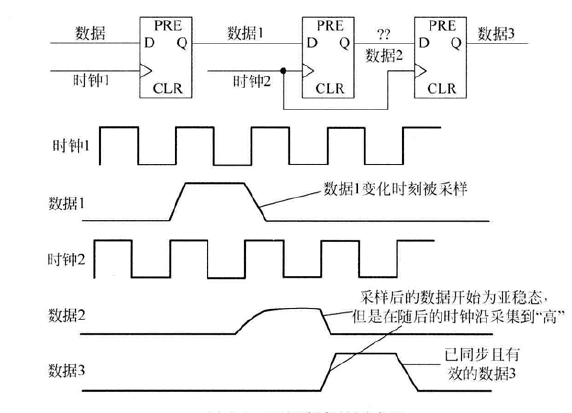

最常见的同步器就是使用两级寄存器,即使用寄存器打两拍的方式同步。

当然两级寄存器输出也不能一定保持稳定状态,因为这种振荡时间有长有短,如长到大于一个采样周期,那么二级寄存器也会进入亚稳态,因此出现三级触发器以至多级(尤其在高速设计中)。资料显示第一级寄存器出现亚稳态的话,第二级稳定输出的概率为90%,第三级99%。

1.2 使用fifo结构处理跨时钟域信号

当数据流从一个时钟域到另一个时钟域的时候,绝大多数情况下都采用fifo来作为中间缓冲,采用双时钟对数据进行缓冲,就可以避免亚稳态的发生。

2.1 复位电路中的亚稳态

复位电路中,有同步复位和异步复位(ps:同步异步大致就是受时钟沿控制就叫同步,不受时钟沿控制就叫异步),由于复位信号异步的,因此有设计采用同步复位进行复位的。很多资料说同步复位不会发生亚稳态情况,其实也会产生,只不过概率小于异步复位电路。同步复位代码如下:

always @(posedge clk)

begin

if(!rst_n) a <= 1’b0;

else a <= b;

end异步复位代码·

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) a <= 1’b0;

else a<=1'b1;

end要解决复位中的亚稳态最常用的方式是:异步复位,同步释放。这种方式结合两种复位方式的优势。异步复位的优势是不参与数据路径,不影响速度,而同步复位优势是百分之百的同步时序且具有抗噪声性能。代码如下:

reg rst_n_1 = 1'b1;

reg rst_n_2 = 1'b1;

always @ (posedge clk or negedge rst_async_n)

begin

if( !rst_async_n ) begin

rst_n_1 <= 1'b0;

rst_n_2 <= 1'b0;

end

else begin

rst_n_1 <= 1'b1;

rst_n_2 <= rst_n_1;

end

end

assign rst_sync_n = rst_n_2;

最后

以上就是傲娇唇膏最近收集整理的关于(一)亚稳态的全部内容,更多相关(一)亚稳态内容请搜索靠谱客的其他文章。

发表评论 取消回复