同步时序电路概述

通过电路的输入、输出端、功能规范和时序规范可以定义一个电路。一个时序电路有一组有限的离散状态{S0,S1,…,Sk-1}。同步时序电路有一个时钟输入,它的上升沿表示电路状态转变发生的时间。我们经常用术语当前状态(current state)和下一个状态(next state)来区分。功能规范详细说明了对于当前状态和输入值的各种组合,每个输出的下一个和值。时序规范包括上界和下界时间,它是从上升沿直到输出改变的时间,还有建立时间和保存时间,它表示当输入必须相对于时钟的上升沿稳定。

同步时序电路的条件:

每个电路元件是寄存器或组合电路

至少有一个寄存器

所有寄存器都接收同一个CLK

每个环路都至少包含一个寄存器

有限状态机

同步时序电路可以以有限状态机(Finite State Machine,FSM)的形式来描述。

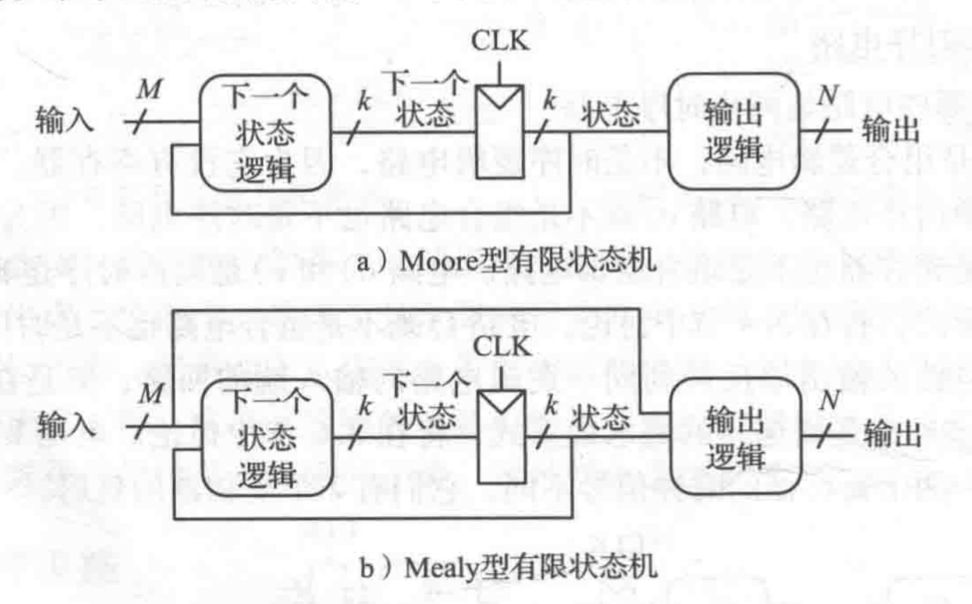

一个FSM有M个输入,N个输出和k位状态。它还接收一个时钟信号和一个可选择的的复位信号。有限状态机包括两个组合逻辑块,下一个状态逻辑(next state logic)和输出逻辑(output logic),以及一个存储状态的寄存器。在每个时钟沿,有限状态机进入下一个状态。

在Moore型有限状态机中,输出取决于当前状态;在Mealy型有限状态机中,输出取决于当前状态和当前输入。

有限状态机设计实例:

明确设计条件、画出状态转换图、重写为状态转换表(将状态和输出按照二进制编码)、读出用与或式表示的布尔表达式并化简、绘制电路图。

两种状态编码:二进制编码、独热编码(001、海子姐、100)。

状态的每一位存储在一个触发器中,所以独热编码比二进制编码需要更多的触发器。然而,使用独热编码,下个状态和输出逻辑通常更简单,需要的门电路也更少。

最后

以上就是虚拟大山最近收集整理的关于同步时序电路同步时序电路概述有限状态机的全部内容,更多相关同步时序电路同步时序电路概述有限状态机内容请搜索靠谱客的其他文章。

发表评论 取消回复