Verilog同步异步复位D触发器的描述

对于D触发器DFF的同步异步,我是吃过亏的,所以一定要理解清晰,同步和异步的概念。

本篇主要例举出同步,异步,复位,置位D触发器的Verilog描述。

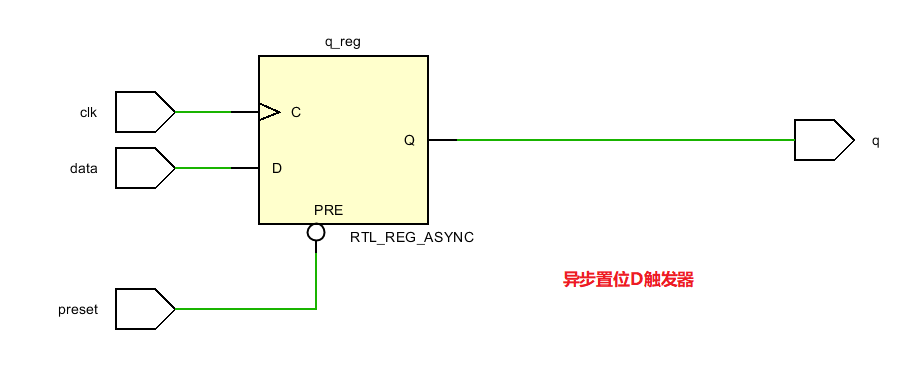

异步置位D触发器

关键在于使用信号preset的下降沿事件,作为always的触发,这样,无论时钟clk处于何种状态,都会对输出q进行置位操作,美其名曰:异步置位;

RTL code

module dff_async_pre (

input data, clk, preset,

output q

);

parameter UDLY = 1;

reg q;

always @ (posedge clk or negedge preset) begin

if ( ~preset ) begin

q <= #UDLY 1'b1;

end else begin

q <= #UDLY data;

end

end

endmodule

逻辑图

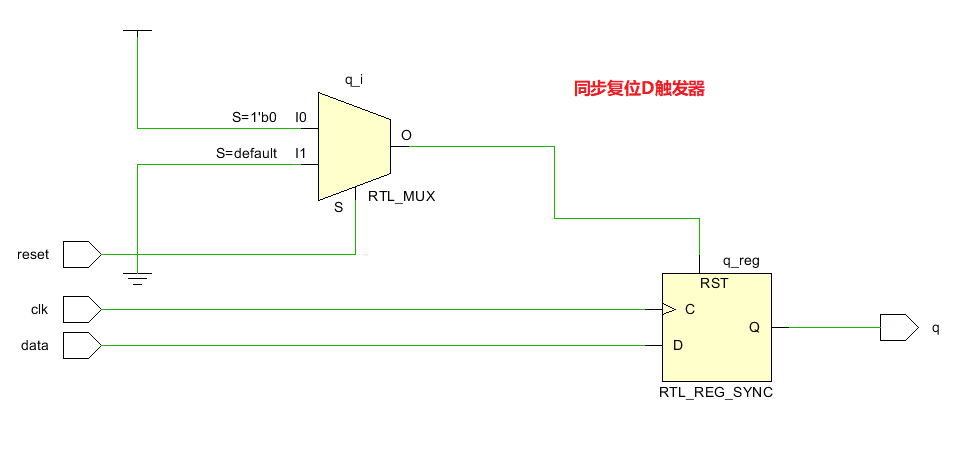

同步复位D触发器

仅由clk上升沿事件作为always的触发,所以复位动作,需要与clk同步才能完成,美其名曰:同步复位;

RTL code

module dff_sync_rst (

input data, clk, reset,

output q

);

parameter UDLY = 1;

reg q;

always @ (posedge clk) begin

if ( !reset ) begin

q <= #UDLY 1'b0;

end else begin

q <= #UDLY data;

end

end

endmodule

逻辑图

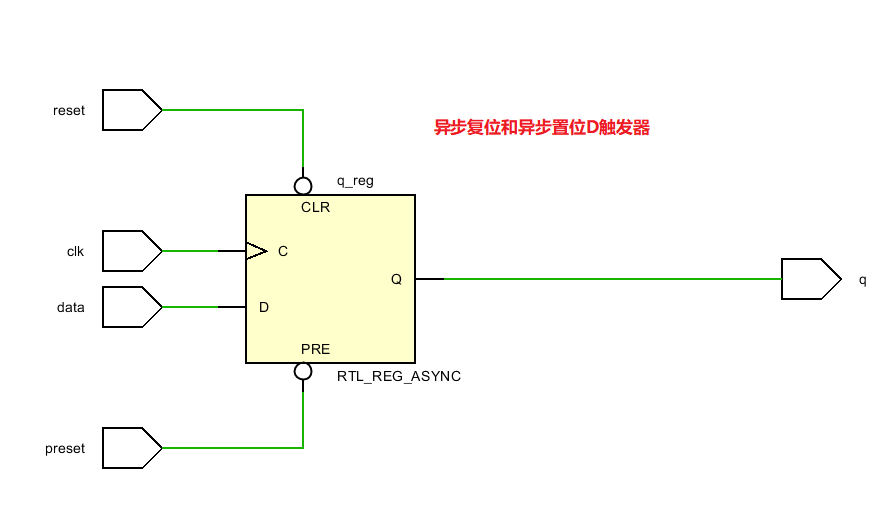

异步复位和异步置位D触发器

有了上面两个例子,这个就好理解了,这就是带有异步复位和异步置位DFF的描述;

RTL code

module dff_async (

input data, clk, reset, preset,

output q

);

parameter UDLY = 1;

reg q;

always @ (posedge clk or negedge reset or negedge preset) begin

if ( ~reset) begin

q <= #UDLY 1'b0;

end else if ( ~preset) begin

q <= #UDLY 1'b1;

end else begin

q <= #UDLY data;

end

end

endmodule

逻辑图

更新

2020-03-04更新RTL原理图,程序Vivado编译无Error。

最后

以上就是淡定雪糕最近收集整理的关于Verilog描述——同步异步复位D触发器Verilog同步异步复位D触发器的描述的全部内容,更多相关Verilog描述——同步异步复位D触发器Verilog同步异步复位D触发器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复