基础

数制与编码

- n进制数,共有0~n-1个数,缝n进1,第i位的权重为n的

。小数点左移一位,为原来的1/n,右移一位,为原来的n倍。

- 十进制:基数为10,使用0~9,第i位权重为

。缝十进一。

- 二进制:基数为2,使用0~1,第i位权重为

。缝二进一。

- 十六进制:基数为16,使用0~9和A~F组成,第i位权重为

。缝十六进一。在小数点左边,从右至左的位权依次是:

、

...在小数点右边,从左至右的位权依次是:

、

...

- 原码:符号位(最高位)+二进制数值(后7位)

- 反码:对于正数,反码与原码相同。对于负数,保留原码符号位,其他位取反 。

- 补码:对于正数,补码与原码相同。对于负数,补码为反码+1。

- 计算机中常用补码,因为补码无重码。

- 格雷码

- BCD码:用4位二进制数来表示1位十进制数中的0~9这10个数码

逻辑代数基础

- 1 与 0 的意义并不是数字意义,而是 真(true) 与 假(false) 。

- 与运算(and)==逻辑乘:F=A⋅B 或者 F=A∧B F = A∧BF=A∧B读作 F等于A与B

-

或运算(or)==逻辑加:F=A+B 或者 F=A∨B F = A∨BF=A∨B读作 F等于A或B

- 非运算(not):F= A或者 F=¬A

- 逻辑函数:逻辑变量通过运算构成的函数。数电中,自变量为输入信号,逻辑函数表示输出信号。

- 证明逻辑等式:真值表、公式法

- 逻辑代数3个运算规则:

- 【代入规则】

- 【对偶规则:所有的“·”和“+”互换,0和1互换,得到的新的表达式为原来的对偶式】A=B,

=

- 【反演规则:所有的“·”和“+”互换,0和1互换,原变量和反变量互换,得到的新的表达式为原来的(F)反函数(

)】

- 计算次序不变,必要时加上中括号

逻辑函数的描述方式

- 真值表:通过自变量和函数的取值关系表示函数,一个确定的逻辑函数,真值表只有一个

- 表达式:通过变量和运算表达函数,一个确定的逻辑函数,表达式可以有多个

- 逻辑图:逻辑门来实现电路

- 积之和式(与-或式):若干个乘积项的逻辑加

- 最小项:特殊的乘积项,包含了所有的自变量(只出现一次)

- 最小项表达式(标准积之和式):每个乘积项都是最小项。(即:在真值表中值等于1的最小项的与或式)

- 和之积式(或-与式):若干个和项的逻辑乘

- 最大项:特殊的和项,包含了所有的自变量(只出现一次)

- 最大项表达式(标准和之积式):每个和项都是最大项。(即:在真值表中值等于0的最大项的与或式)

逻辑函数的简化

- 代数法简化

- 卡诺图简化:https://blog.csdn.net/fengmm521/article/details/78438407

组合逻辑电路分析与设计

数字电路分为组合逻辑门和时序逻辑门

集成逻辑门

- CMOS逻辑门

- TTL逻辑门

- ECL逻辑门

常用MIS组合逻辑模块

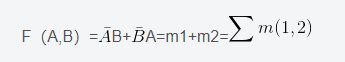

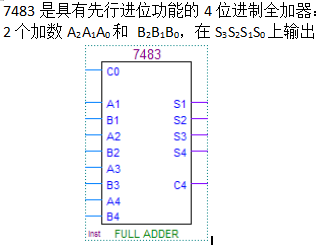

- 加法器:【半加器】加数和被加数为输入,和数与进位为输出的装置【全加器】加数、被加数与低位的进位数为输入,和数与进位为输出

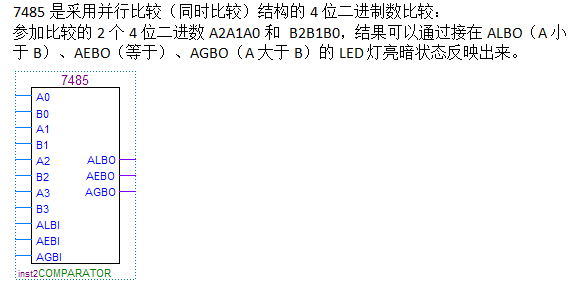

- 比较器:用于比较2个数的大小,并给出“大于”、“小于”和“等于”三种比较结果。【比较:从高位开始,逐位比较。A3~A0】

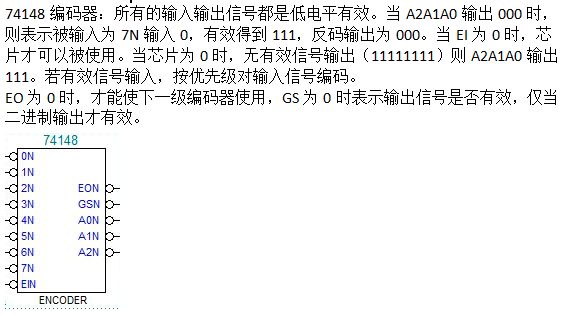

- 编码器:又叫二进制编码器。当第i个键被按下的时候,此时对应的编码输出为i的二进制值。

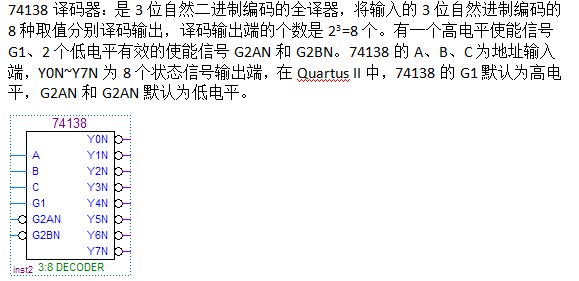

- 译码器:执行与编码器相反操作。译码是编码的逆过程,在编码时,每一种二进制代码,都赋予了特定的含义,即都表示了一个确定的信号或者对象。把代码状态的特定含义“翻译”出来的过程叫做译码,或者说,译码器是可以将输入二进制代码的状态翻译成输出信号,以表示其原来含义的电路。

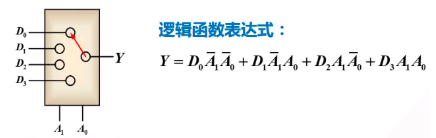

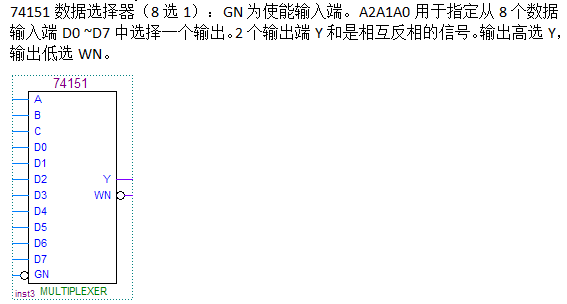

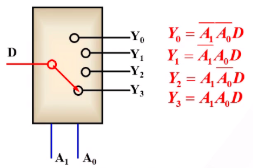

- 数据选择器: 完成从一组输入数据中选出在哪里输出。

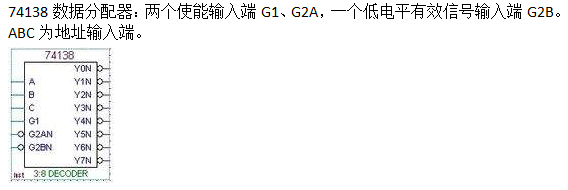

- 数据分配器:数据传输过程中,完成将数据分配到不同的数据通道上,其电路为单输入、多输出形式。

时序逻辑基础

组合逻辑电路和时序逻辑电路的重要区别就在于组合逻辑电路不存在储存电路,时序逻辑电路含有储存电路。

时序电路:输出结果与现在的输入以及储存电路有关。储存电路的值来自次态的输入。

时序逻辑概述

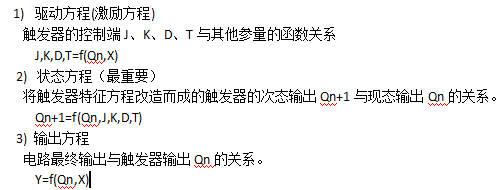

- 方程描述:输出方程组、状态方程组、次态方程组

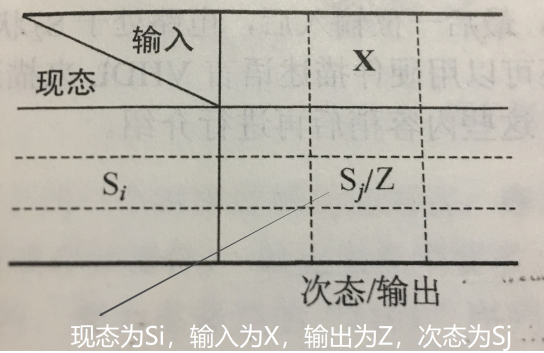

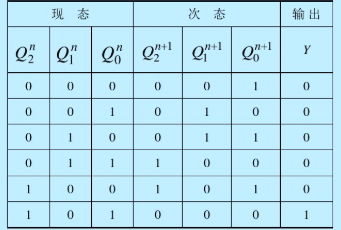

- 状态表描述:

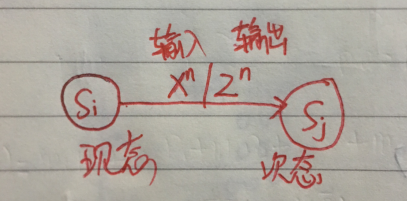

- 状态图描述

- 状态表转换为真值表

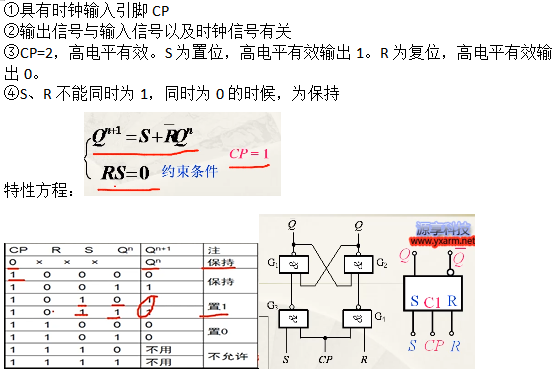

- 根据状态改变分类

- 根据输出变量的依从关系分类:【摩尔型】输出只与状态相关,与输入无关【米里型】输出不仅与状态相关,也与输入相关。

触发器:具有高电平和低电平两种稳定的输出状态

分类:

- 按照结构分

基本触发器:输入信号直接加到输入端。

同步触发器:信号经过控制门输入,控制门受CP控制

边沿触发器:只在CP的上升沿或者下降沿 ,信号才被接收 - 按逻辑功能分:RS、JK、D、T、T'

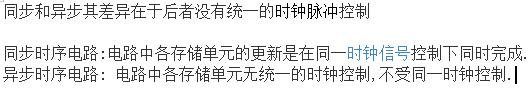

- SR基本触发器

-

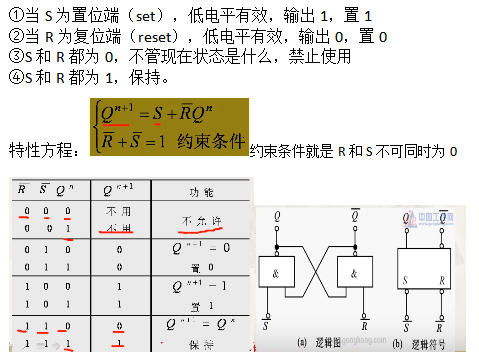

时钟控制RS触发器

-

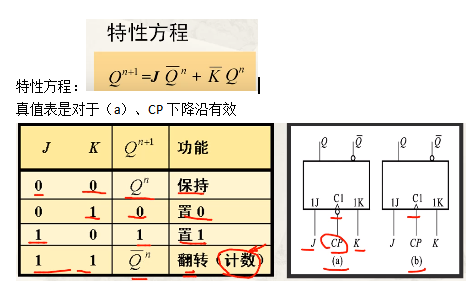

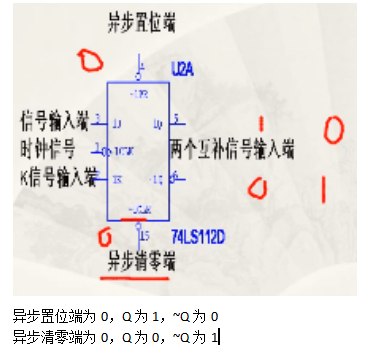

JK触发器:具有保持、置1、置0、翻转功能

-

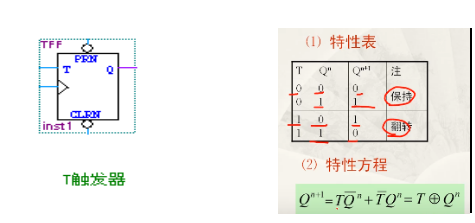

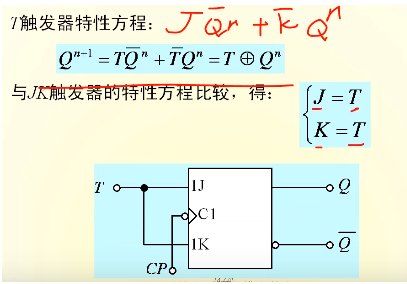

T触发器:具有保持(T=0)、翻转(T=1)功能。

-

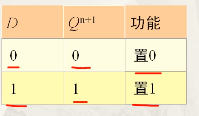

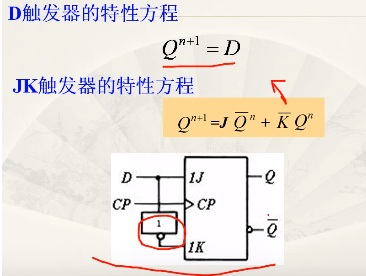

D触发器:具有置1,置0的功能。 (一般采用时钟脉冲CP上升沿触发翻转的边沿触发电路结构,D触发器是一种延迟型触发器,不管触发的现态是0还是1,CP脉冲上升沿到来后,触发器的状态都将变成与CP脉冲上升沿到来时的D端输入值相同,相当于将数据D存入了D触发器中。 )

-

JK触发器转换成T触发器,让J和K相等

-

JK触发器转换成D触发器,让J到K中加一个非门

-

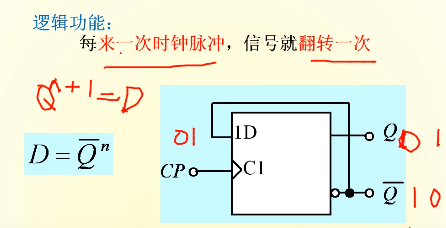

T'触发器:将T触发器的T端固定接1,则只有翻转功能

【D触发器转化为T‘触发器】

【D触发器转化为T‘触发器】

计数器

-

计数器:【定义:统计输入计数脉冲的个数电路】【结构:内部是触发器构成,1个触发器储存1位二进制数】【应用:计数、定时、分频】

-

计数器分类

-

同步计数器和异步计数器区别:①、同步计数器的外部时钟端都连在一起,而异步计数器没有。②、同步计数器在外部信号到来时触发器同时翻转,而异步计数器的触发器为串行连接。工作频率较低。③、异步计数器输出状态的建立,要比CP慢一个传输时间,容易存在竞争冒险。

-

异步计数器:异步计数器是异步时序电路,其主要特点是内部各触发器的时钟脉冲端CP不全都连接在一起,因此各触发器的翻转时刻有先有后

-

同步计数器:于同步计数器,由于时钟脉冲同时作用于各个触发器,克服了异步触发器所遇到的触发器逐级延迟问题

-

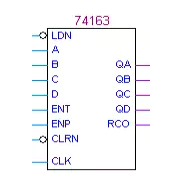

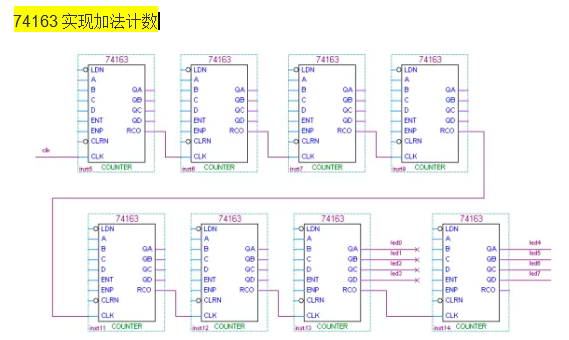

74163同步计数器:CLRN是低电平有效的同步清0信号,优先权最高。LND是低电平有效的同步置数信号。DBCA是数据输入端,QA、QB、QC、QD数据输出端。ENT、ENP为计数控制信号,同时为1则计数。

-

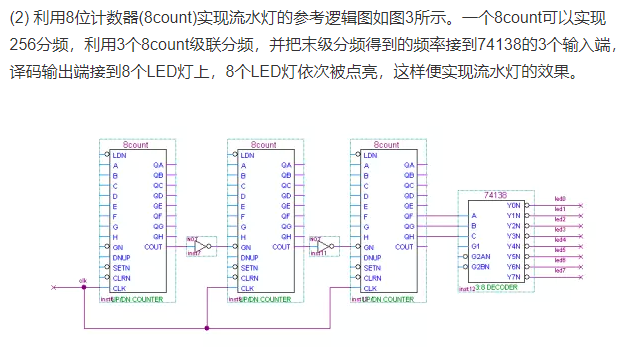

8count:一个8count可以实现256分频,【DUNP:是控制加减(默认是减法1,加法是0),CLEAR:自动清零(给0)。SETN:置1。GN:使能。LDN:锁数==置数,前提是SETN为0,才会一直是置的数】

最后

以上就是单薄盼望最近收集整理的关于数字逻辑基础的全部内容,更多相关数字逻辑基础内容请搜索靠谱客的其他文章。

发表评论 取消回复