时序逻辑电路

- 一、时序逻辑电路的基本概念

- 时序逻辑电路的模型与分类

- 时序逻辑电路模型

- 时序逻辑电路分类

- 时序电路的逻辑功能表达

- 1.由时序电路得到逻辑方程组

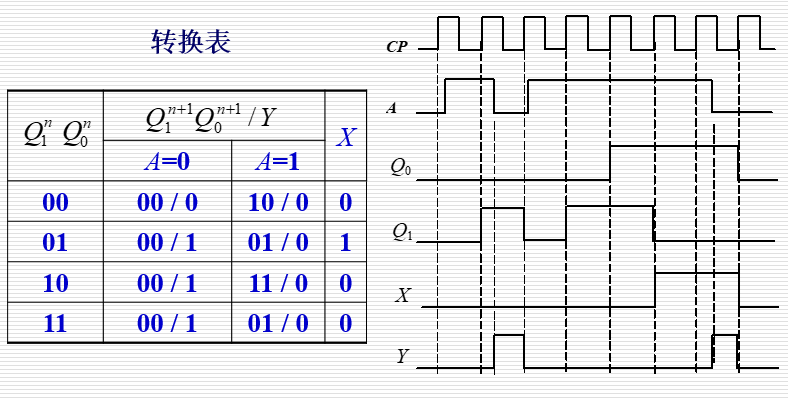

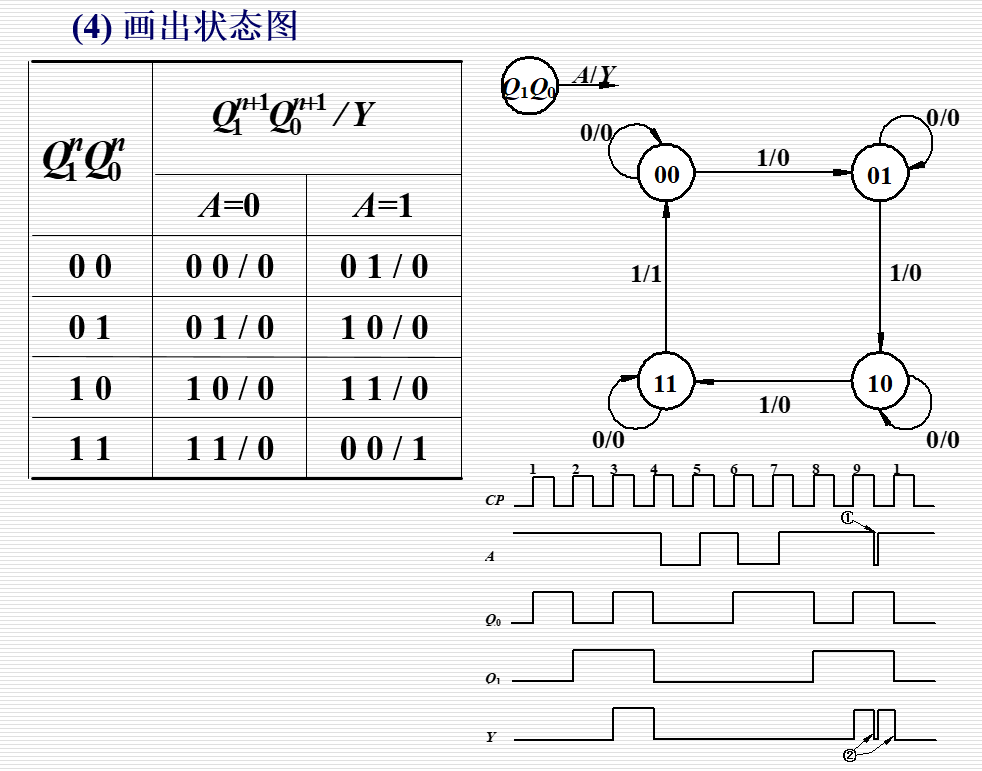

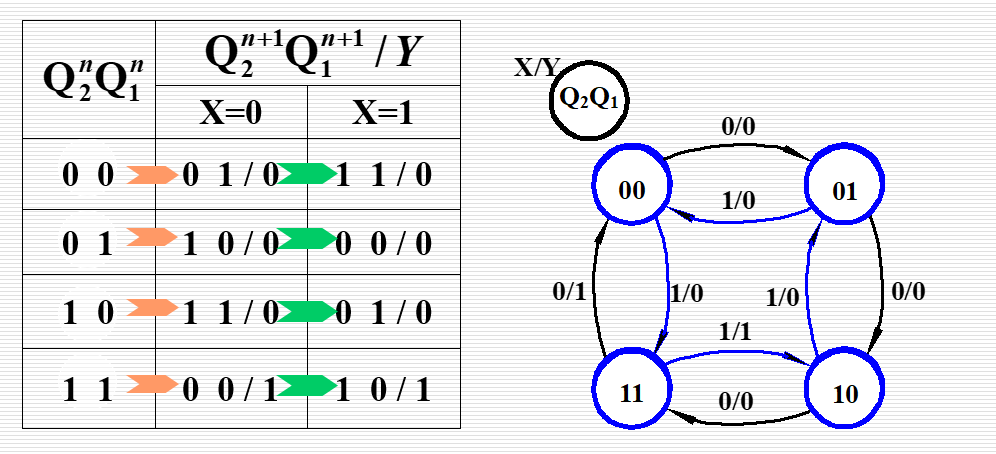

- 2.根据方程组列写状态转换真值表

- 3.将状态转换真值表变形为转换表

- 4.由转换表得状态表

- 5.由状态表画状态图

- 6.根据转换表画出伯德图

- 二、同步时序逻辑电路的分析

- 分析同步时序逻辑电路的一般步骤

- 分析举例

- 三、同步时序逻辑电路的设计

- 设计同步时序逻辑电路的一般步骤

- 设计举例

- 四、异步时序逻辑电路的分析

- 分析方法

- 分析举例

- 五、若干典型的时序逻辑电路

- 寄存器与移位寄存器

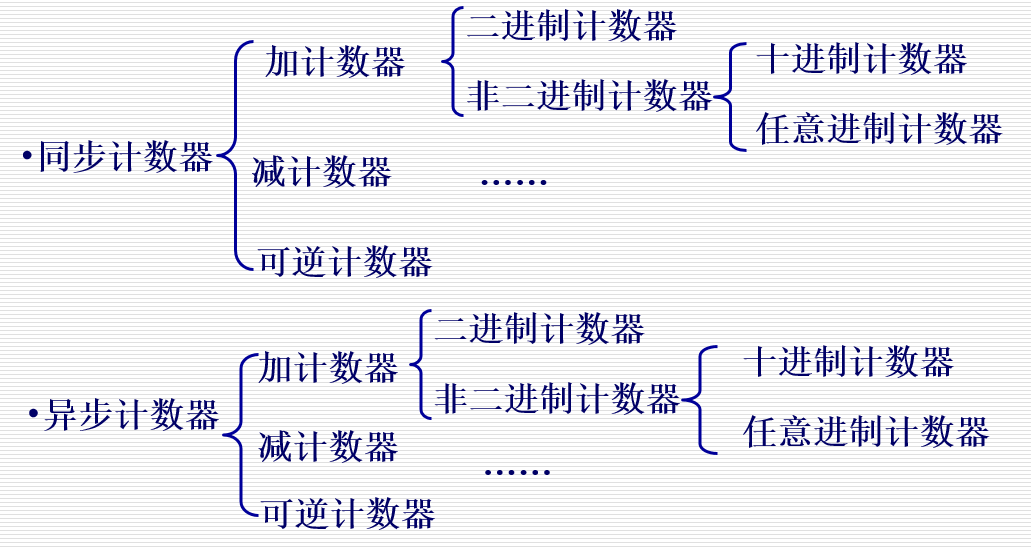

- 计数器

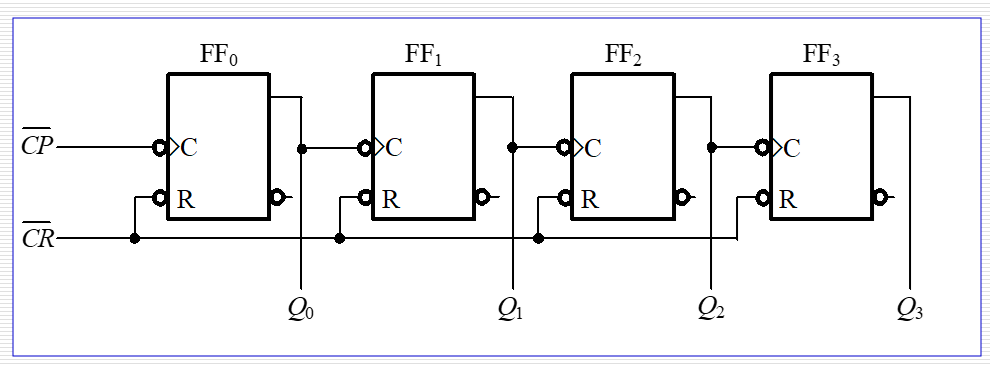

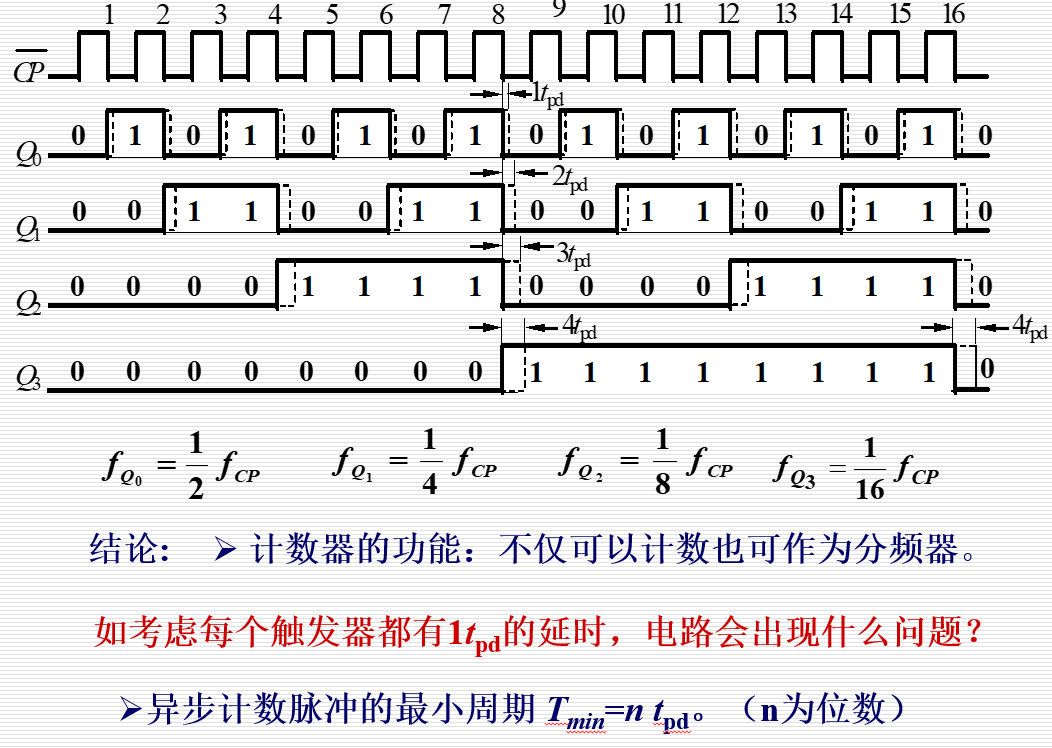

- 异步二进制计数器

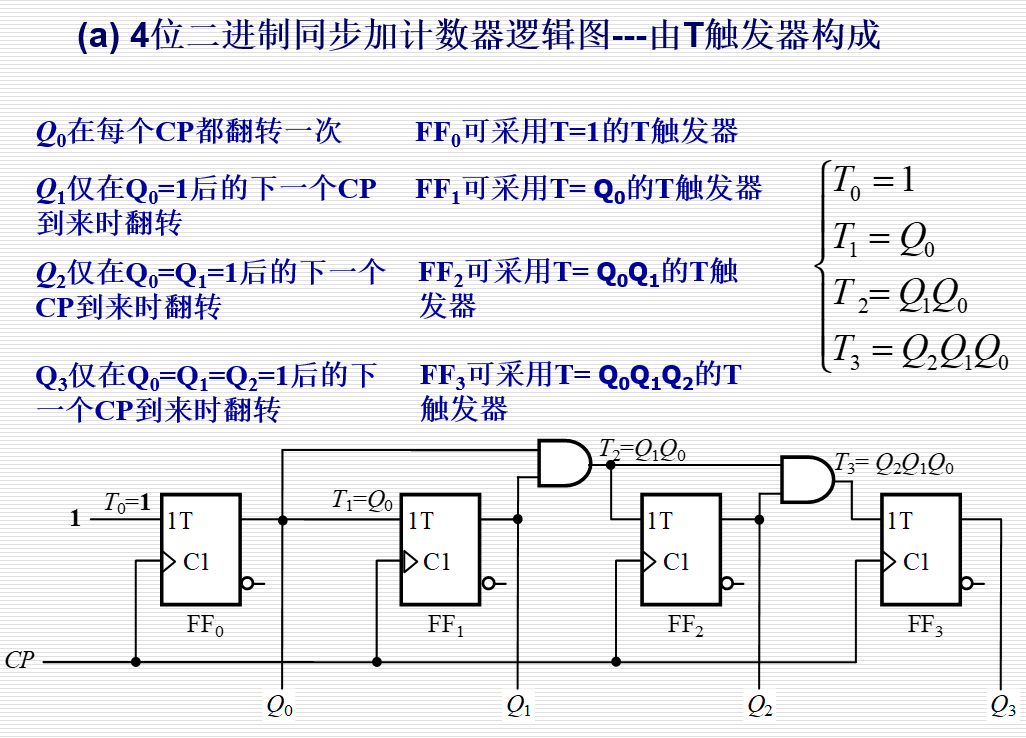

- 同步二进制计数器

学习完本节,要能回答以下问题:

- 掌握时序逻辑电路的描述方式及其相互转换

- 掌握时序逻辑电路的分析方法

- 掌握时序逻辑电路的设计方法

- 掌握典型时序逻辑电路计数器、寄存器、移位寄存器的逻辑功能及其应用

一、时序逻辑电路的基本概念

时序逻辑电路的模型与分类

时序逻辑电路模型

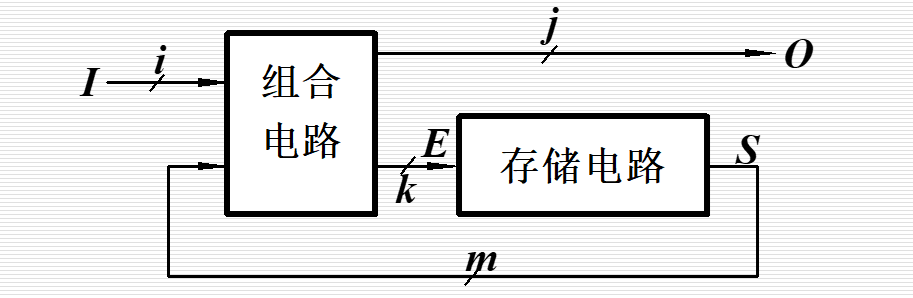

时序电路由存储电路与组合电路构成,电路存在反馈,其一般化模型如下所示:

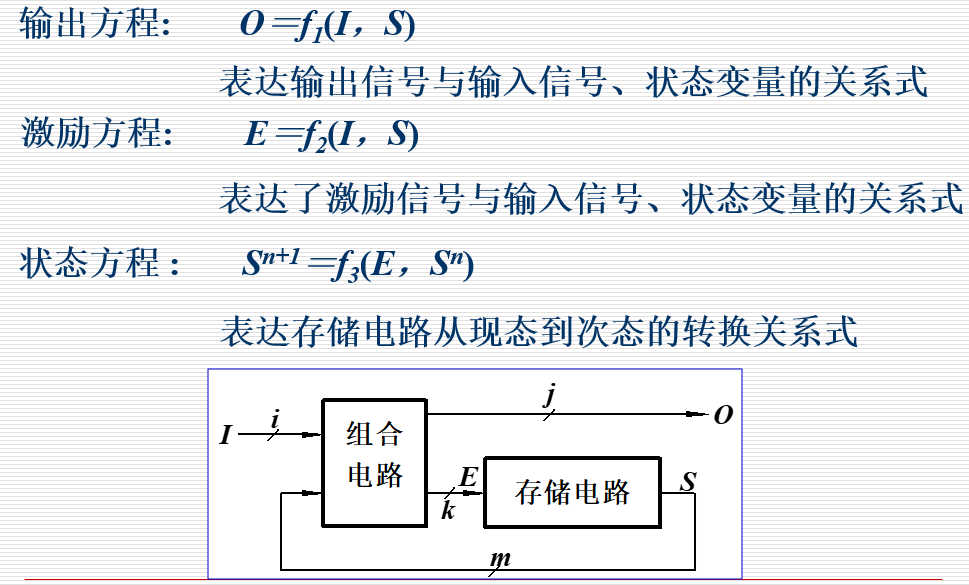

一般化模型对应三个电路方程:

一般化模型对应三个电路方程:

时序逻辑电路分类

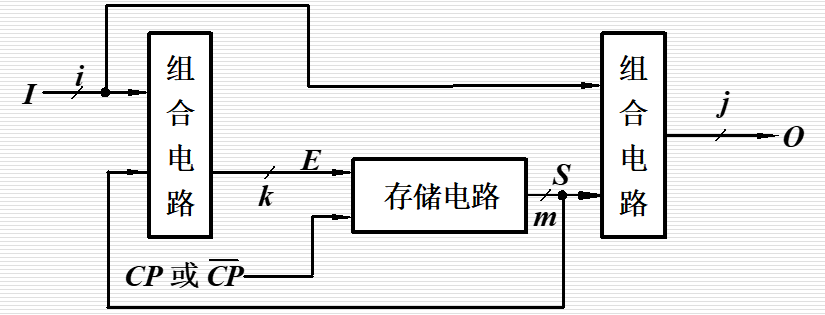

按照时序脉冲分为同步与异步:

- 同步:存储电路例所有触发器有一个统一的时钟源,它们的状态在同一时刻更新

- 异步:没有统一的时钟脉冲,电路的状态更新不是同时发生的

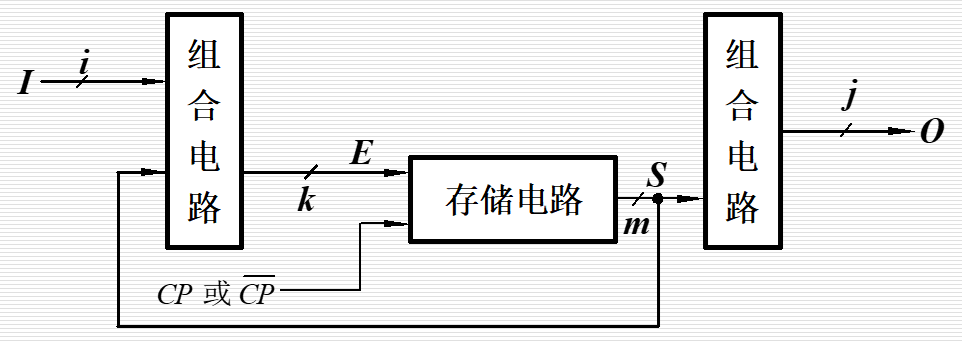

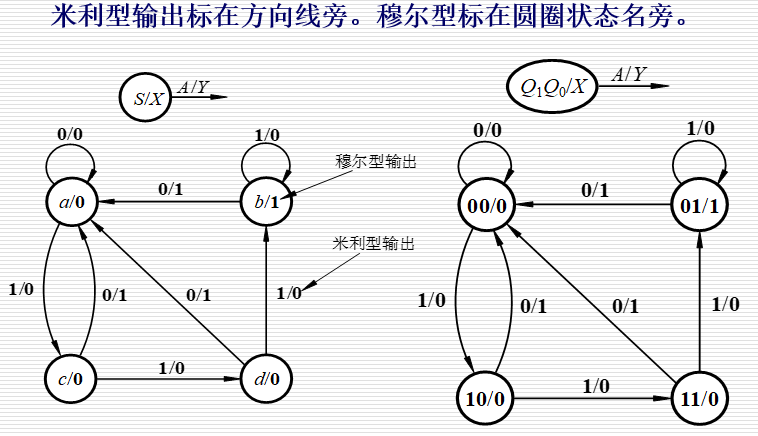

按照电路结构分为米利型电路和:

- 米利型电路:电路的输出与输入变量和触发器的输出有关。

- 穆尔型电路:电路的输出只取决于个触发器的状态。

时序电路的逻辑功能表达

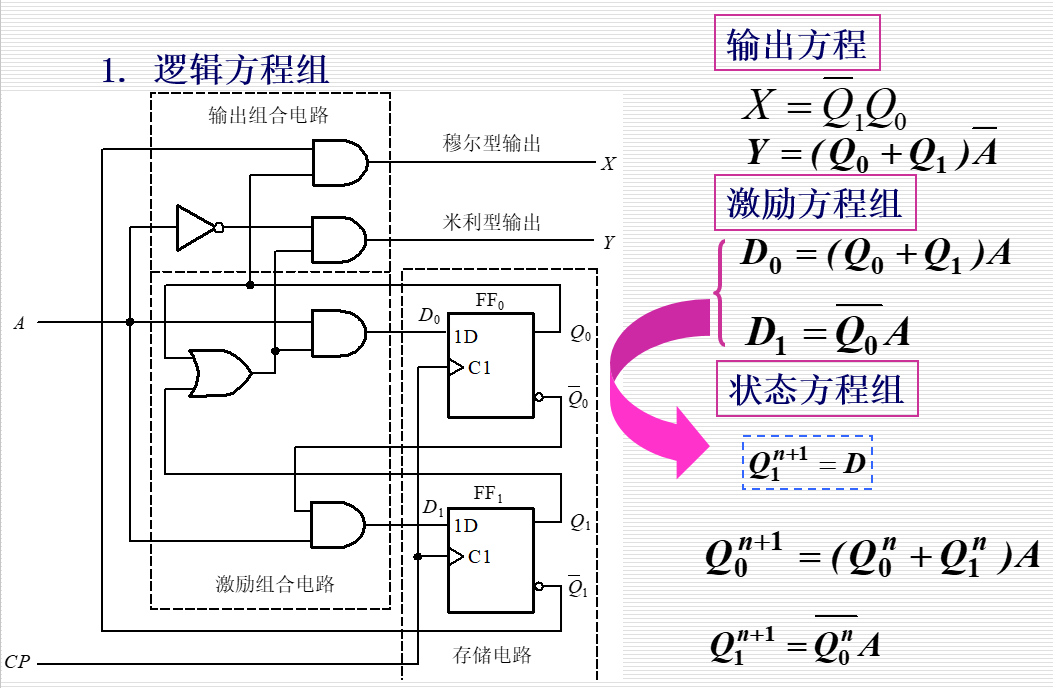

1.由时序电路得到逻辑方程组

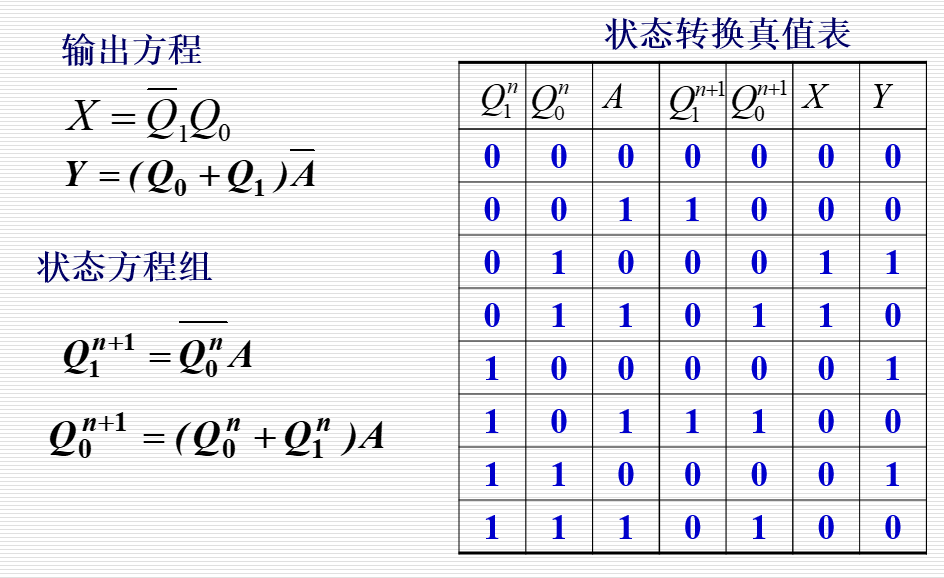

2.根据方程组列写状态转换真值表

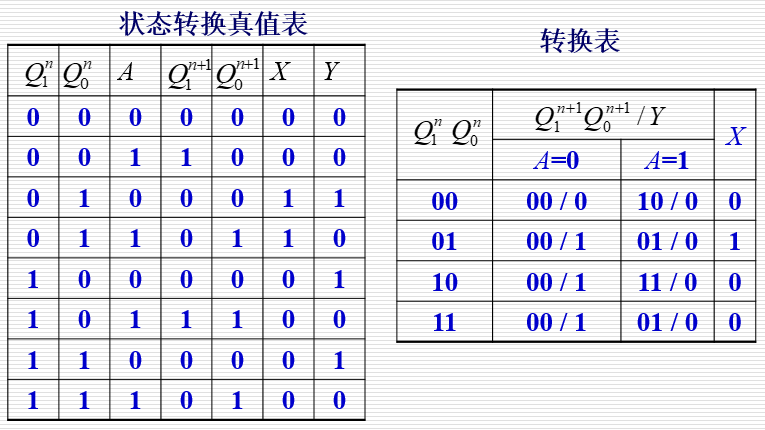

3.将状态转换真值表变形为转换表

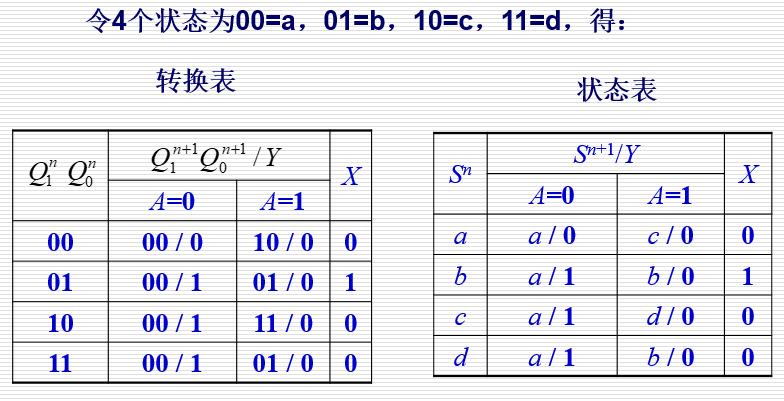

4.由转换表得状态表

5.由状态表画状态图

6.根据转换表画出伯德图

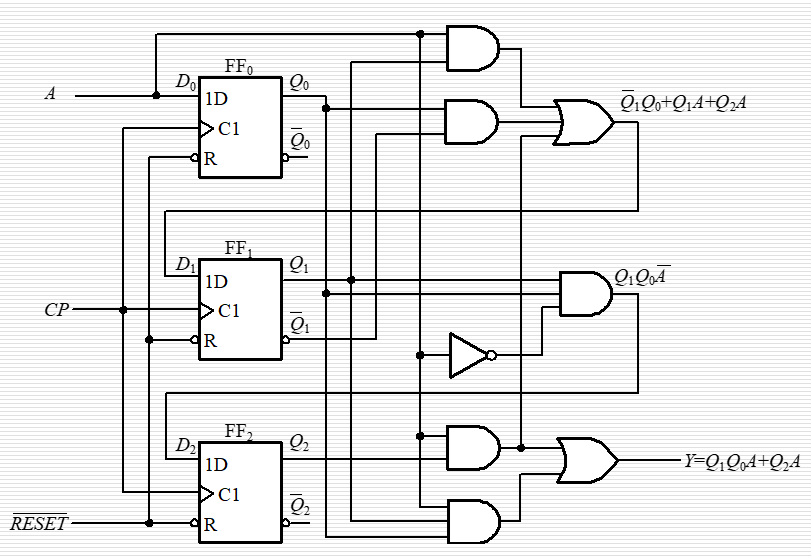

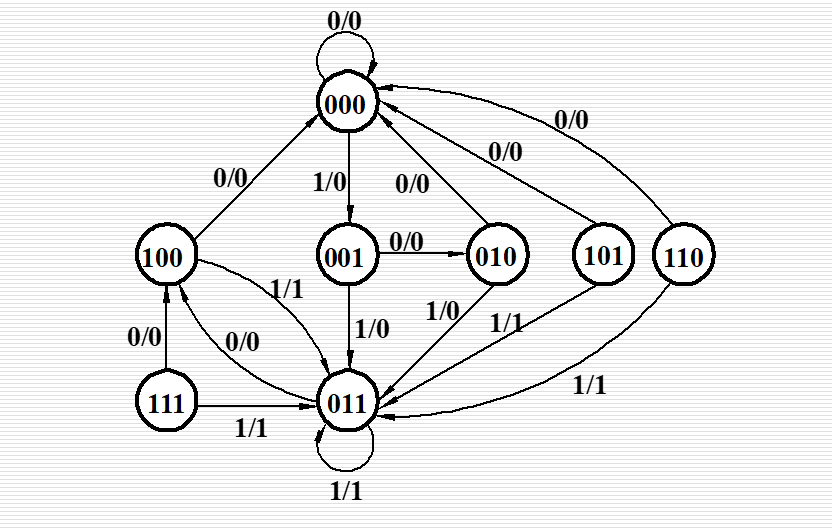

二、同步时序逻辑电路的分析

分析同步时序逻辑电路的一般步骤

时序逻辑电路分析的任务:分析电路在输入信号的作用下,其状态和输出信号变化的规律,列写出电路状态或画出状态图、工作波形图,进而确定电路的逻辑功能。

时序逻辑电路的一般步骤

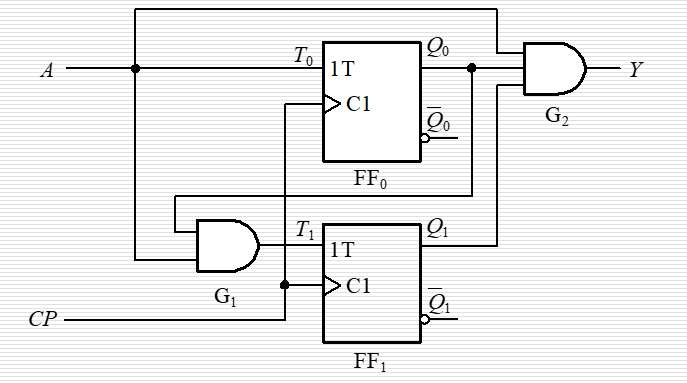

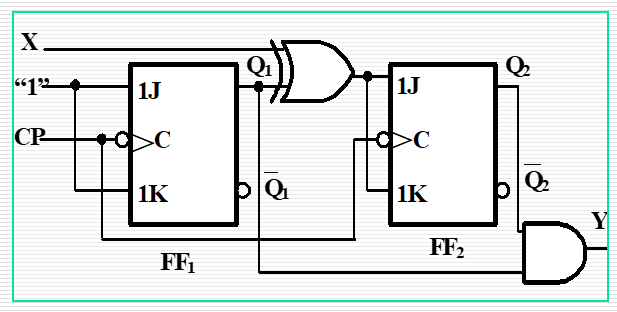

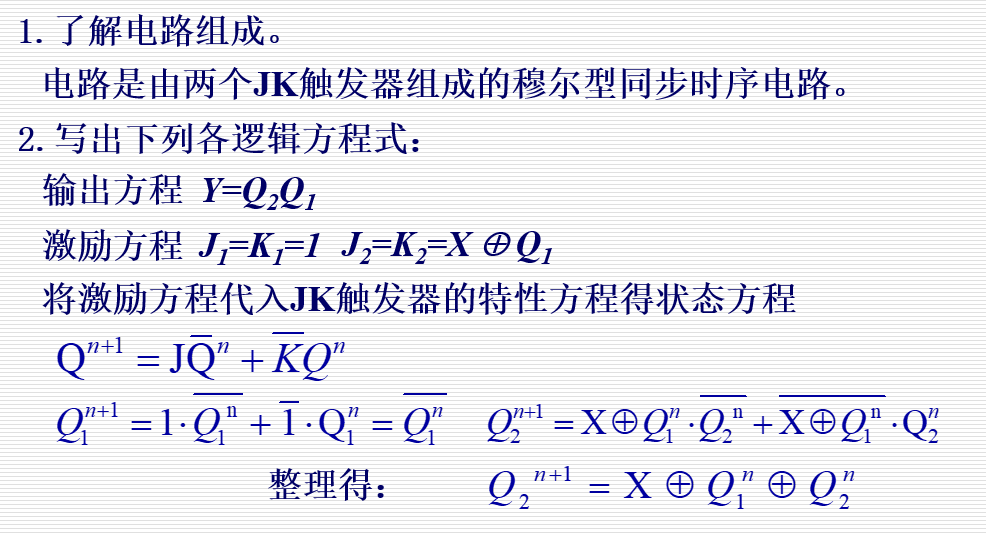

- 了解电路的组成:电路的输入、输出信号、触发器的类型

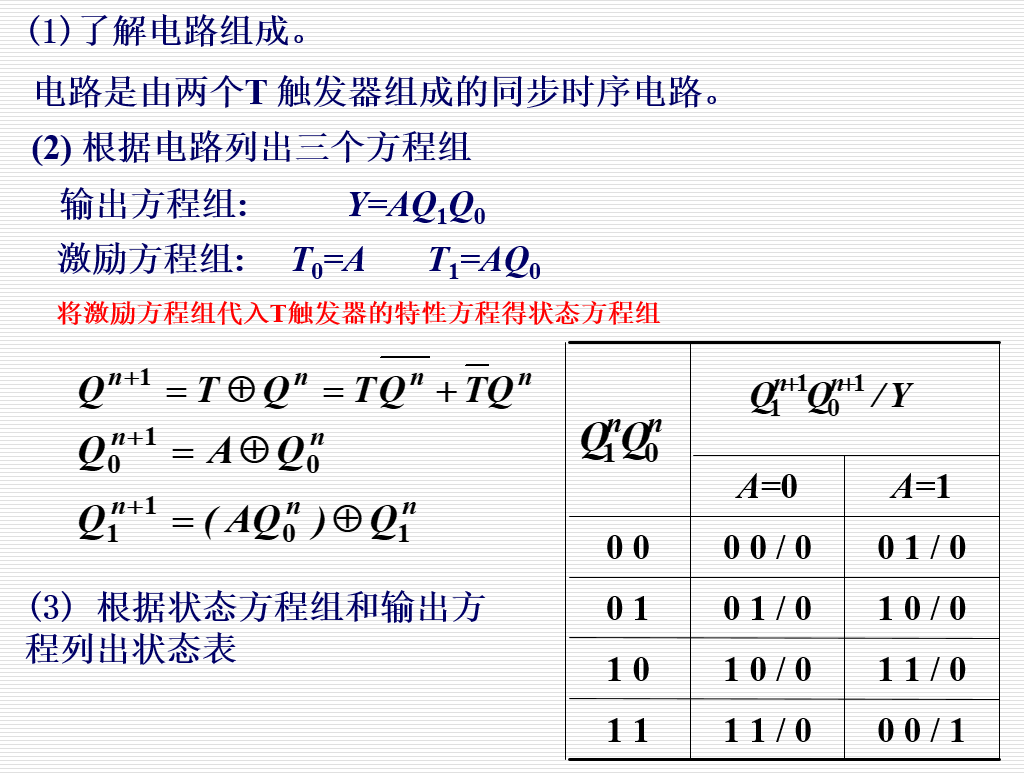

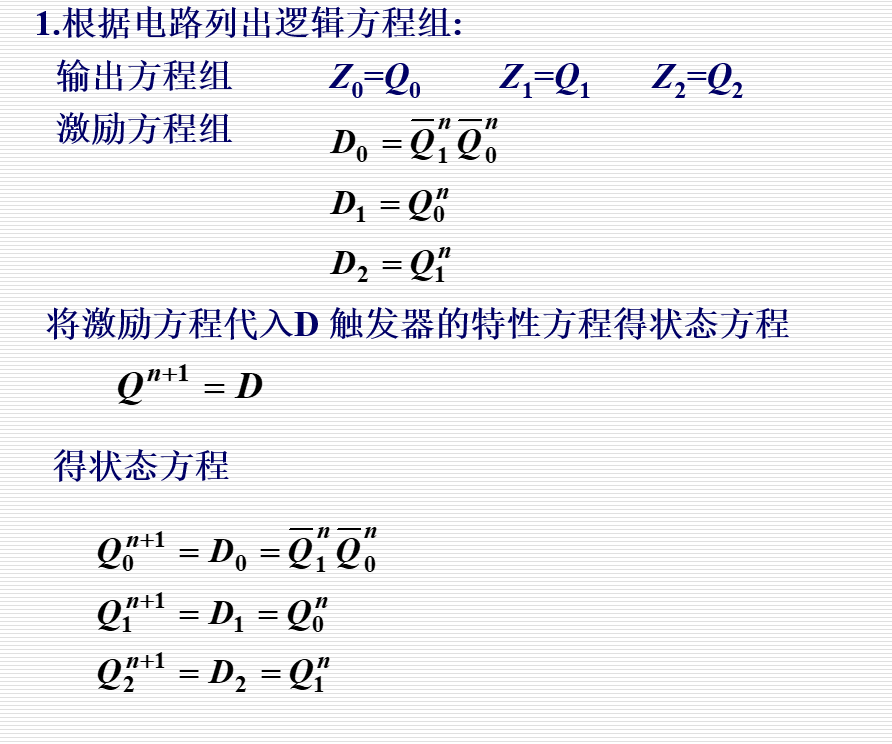

- 根据给定的电路图,列写电路的输出方程、各触发器的激励方程、状态方程(联立激励方程与触发器的自身特性得到)

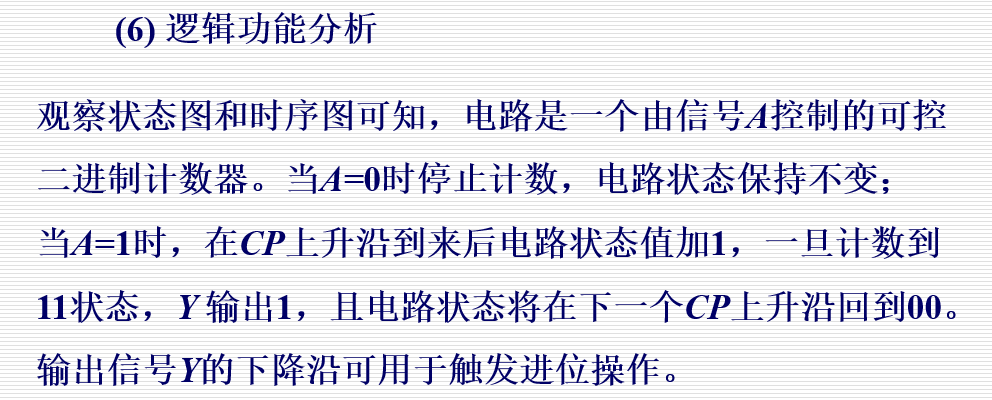

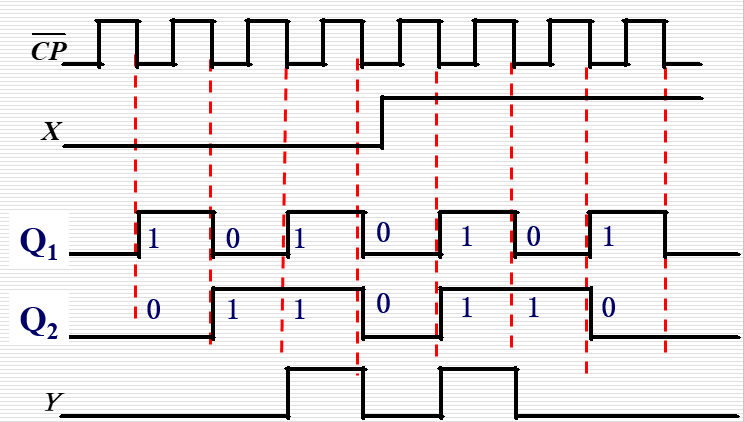

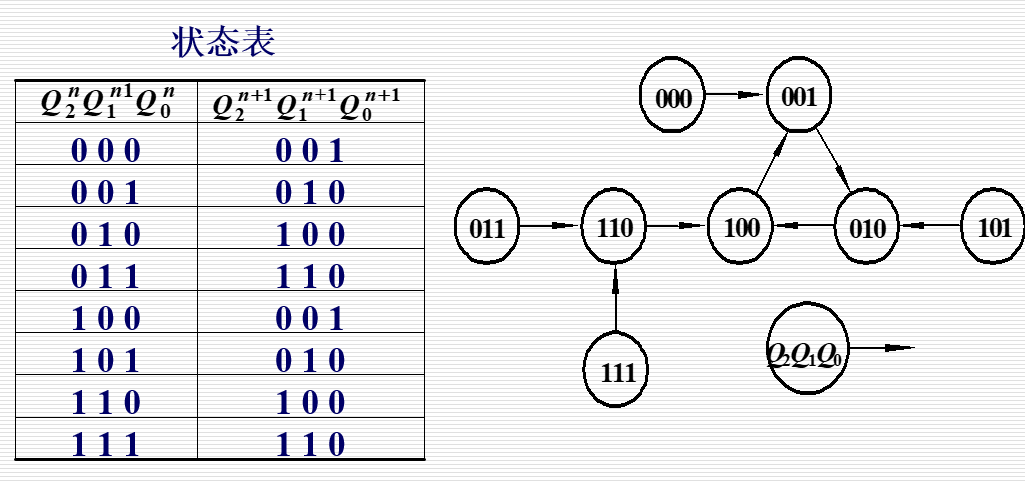

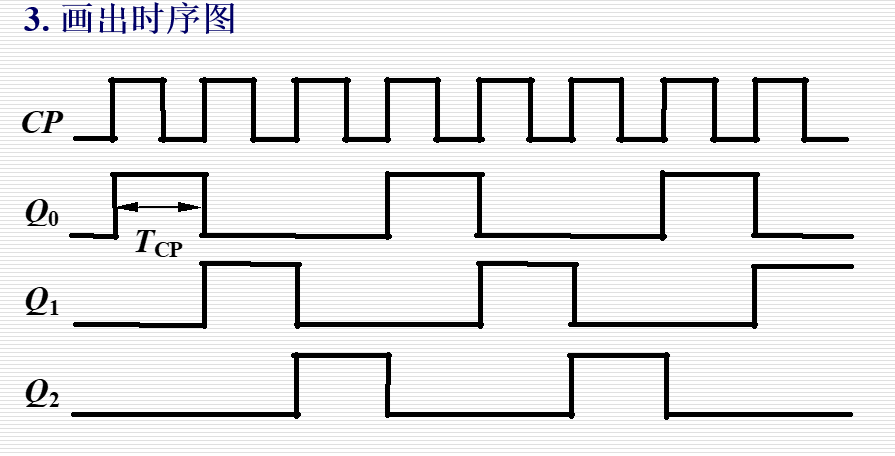

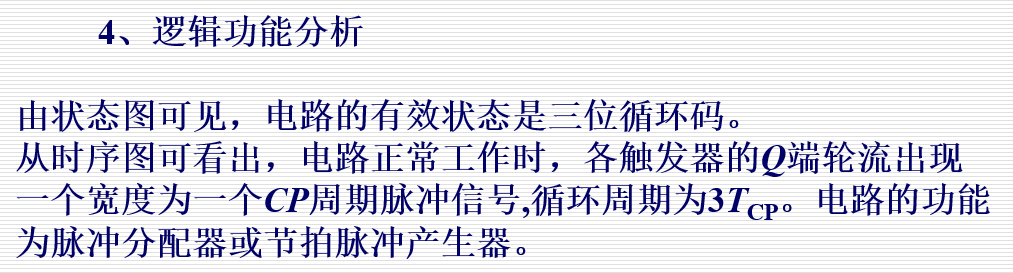

- 列写状态转换表、画出状态图和波形图

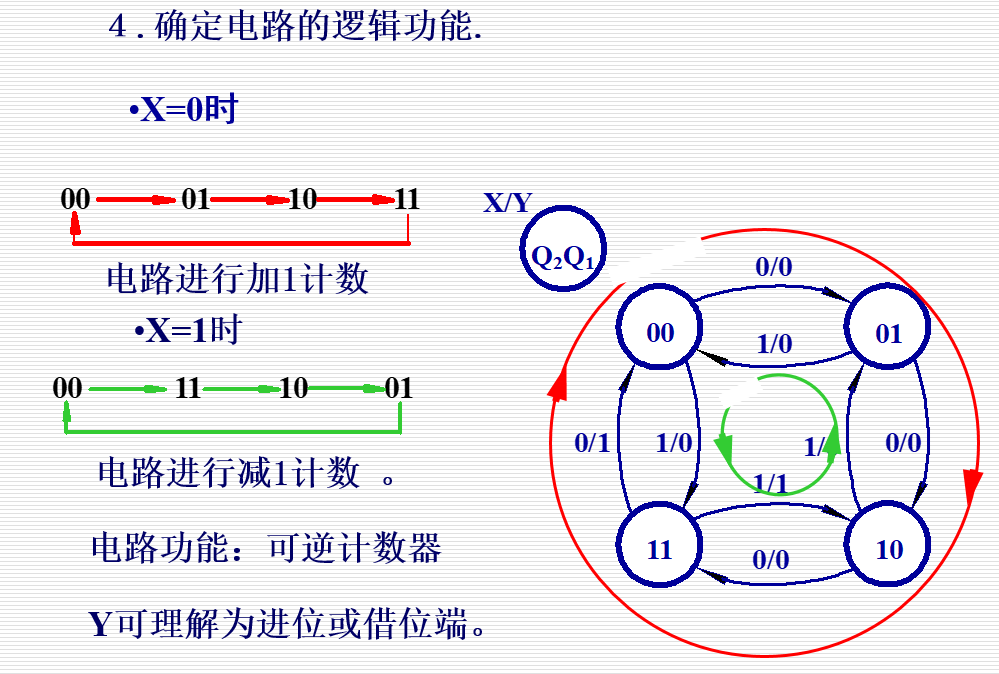

- 确定电路的逻辑功能。

分析举例

-

例题一

-

例题二

-

例题三

三、同步时序逻辑电路的设计

设计同步时序逻辑电路的一般步骤

- 根据给定的逻辑功能建立原始状态图和原始状态表

- 明确电路的输入条件和相应的输出要求,分别确定输入变量

和输出变量的数目和符号 - 找出所有可能的状态和状态转换之间的关系

- 根据原始状态图建立原始状态表

- 明确电路的输入条件和相应的输出要求,分别确定输入变量

- 化简状态,合并等价状态,消去多余状态,求出最简状态图

- 等价状态是指相同输入下有相同的输出,并转换到同一个次态去的两个状态

- 给每一个状态赋予二进制代码,根据状态数确定触发器的个数。

- 选择触发器的类型

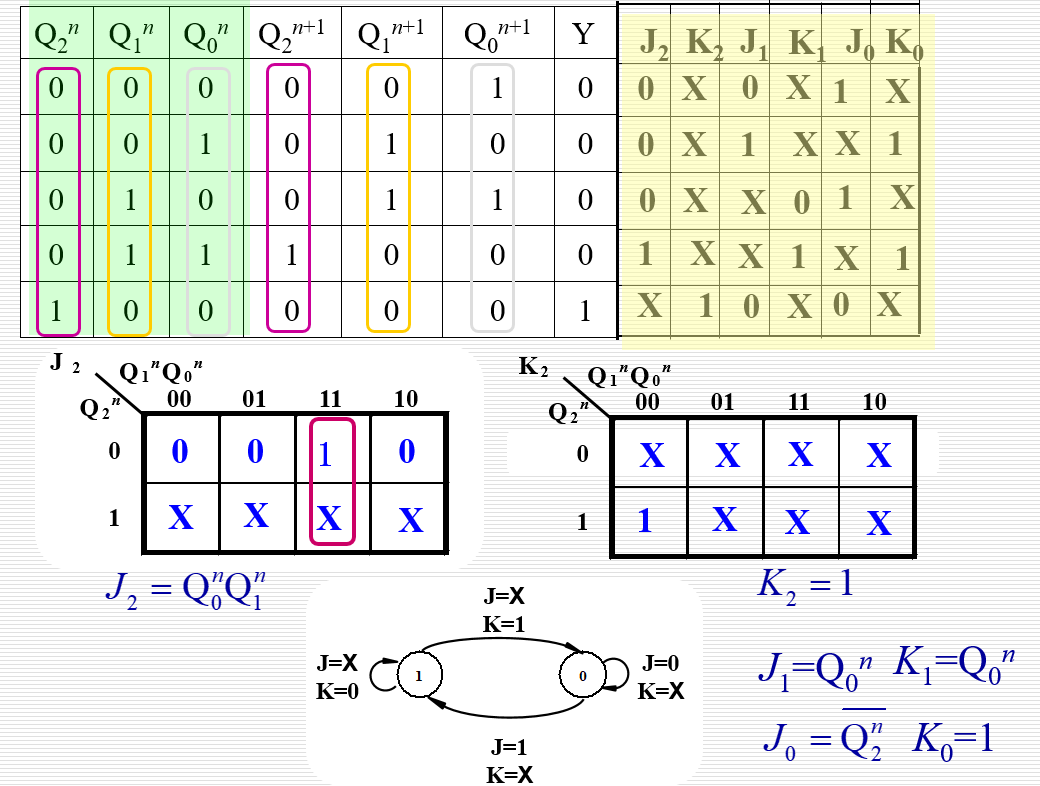

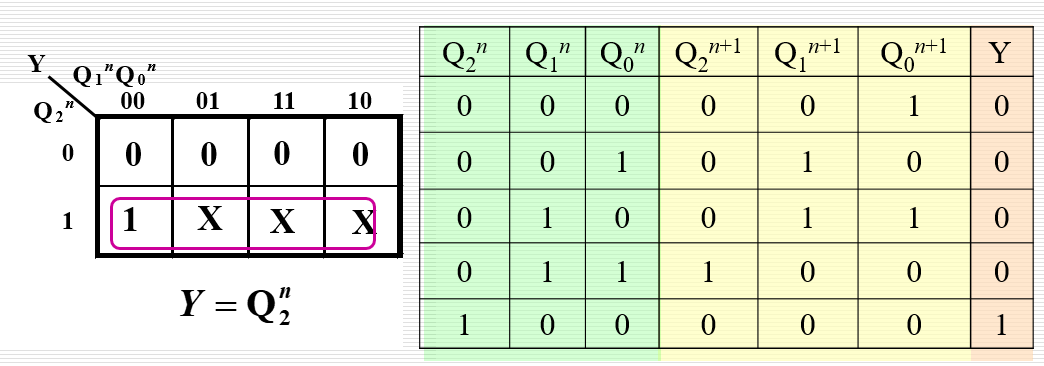

- 求出电路的激励方程和输出方程

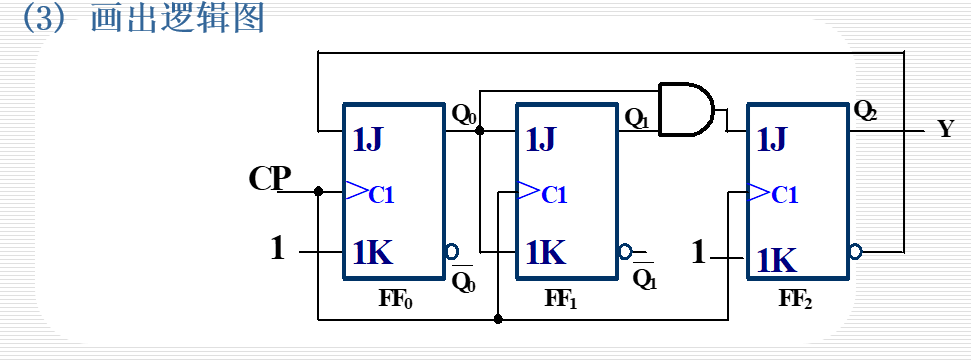

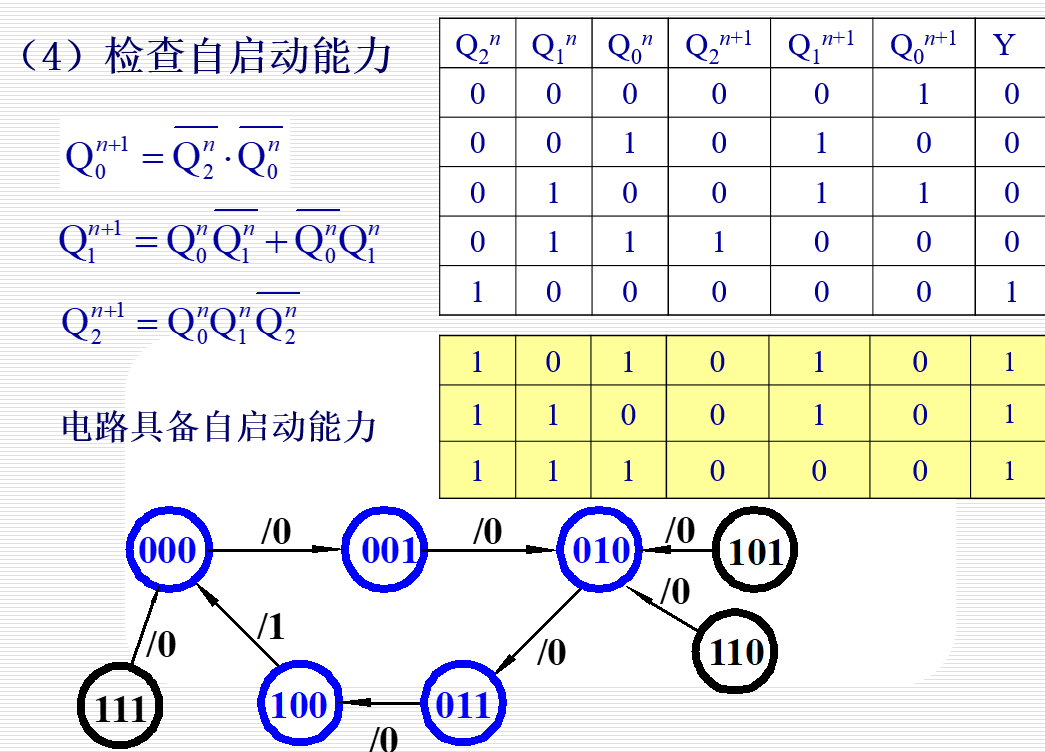

- 画出逻辑图并检查自启动能力

设计举例

例子一、用D触发器设计一个8421BCD码同步十进制加计数器

步骤1、列写原始状态表

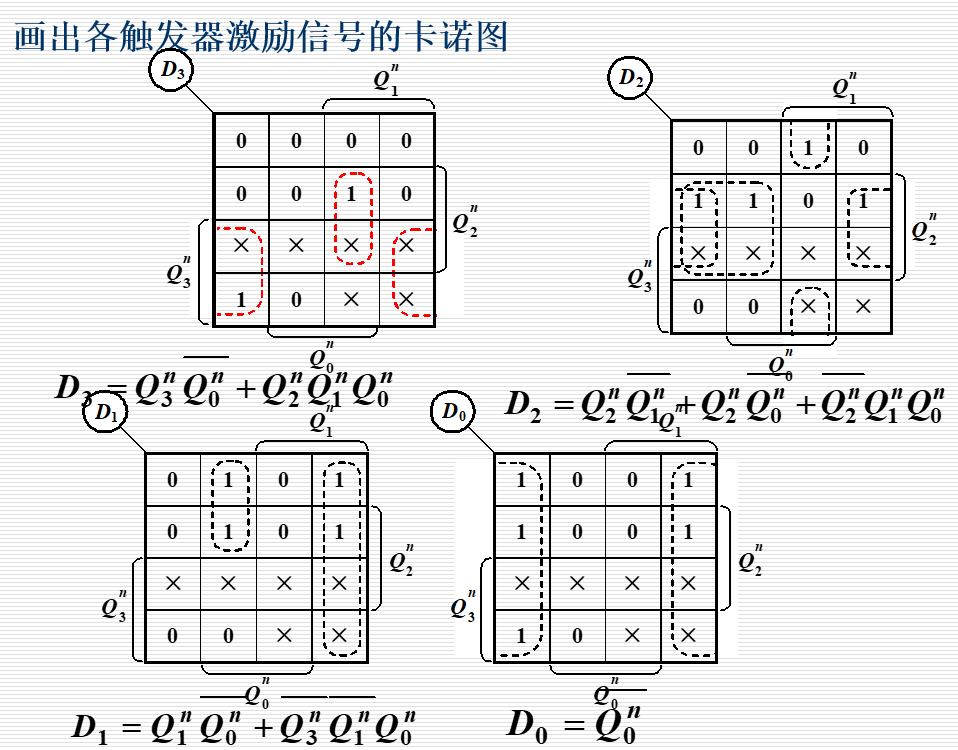

步骤二、求解电路的激励方程(通过卡诺图求解最简表达式)

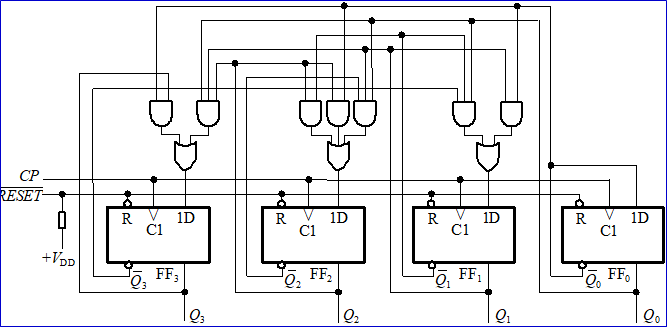

步骤三、画出逻辑图

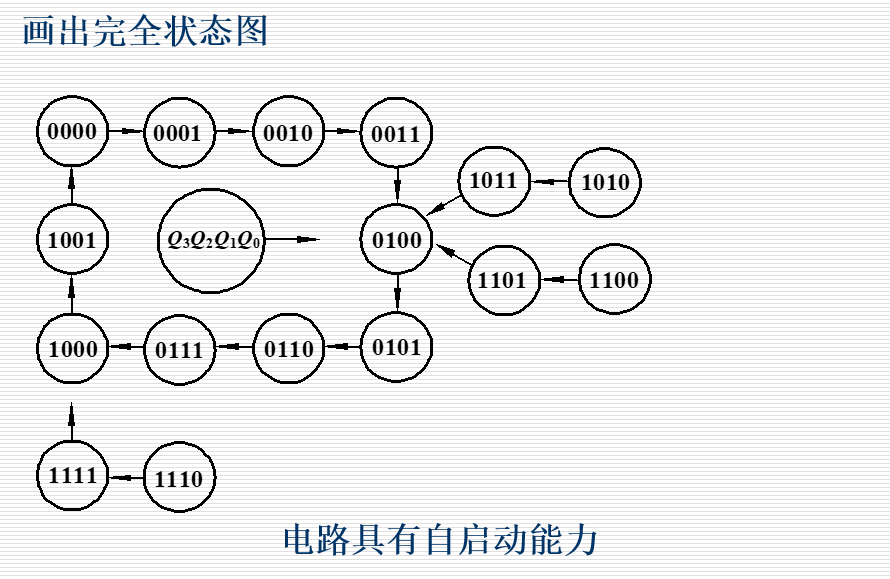

步骤四、检查电路自启动能力

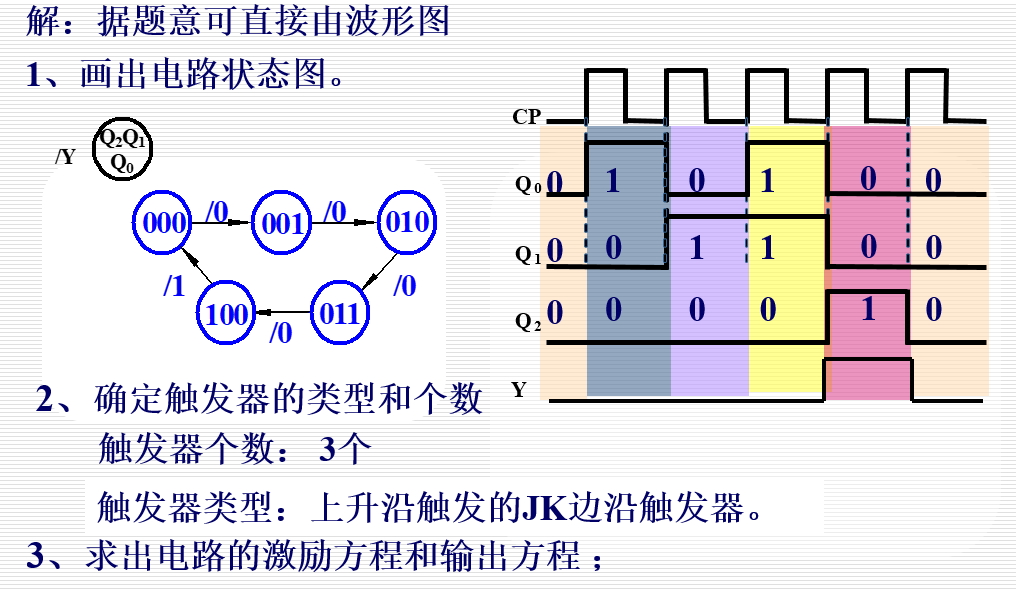

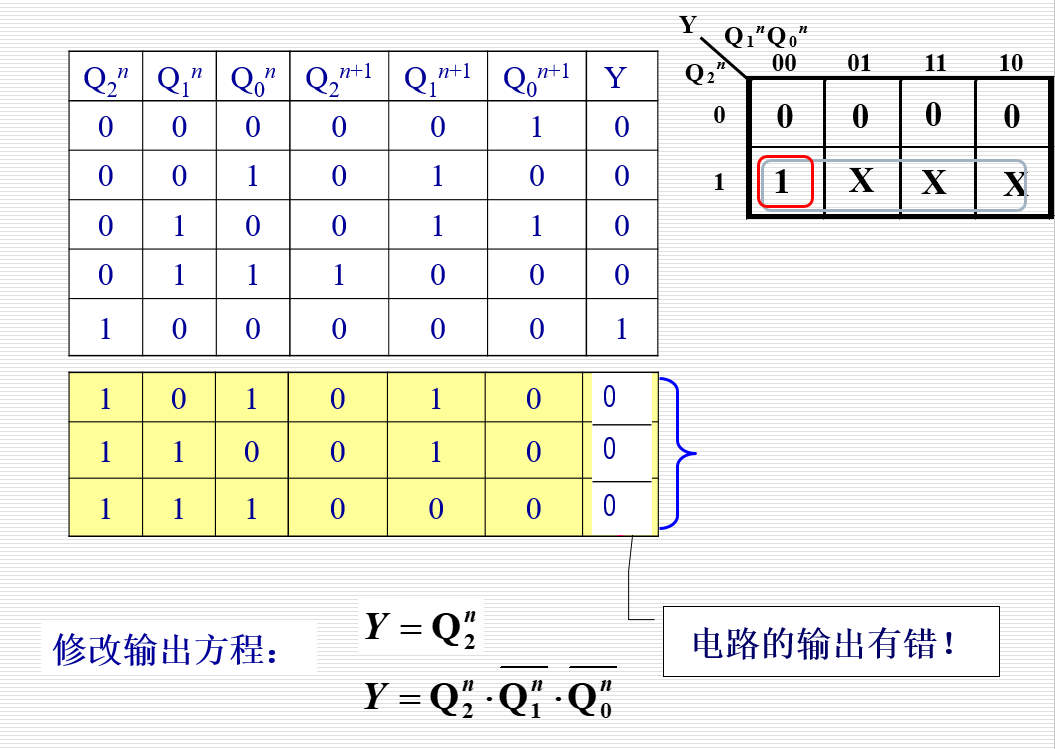

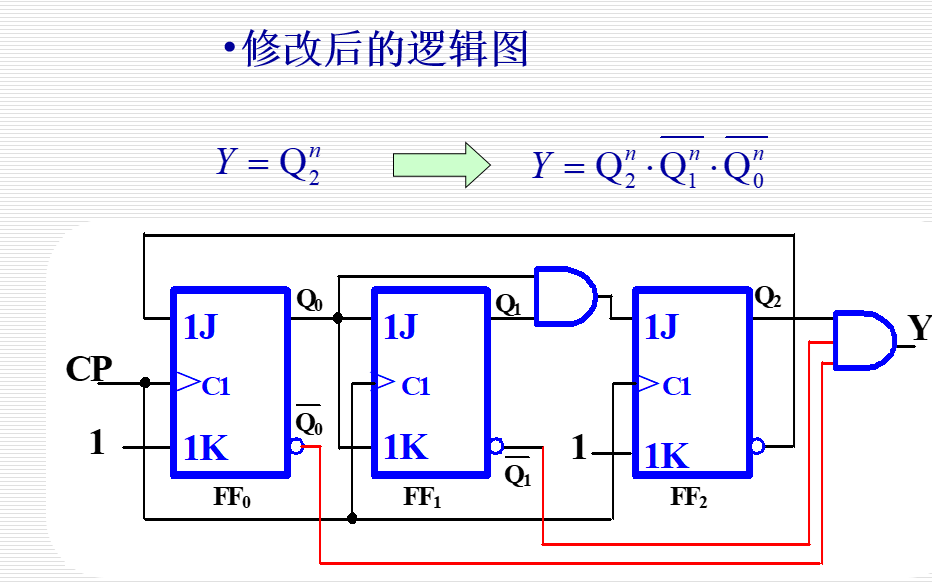

例子二、试设计一个同步时序电路,要求电路中触发器Q0、Q1、Q2及输出Y端的信号与CP时钟信号波形满足下图所示的时序关系。.

设计以外的状态产生了意外输出,需要修正。

设计以外的状态产生了意外输出,需要修正。

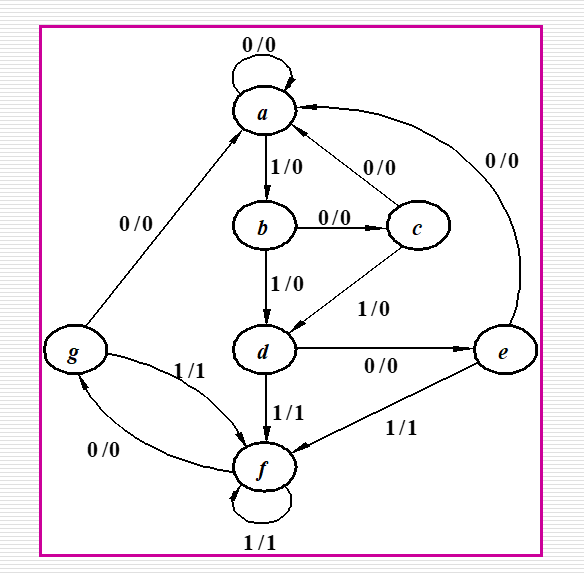

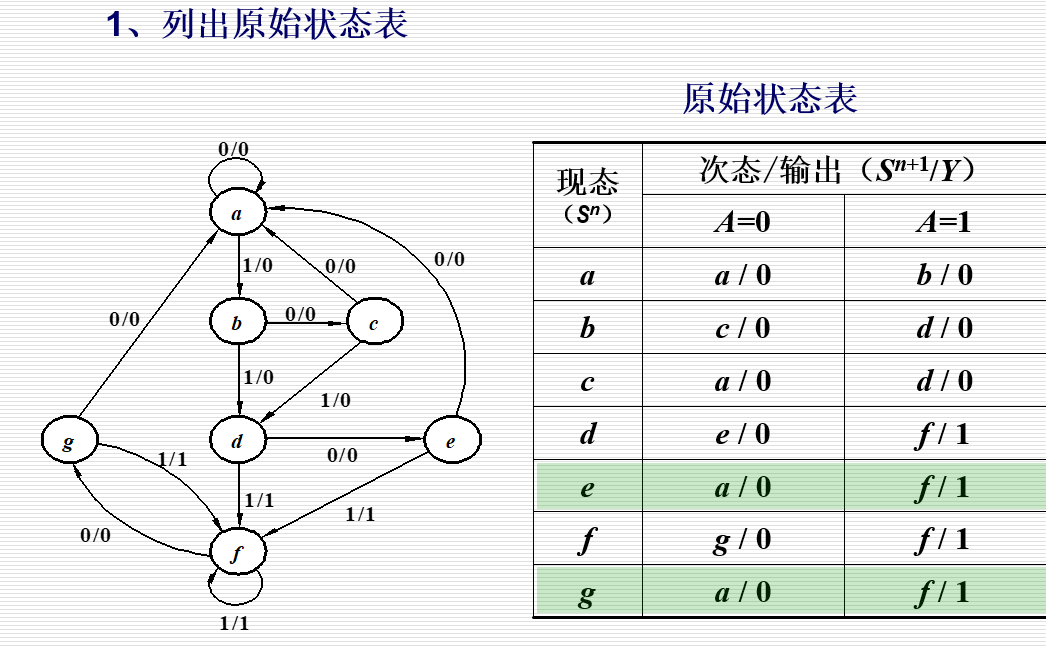

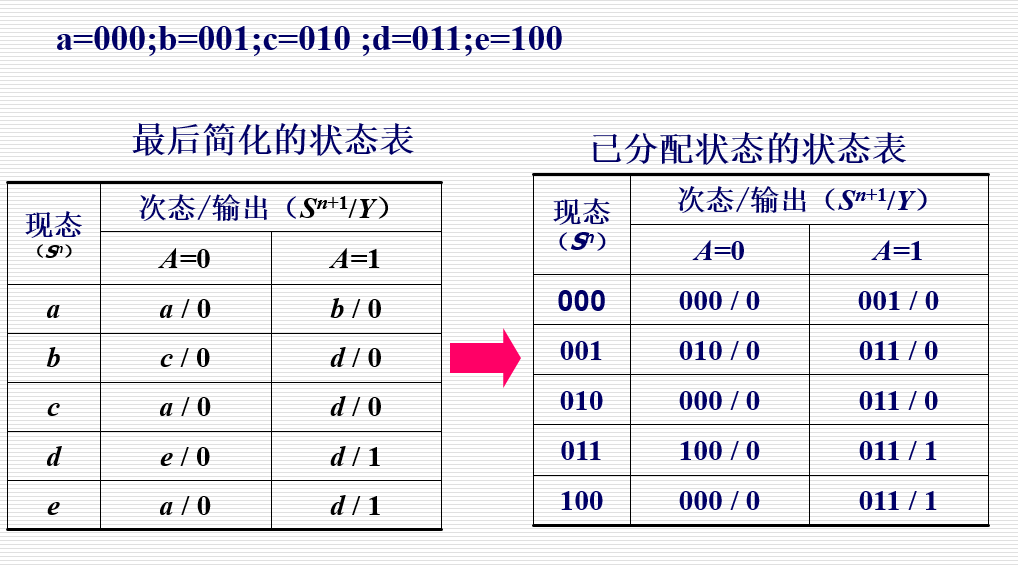

例子三、用D触发器设计状态变化满足以下状态图的时序逻辑电路

步骤一、列写原始状态表,合并等价状态

步骤一、列写原始状态表,合并等价状态

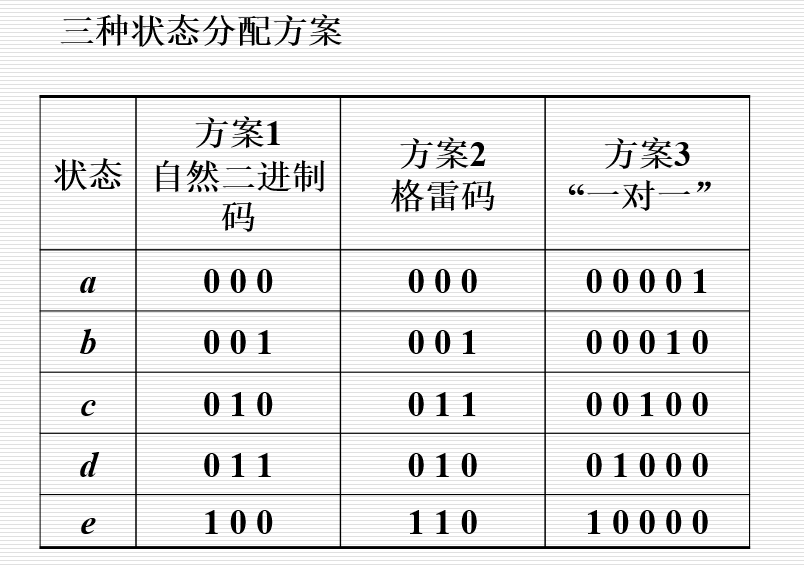

步骤二、给状态编码。编码形式可自行选择

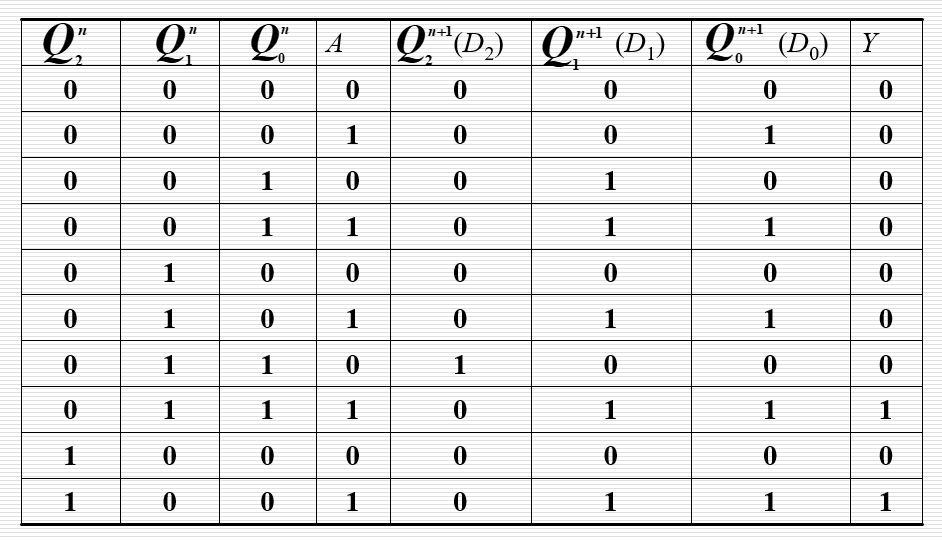

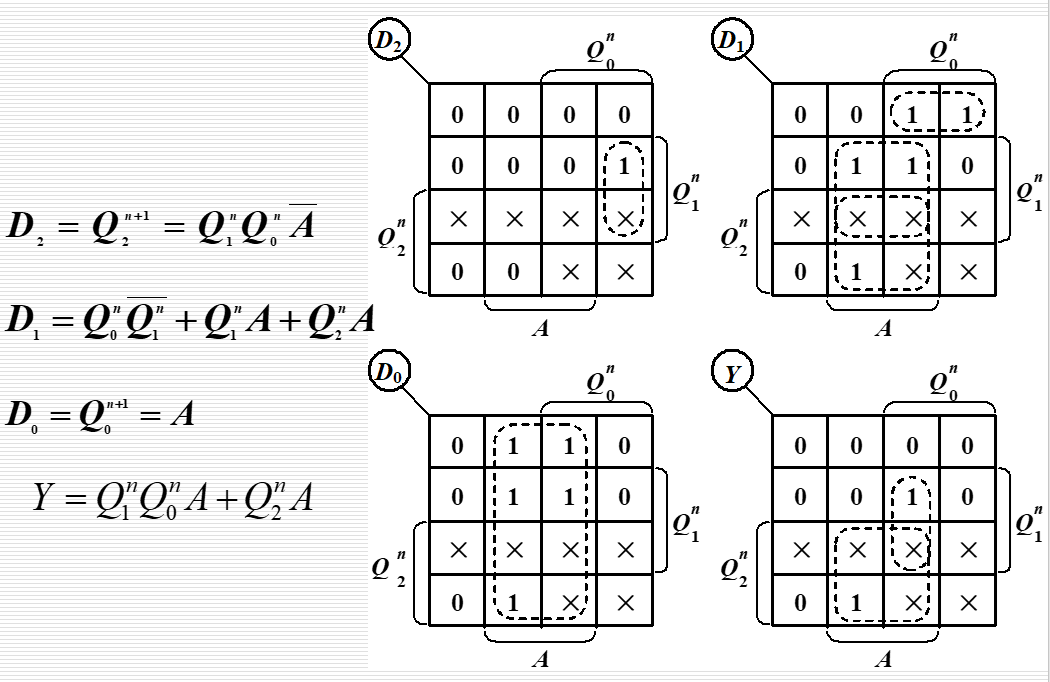

步骤三、根据状态转换真值表,求解激励方程与输出方程

步骤四、绘制时序电路

步骤五、检查自启动能力

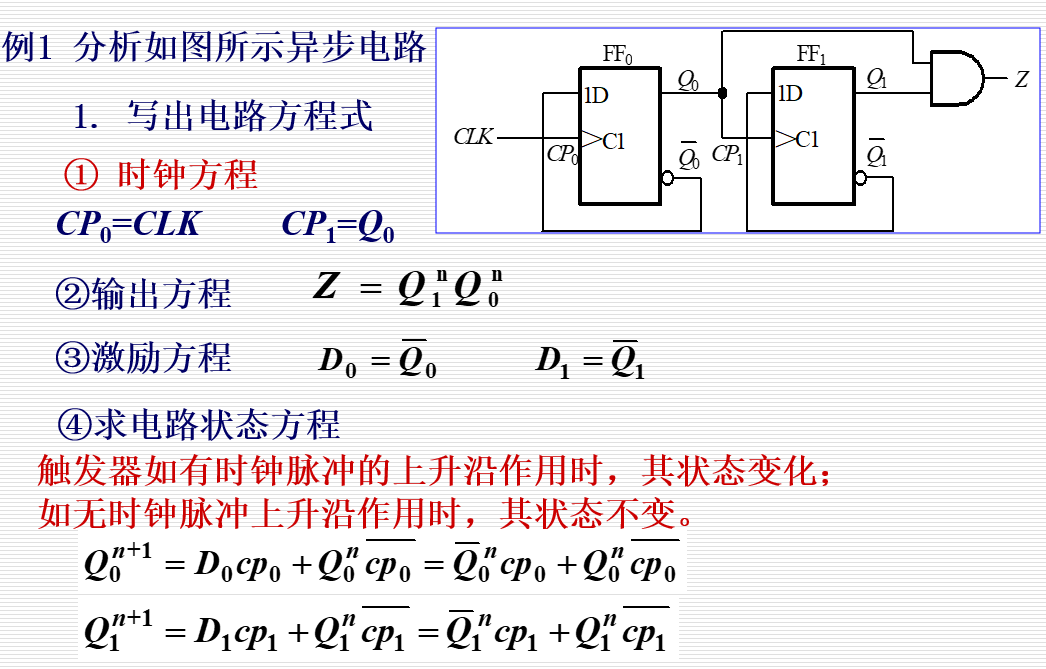

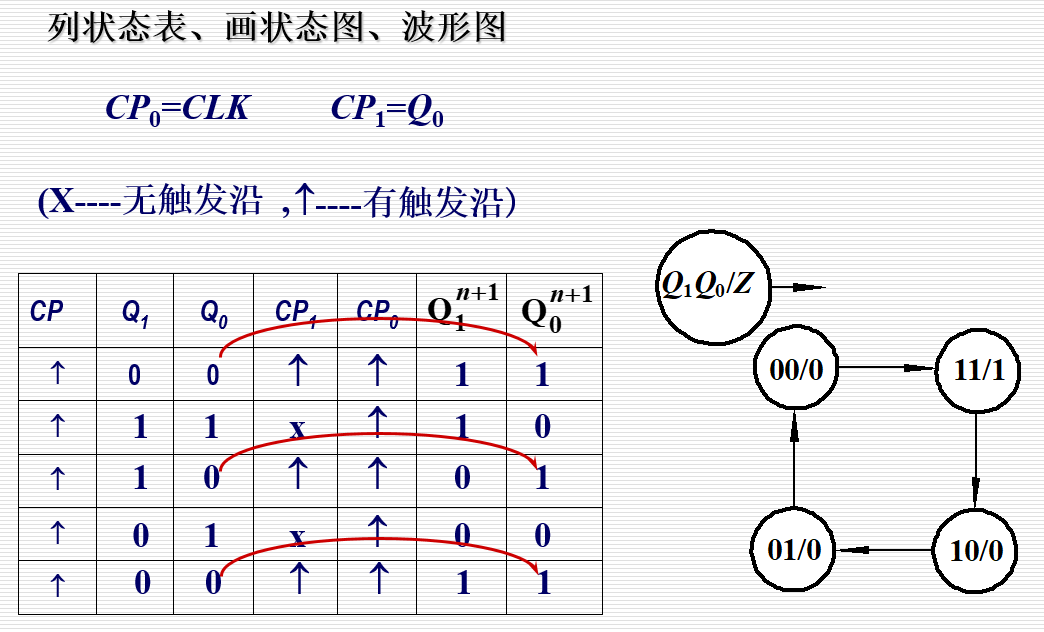

四、异步时序逻辑电路的分析

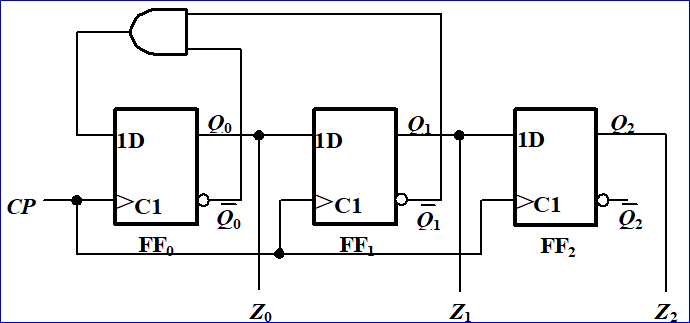

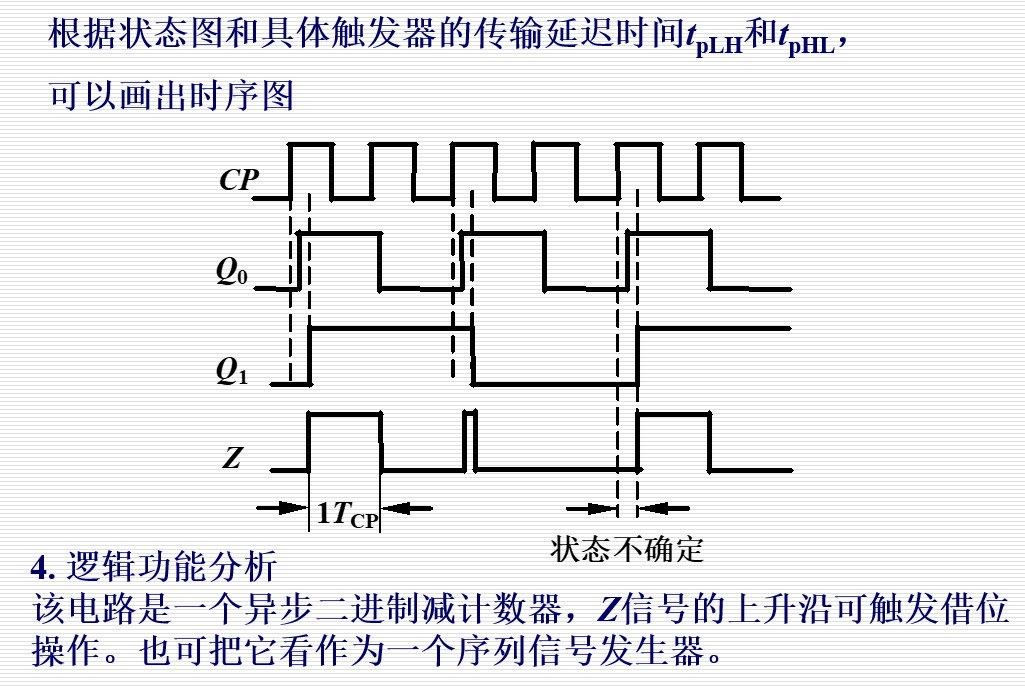

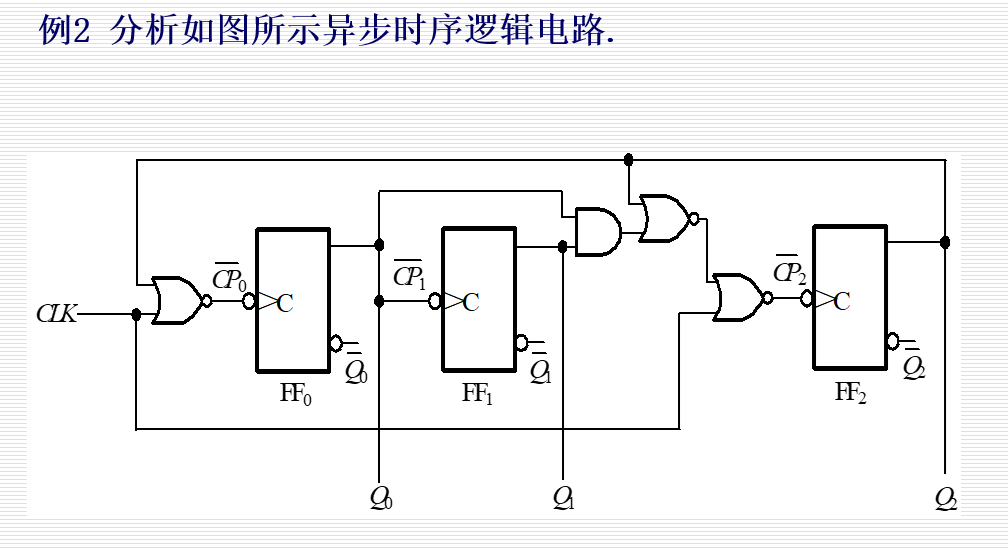

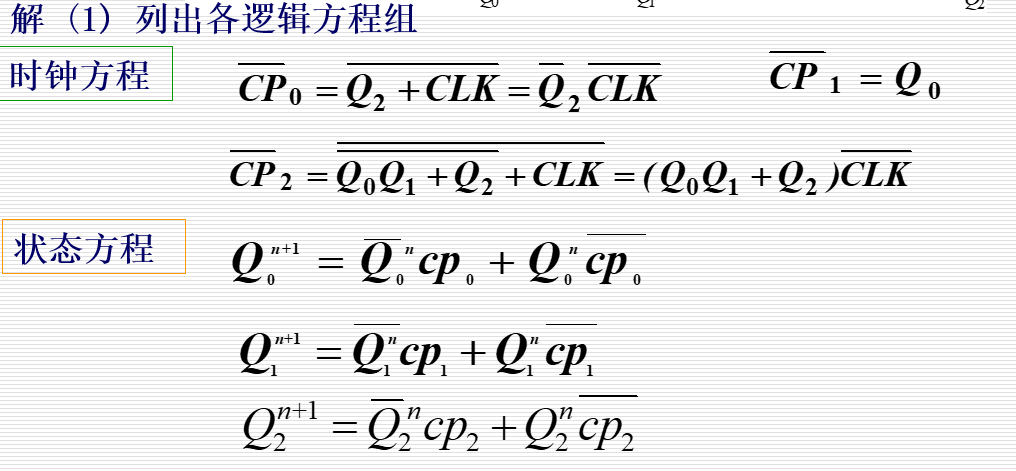

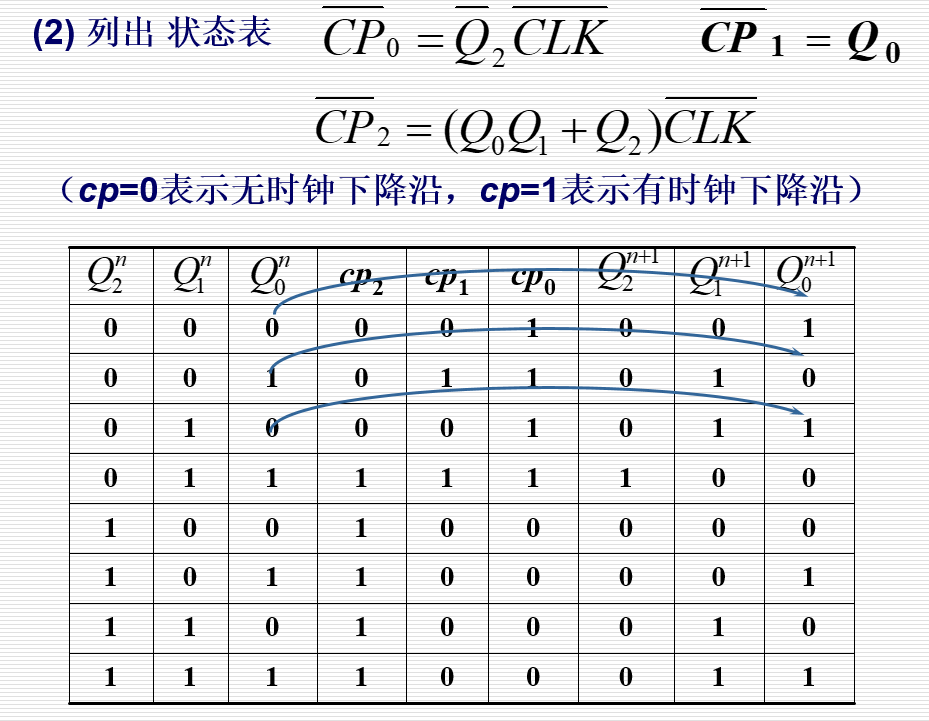

分析方法

异步时序逻辑电路的一般步骤

- 了解电路的组成:电路的输入、输出信号、触发器的类型

- 根据给定的电路图,列写电路的时钟方程、输出方程、各触发器的激励方程、状态方程(联立激励方程与触发器的自身特性得到)

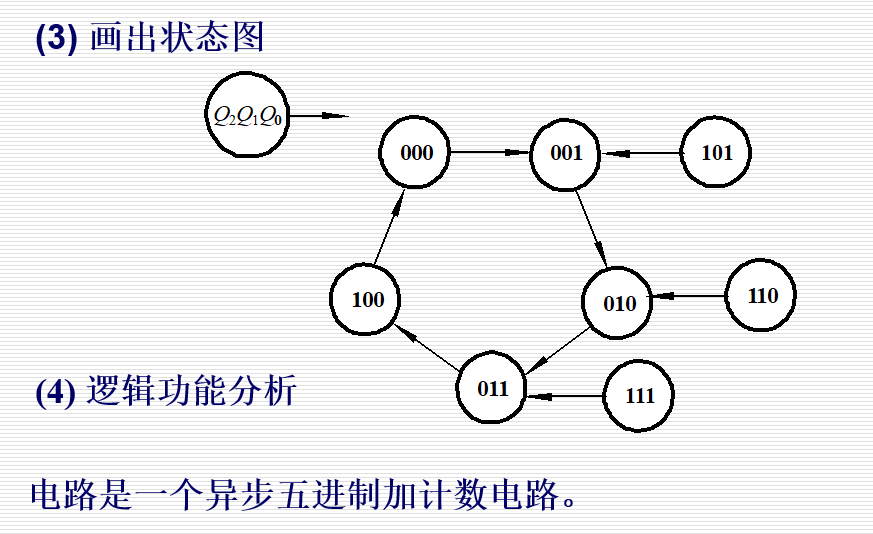

- 列写状态转换表、画出状态图和波形图

- 确定电路的逻辑功能

异步时序逻辑电路分析的注意事项

- 分析状态转换时,必须考虑各触发器的时钟信号的作用情况。对于时钟有效的触发器,再根据激励信号确定这些触发器的次态,对于时钟无效的触发器,触发器次态保持原有状态不变。

- 每一次状态转换必须从输入信号所能触发的第一个触发器开始逐级确定

- 异步时序电路各个触发器之间状态转换存在延迟,只有当全部触发器状态转换完毕之后,电路才进入新的稳定次态。

分析举例

五、若干典型的时序逻辑电路

寄存器与移位寄存器

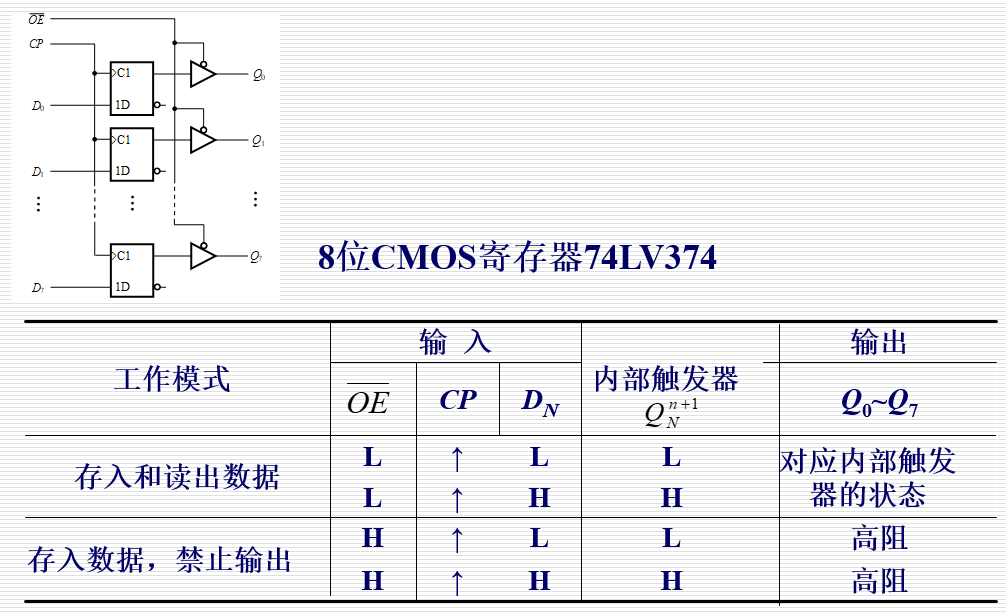

寄存器实际上就是若干触发器的集合,常用寄存器的集成芯片如下所示:

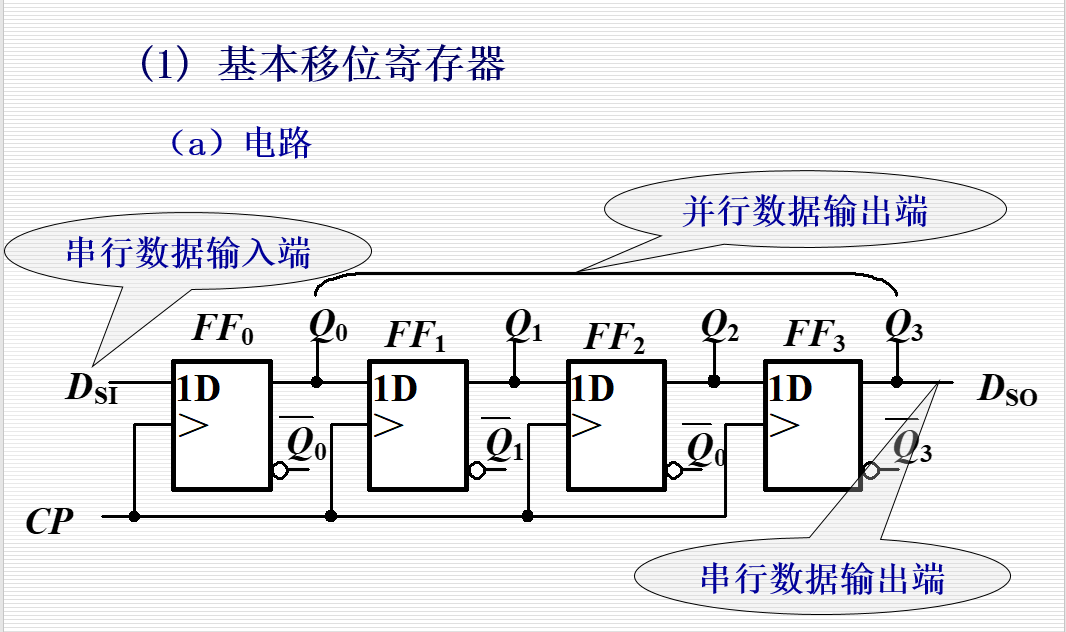

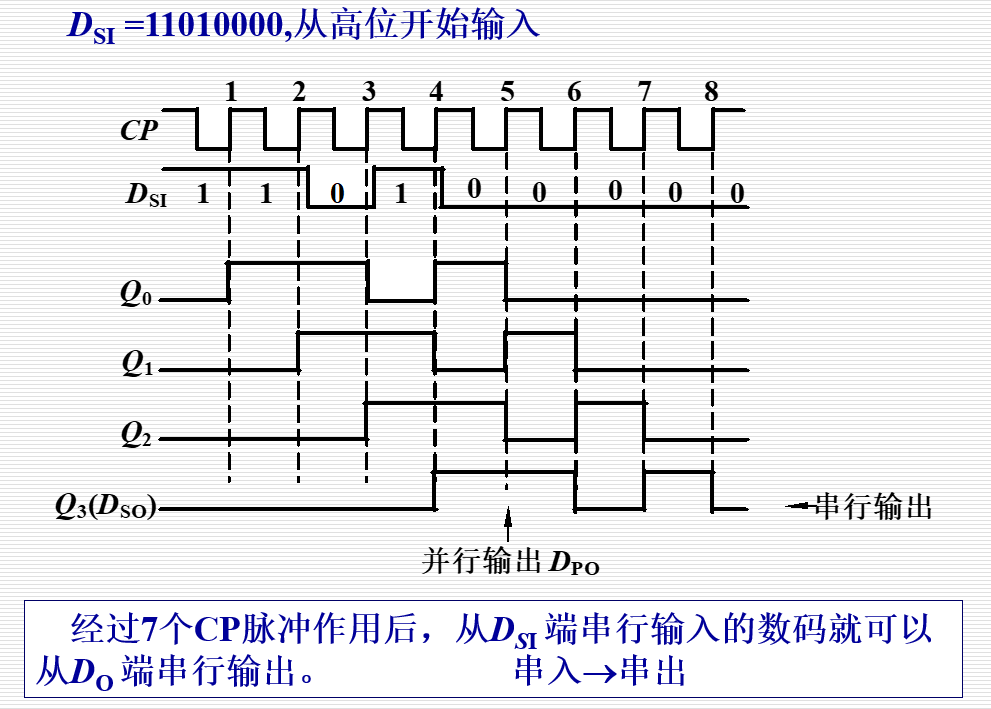

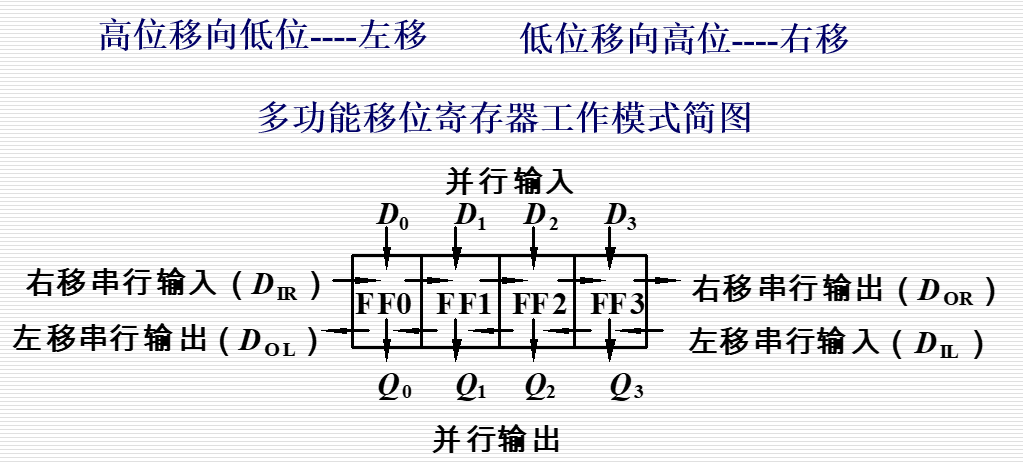

移位寄存器既能寄存数码,又能在时钟脉冲的作用下使数码向高位或向低位移动的逻辑部件

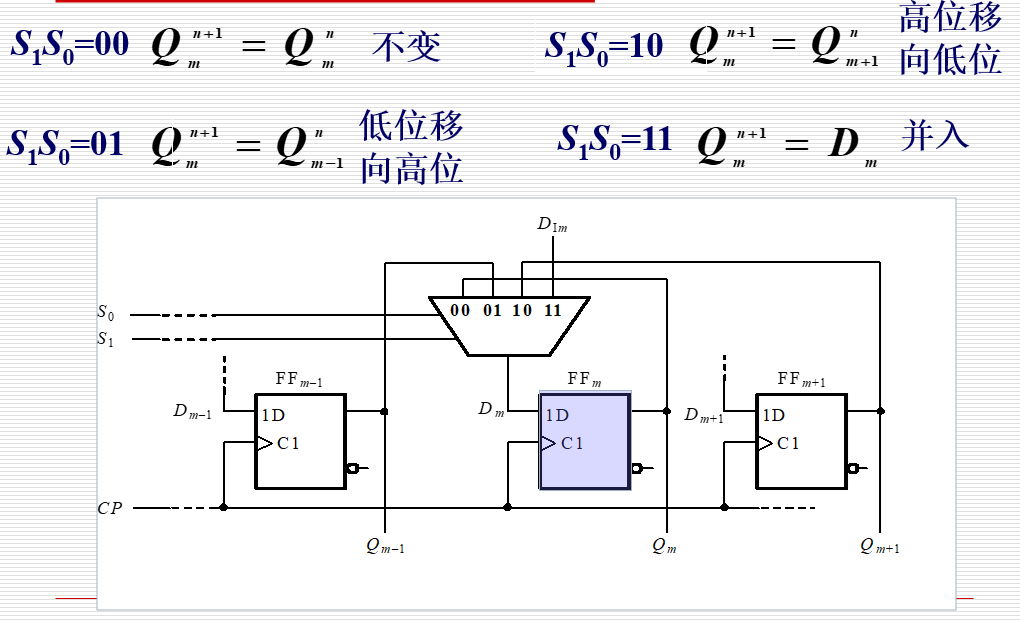

双向移位寄存器的机理如下

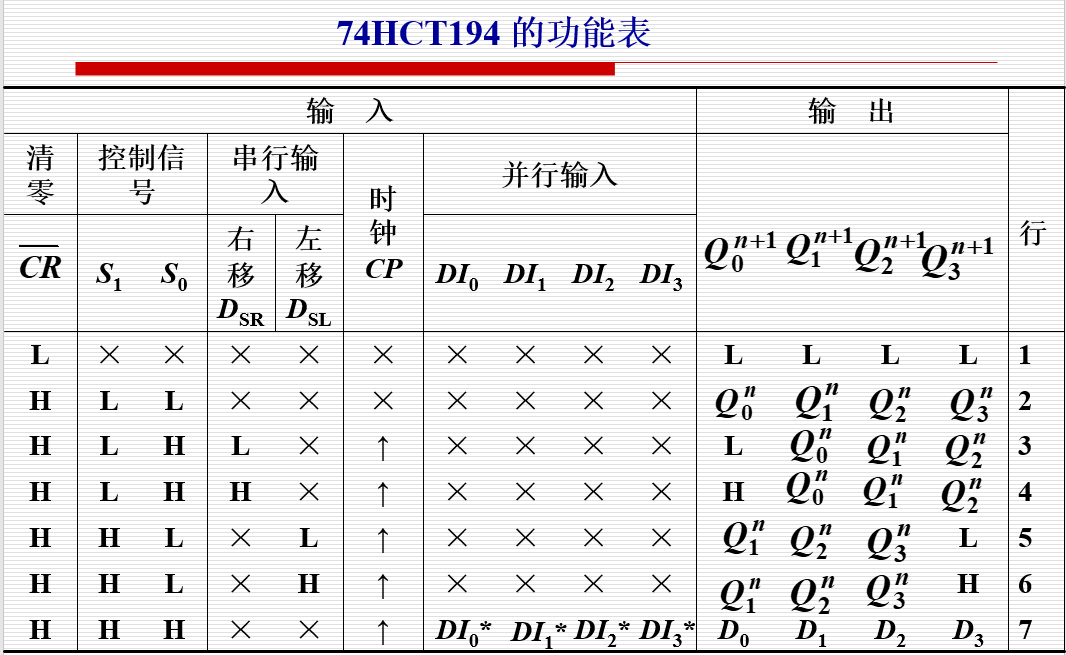

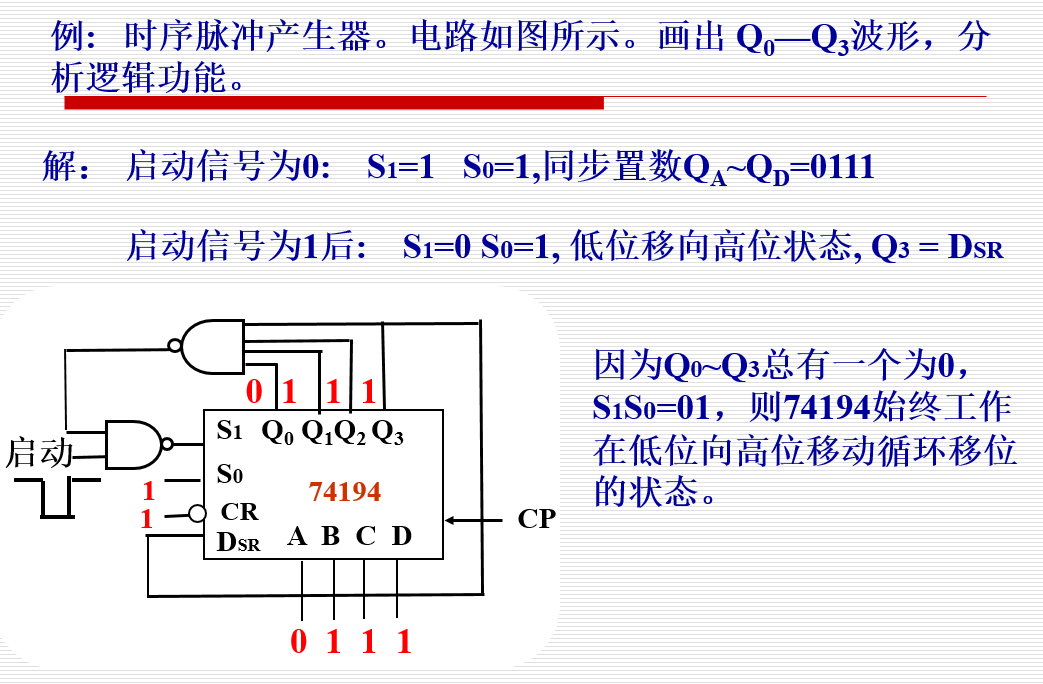

集成双向移位寄存器芯片功能表如下:

集成双向移位寄存器芯片功能表如下:

计数器

计数器的功能是对输入脉冲进行计数,也可用于分频、定时。

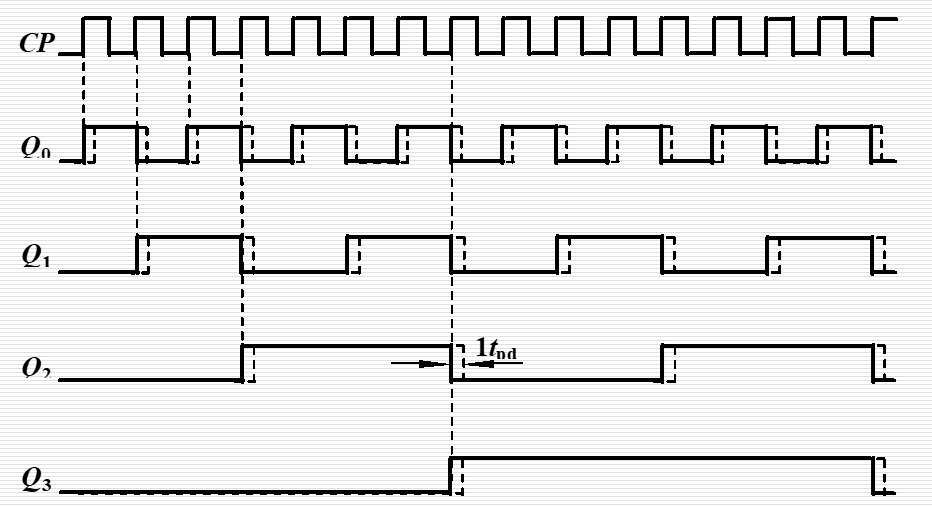

异步二进制计数器

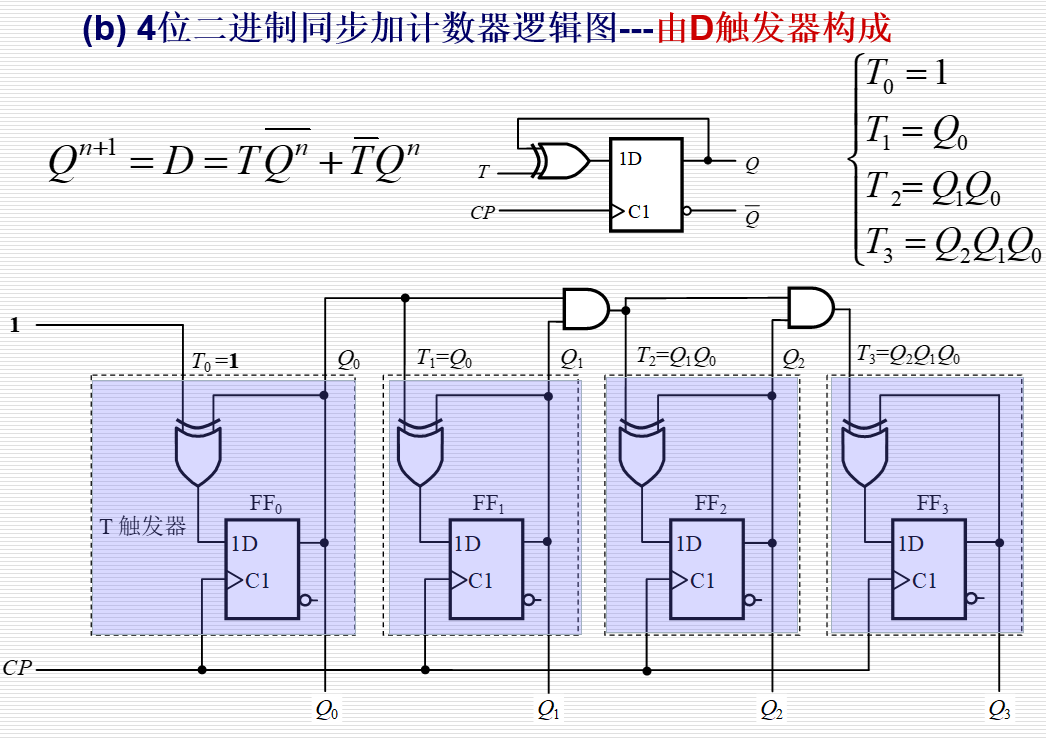

同步二进制计数器

如何把异步电路改成同步? 思想是:如果当你需要用一个逻辑运算生成的脉冲上升/下降沿做触发时,仅把这个生成的信号作为使能信号,只有这个信号有效时时钟脉冲有效即可,而不把这个生成的脉冲作为时钟信号。

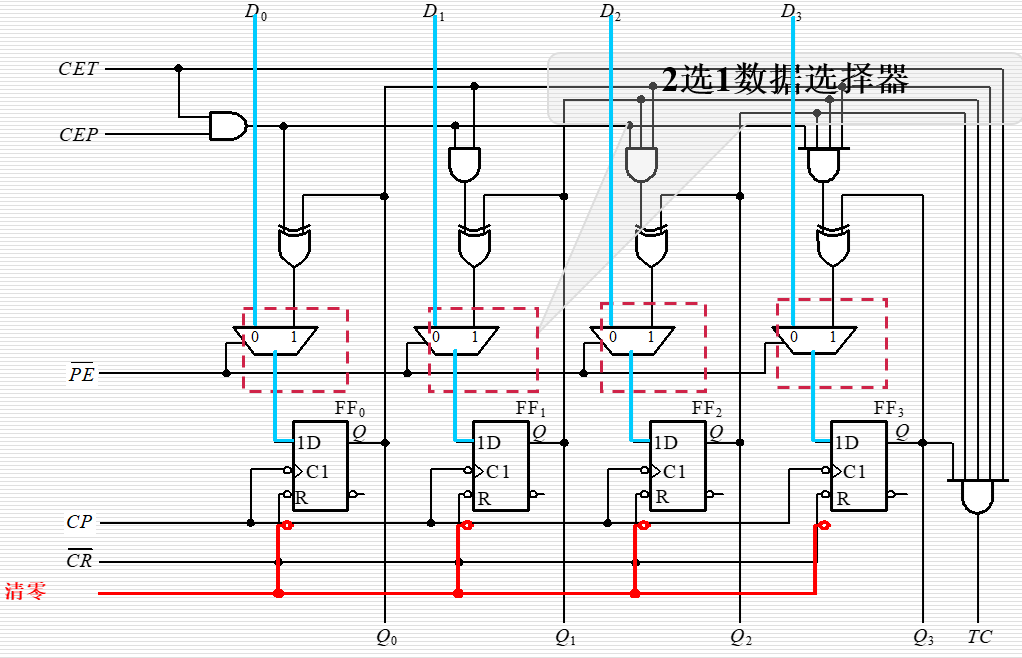

集成的同步计数器芯片如下:

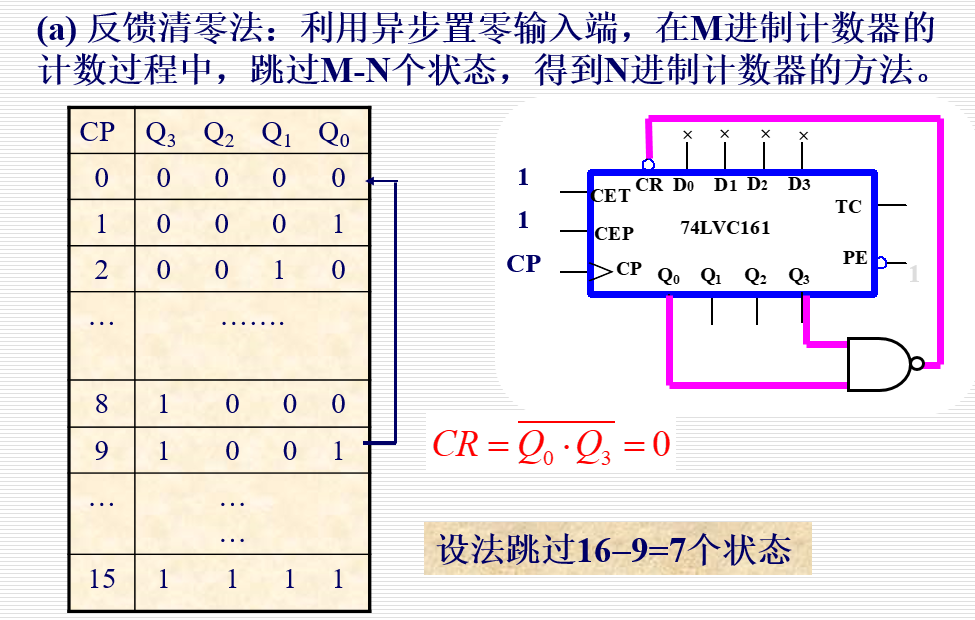

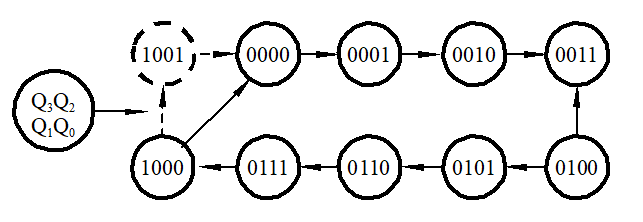

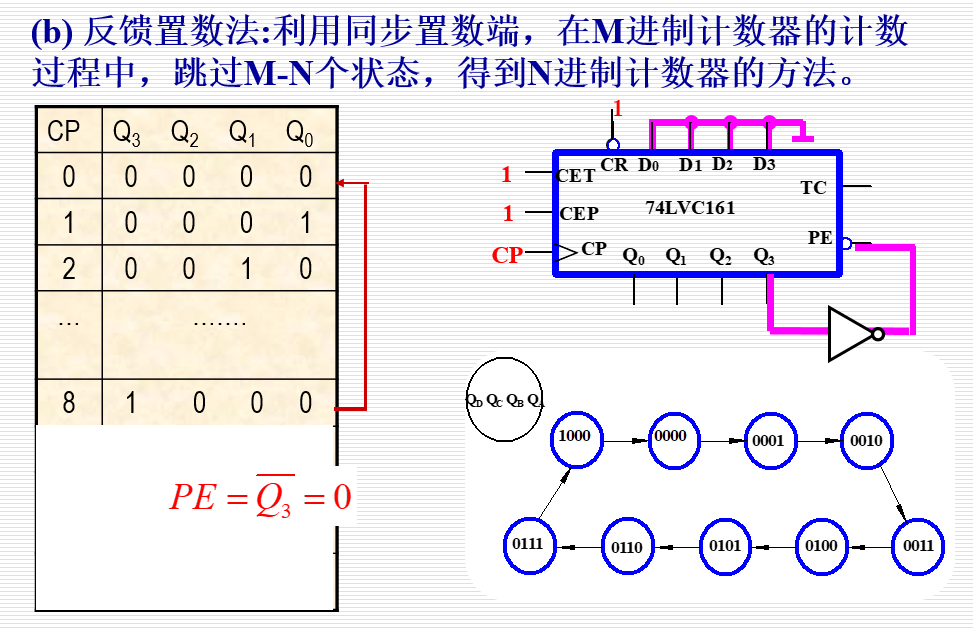

例子:利用74LVC161构成九进制加计数器

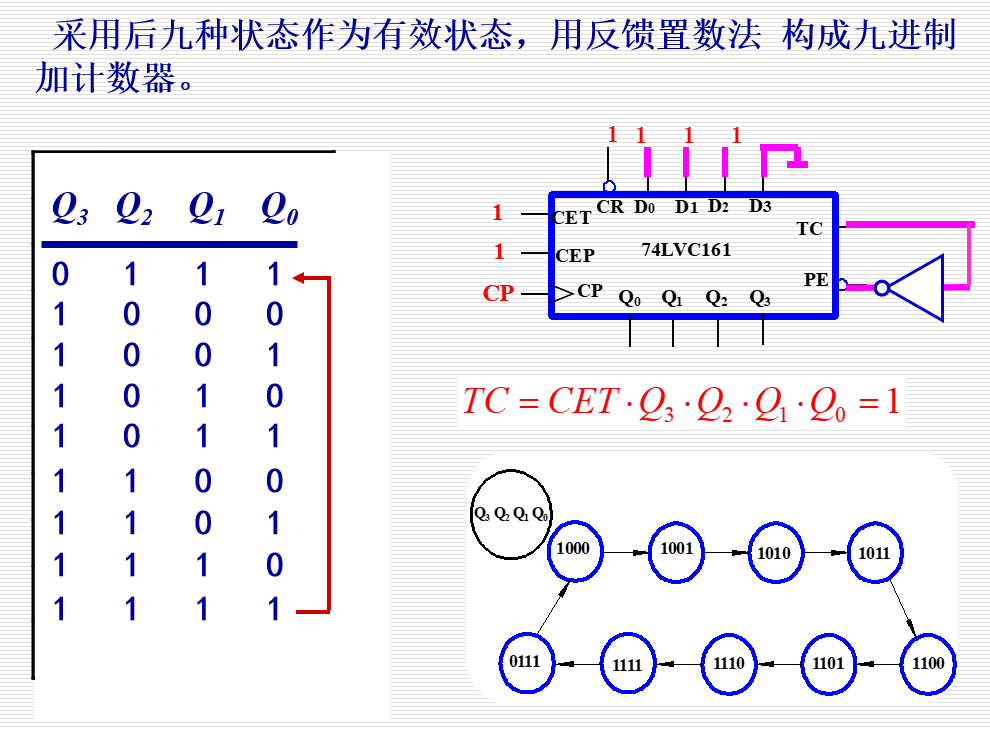

也可以用进位信号作为置数信号,构成九进制计数器

也可以用进位信号作为置数信号,构成九进制计数器

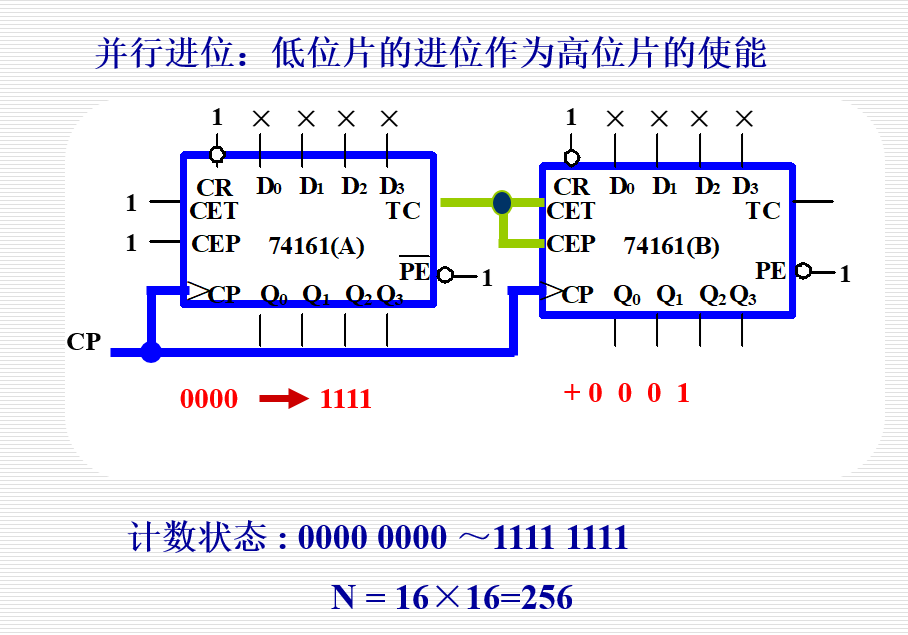

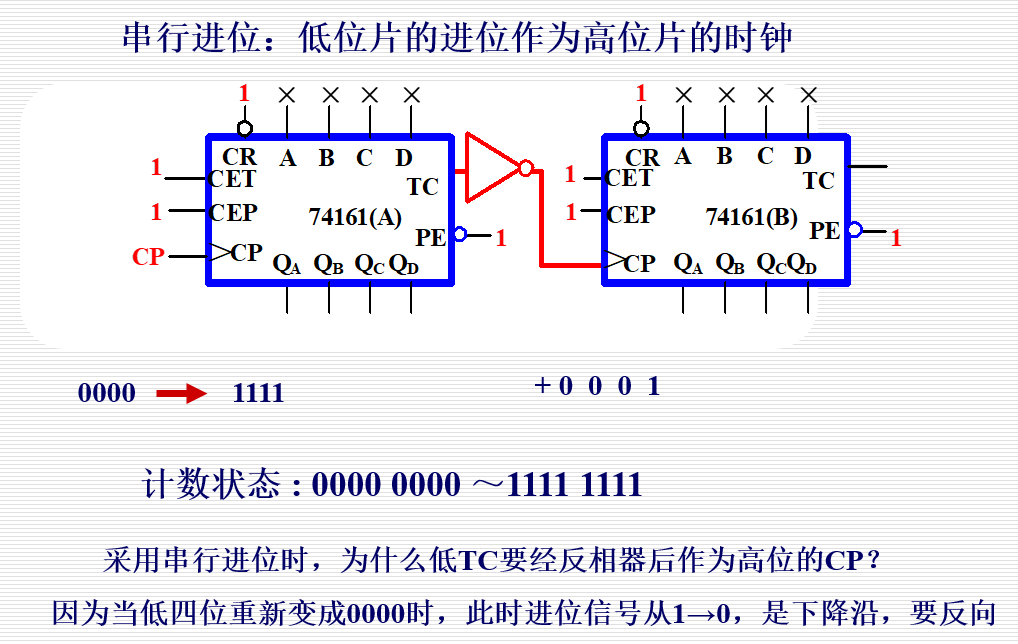

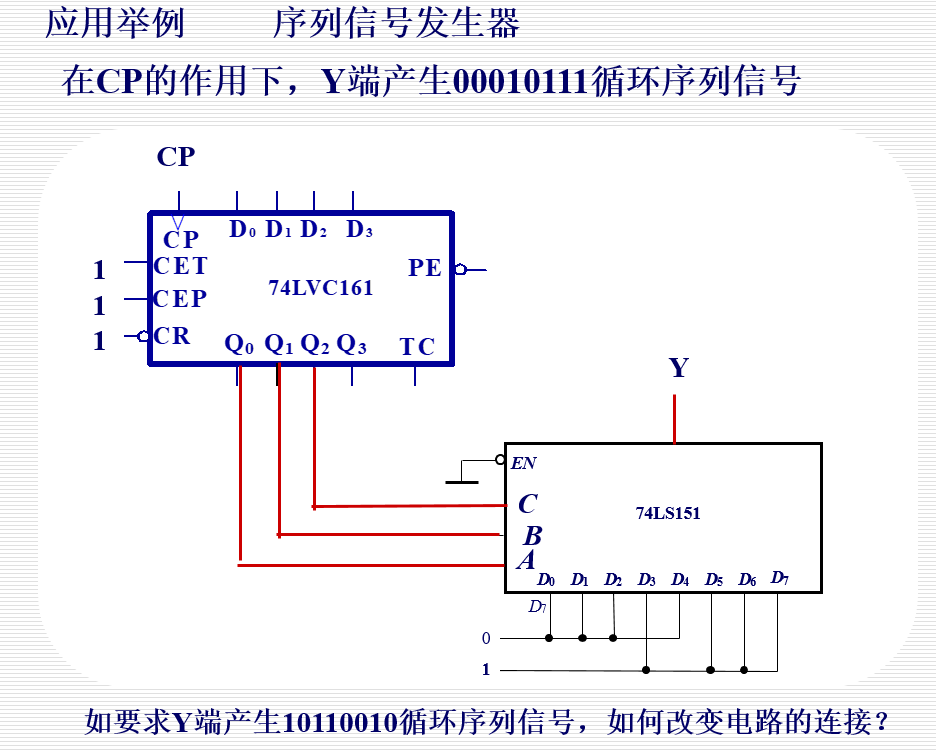

如何用74VC61组成256进制的计数器

最后

以上就是可靠秀发最近收集整理的关于数电基础(6)--时序逻辑电路一、时序逻辑电路的基本概念二、同步时序逻辑电路的分析三、同步时序逻辑电路的设计四、异步时序逻辑电路的分析五、若干典型的时序逻辑电路的全部内容,更多相关数电基础(6)--时序逻辑电路一、时序逻辑电路内容请搜索靠谱客的其他文章。

发表评论 取消回复