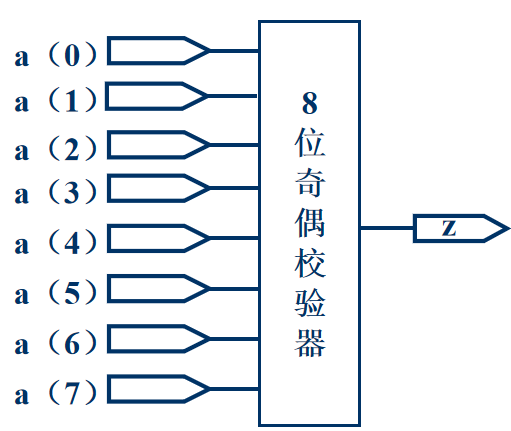

1.引脚图

z:输出校验位

2.VHDL语言

2.1 一般顺序语句

library ieee;

use ieee.std_logic_1164.all;

entity p_check is

port(a : in std_logic_vector(7 downto 0); --定义a为长度8的标准逻辑矢量位矢量

y : out std_logic);

end p_check;

architecture behave of p_check is

begin

process(a)

variable temp : std_logic;

begin

temp := '0';

temp := temp xor a(0);

temp := temp xor a(1);

temp := temp xor a(2);

temp := temp xor a(3);

temp := temp xor a(4);

temp := temp xor a(5);

temp := temp xor a(6);

temp := temp xor a(7);

y <= temp;

end process;

end behave;

2.2 for loop语句

architecture behave of p_check is

begin

process(a)

variable temp : std_logic;

begin

temp := '0';

for n in 0 to 7 loop --循环7次,n为循环变量

temp := temp xor a(n);

end loop;

y <= temp;

end process;

end behave;

2.3 while loop语句

architecture behave of p_check is

begin

process(a)

variable temp : std_logic;

variable n : integer; --定义循环变量n为整数

begin

temp := '0';

n := 0;

while n<8 loop

temp := temp xor a(n);

n := n+1;

end loop;

y <= temp;

end process;

end behave;

最后

以上就是碧蓝太阳最近收集整理的关于VHDL——8位奇偶校验电路的全部内容,更多相关VHDL——8位奇偶校验电路内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复