|

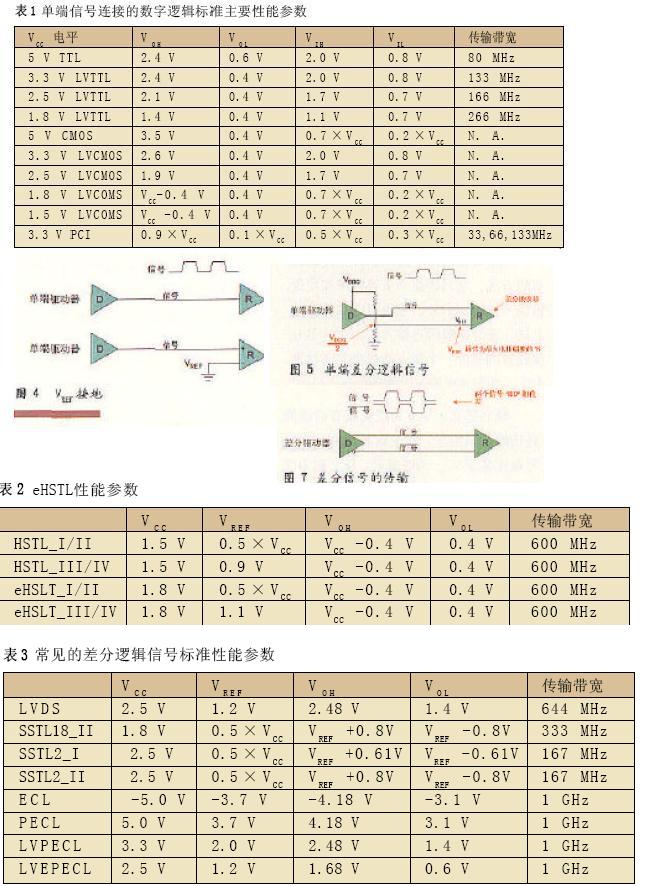

我们知道,0和1是数字世界的两个基本元素,在数字电路中它们由特定范围的高低电平来表示。数字电路发展的早期,绝大多数数字器件都采用TTL和CMOS数字逻辑标准。近几年,产生了许多针对不同应用的低压、高速的数字逻辑标准,例如LVTTL、LVCMOS、LVDS、HSTL、SSTL、LVPECL等。

实际应用中共有二三十种数字逻辑信号标准,根据其物理连接特性不同,可以划分为单端逻辑信号、单端差分逻辑信号和差分逻辑信号三大类。在对它们详细介绍之前,我们首先了解一下数字逻辑信号的几个重要专业术语。

a. 门限电压(VTH )

-- -顾名思义,VTH为逻辑状态高或低转换的门限电压,在逻辑器件中,当信号电压高于VTH 为逻辑高,反之则为逻辑低,通常VTH为电源电压的1/2。 --- b. 输出高电平(VOH)和输出低电平(VOL) --- 确切地说VOH应该为逻辑器件输出高电平的下限,VOL为输出低电平的上限。通常在VOH和VOL之间有一个电压缓冲区,这样在实际电路中输出逻辑信号迭加噪声后,就不会导致对逻辑状态的错误判断。 --- c. 输入高电平(VIH)和输入低电平(VIL) --- VIH为输入高电平的下限,VIL为输入低电平的上限。

在许多数字系统中,前一个逻辑器件的输出就是后一个逻辑器件的输入,所以必须满足VOH>VIH、VOL< VIL,否则就会出现逻辑状态判断错误。另外,它们之间的差值称为噪声容限,外部叠加的噪声应小于噪声容限,否则也会出现逻辑状态判断错误。

单端数字逻辑信号 单端差分逻辑信号 差分逻辑信号

应用 接口技术

TTL:Transistor-Transistor Logic 三极管结构。

Vcc:5V

输出 VOL: <0.8V ; VOH:>2.4V。 输入 VIL: <1.2V ; VIH: >2.0V TTL器件输出低电平要小于0.8V,高电平要大于2.4V。输入,低于1.2V就认为是0,高于2.0就认为是1。

因为2.4V与5V之间还有很大空闲,对改善噪声容限并没什么好处,又会白白增大系统功耗,还会影响速度。所以后来就把一部分“砍”掉了。也就是后面的LVTTL。

LVTTL又分3.3V、2.5V以及更低电压的LVTTL(Low Voltage TTL)。

3.3V LVTTL:

Vcc:3.3V;VOH>=2.4V;VOL<=0.4V;VIH>=2V;VIL<=0.8V。 2.5V LVTTL: Vcc:2.5V;VOH>=2.0V;VOL<=0.2V;VIH>=1.7V;VIL<=0.7V。

TTL使用注意:TTL电平一般过冲都会比较严重,可能在始端串22欧或33欧电阻;TTL电平输入脚悬空时是内部认为是高电平。要下拉的话应用1k以下电阻下拉。TTL输出不能驱动CMOS输入。

CMOS电平:Complementary Metal Oxide Semiconductor PMOS+NMOS。

Vcc:5V

输出 VOL: <0.1*Vcc ; VOH:>0.9*Vcc。 输入 VIL: <0.3*Vcc ; VIH: >0.7*Vcc.

CMOS电平Vcc可达到12V

CMOS电路输出高电平约为0.9Vcc,而输出低电平约为 0.1Vcc。

相对TTL有了更大的噪声容限,输入阻抗远大于TTL输入阻抗。对应3.3V LVTTL,出现了LVCMOS,可以与3.3V的LVTTL直接相互驱动。

3.3V LVCMOS:

Vcc:3.3V;VOH>=3.2V;VOL<=0.1V;VIH>=2.0V;VIL<=0.7V。 2.5V LVCMOS: Vcc:2.5V;VOH>=2V;VOL<=0.1V;VIH>=1.7V;VIL<=0.7V。 CMOS使用注意:CMOS结构内部寄生有可控硅结构,当输入或输入管脚高于VCC一定值(比如一些芯片是0.7V)时,电流足够大的话,可能引起闩锁效应,导致芯片的烧毁。 CMOS电路不使用的输入端不能悬空,会造成逻辑混乱,不用的输入端必须连到高电平或低电平, 这是因为 CMOS 是高输入阻抗器件, 理想状态是没有输入电流的. 如果不用的输入引脚悬空, 很容易感应到干扰信号, 影响芯片的逻辑运行, 甚至静电积累永久性的击穿这个输入端, 造成芯片失效. 另外,CMOS集成电路电源电压Vcc可以在较大范围内变化,因而对电源的要求不像TTL集成电路那样严格。 用TTL电平他们就可以兼容。

TTL和CMOS区别:

1.电平的上限和下限定义不一样,CMOS具有更大的抗噪区域。同是5伏供电的话,ttl一般是1.7V和3.5V的样子,CMOS一般是2.2V,2.9V的样子,不准确,仅供参考。

2。电流驱动能力不一样,ttl一般提供25毫安的驱动能力,而CMOS一般在10毫安左右。

3。需要的电流输入大小也不一样,一般ttl需要2.5毫安左右,CMOS 几乎不需要电流输入。 4。TTL电路是电流控制器件,而coms电路是电压控制器件。 5。TTL电路的速度快,传输延迟时间短(5-10ns),但是功耗大。COMS电路的速度慢,传输延迟时间长(25-50ns),但功耗低。COMS电路本身的功耗与输入信号的脉冲频率有关,频率越高,芯片集越热,这是正常现象。 COMS电路的锁定效应: COMS电路由于输入太大的电流,内部的电流急剧增大,除非切断电源,电流一直在增大。这种效应就是锁定效应。当产生锁定效应时,COMS的内部电流能达到40mA以上,很容易烧毁芯片。 防御措施: 1)在输入端和输出端加钳位电路,使输入和输出不超过不超过规定电压。 2)芯片的电源输入端加去耦电路,防止VDD端出现瞬间的高压。 3)在VDD和外电源之间加线流电阻,即使有大的电流也不让它进去。 4)当系统由几个电源分别供电时,开关要按下列顺序:开启时,先开启COMS电路得电源,再开启输入信号和负载的电源;关闭时,先关闭输入信号和负载的电源,再关闭COMS电路的电源。

COMS电路的使用注意事项

1)COMS电路时电压控制器件,它的输入总抗很大,对干扰信号的捕捉能力很强。所以,不用的管脚不要悬空,要接上拉电阻或者下拉电阻,给它一个恒定的电平。 2)输入端接低内组的信号源时,要在输入端和信号源之间要串联限流电阻,使输入的电流限制在1mA之内。 3)当接长信号传输线时,在COMS电路端接匹配电阻。 4)当输入端接大电容时,应该在输入端和电容间接保护电阻。电阻值为R=V0/1mA.V0是外界电容上的电压。 5)COMS的输入电流超过1mA,就有可能烧坏COMS。 TTL门电路中输入端负载特性(输入端带电阻特殊情况的处理): 1)悬空时相当于输入端接高电平。因为这时可以看作是输入端接一个无穷大的电阻。 2)在门电路输入端串联10K电阻后再输入低电平,输入端出呈现的是高电平而不是低电平。因为由TTL门电路的输入端负载特性可知,只有在输入端接的串联电阻小于910欧时,它输入来的低电平信号才能被门电路识别出来,串联电阻再大的话输入端就一直呈现高电平。这个一定要注意。COMS门电路就不用考虑这些了。 TTL电路有集电极开路OC门,MOS管也有和集电极对应的漏极开路的OD门,它的输出就叫做开漏输出。OC门在截止时有漏电流输出,那就是漏电流,为什么有漏电流呢?那是因为当三机管截止的时候,它的基极电流约等于0,但是并不是真正的为0,经过三极管的集电极的电流也就不是真正的 0,而是约0。而这个就是漏电流。开漏输出:OC门的输出就是开漏输出;OD门的输出也是开漏输出。它可以吸收很大的电流,但是不能向外输出的电流。所以,为了能输入和输出电流,它使用的时候要跟电源和上拉电阻一齐用。OD门一般作为输出缓冲/驱动器、电平转换器以及满足吸收大负载电流的需要。 TTL集成电路中,输出有接上拉三极管的输出叫做图腾柱输出,没有的叫做OC门。因为TTL就是一个三级关,图腾柱也就是两个三级管推挽相连。所以推挽就是图腾。一般图腾式输出,高电平400UA,低电平8MA

3.3V和5.0V电平信号的转换

在混合电压系统中,不同电源电压的逻辑器件互相接口时存在以下几个问题:

第一,加到输入和输出引脚上允许的最大电压限制问题。器件对加到输入或者输出脚上的电压通常是有限制的。这些引脚有二极管或者分离元件接到Vcc。如果接入的电压过高,则电流将会通过二极管或者分离元件流向电源。例如在3.3V器件的输入端加上5V的信号,则5V电源会向3.3V电源充电。持续的电流将会损坏二极管和其它电路元件。

第二,两个电源间电流的互串问题。在等待或者掉电方式时,3.3V电源降落到0V,大电流将流通到地,这使得总线上的高电压被下拉到地,这些情况将引起数据丢失和元件损坏。必须注意的是:不管在3.3V的工作状态还是在0V的等待状态都不允许电流流向Vcc。

第三,接口输入转换门限问题。5V器件和3.3V器件的接口有很多情况,同样TTL和CMOS间的电平转换也存在着不同情况。驱动器必须满足接收器的输入转换电平,并且要有足够的容限以保证不损坏电路元件。

基于上述情况,5V器件和3.3V器件是不能直接接口的。有些半导体器件制造厂家就推出了具有5V输入容限的3.3V器件,这种器件输入端具有ESD保护电路。实际上数字电路的所有输入端都有一个ESD保护电路,传统的CMOS电路通过接地二极管对负向高电压限幅,正向高电压则由二极管钳位。这种电路的缺点是最大的输入电压被限制在3.3V+0.5V(二极管压降)以内(否则电流将流向3.3V电源)。而大多数5V系统输出端的电压可达3.6V以上,因此采用了这种电路结构的3.3V器件是不能与5V器件输出端直接接口的。如果采用相当于快速齐纳二极管的MOS场效应管代替上述钳位二极管,实现对高电压限幅,并且去掉接到Vcc(3.3V)的二极管,那么最大输入电压不受Vcc(3.3V)的限制。典型情况下,这种电路的击穿电压在7V~10V之间。因此,这种改进后具有ESD保护电路的3.3V系统的输入端可以承受5V的输入电压。为了防止在3.3V器件的输出端可能存在电流倒灌问题,还需要在输出端加保护电路,当加到输出端电压高于Vcc(3.3V)时,保护电路的比较器会断开电流倒灌通路,这样在三态方式时就能与5V器件相连。

分析各种逻辑电平信号的电特性,会发现有以下五种接口情况: 第一, 相同供电电压的TTL器件驱动CMOS器件时,TTL器件的输出高电平可能达不到CMOS器件的输入高电平的最小值。3.3V TTL器件的VOH是2.4V,3.3V CMOS器件的VIH是0.8VCC(3.3V×0.8=2.64V);5.0V TTL器件的VOH是2.4V,5.0V CMOS器件的VIH是0.7VCC(3.5V)。为了可靠地传输数据,可以将TTL器件的输出端上拉。有些CMOS工艺制造的器件兼容 TTL电平,这样就可以与相同供电电压的TTL器件直接接口,不需要上拉。

第二,

相同供电电压的CMOS器件驱动TTL器件,电平匹配,数据能可靠地传输。

第三,

不同供电电压的TTL器件驱动CMOS器件时,TTL器件的输出高电平也可能达不到CMOS器件的输入高电平的最小值。3.3V TTL器件的VOH是2.4V,5.0V CMOS器件的VIH是0.7VCC(3.5V),电平不匹配;5.0V TTL器件的VOH是2.4V,3.3V CMOS器件的VIH是0.8VCC(2.64V),可以将5.0V TTL器件的输出端上拉,达到电平匹配的目的。

第四,

不同供电电压的CMOS器件驱动TTL器件时,在输入端具有5V容限的情况下,电平匹配,数据能可靠地传输。

第五,不同供电电压的TTL器件在输入端具有5V容限的情况下可以直接接口;不同供电电压的CMOS器件由于电平不匹配不能直接接口。

由以上分析可知,不同逻辑标准的电平信号一般是不能直接接口的。在只有少量信号需要电平转换的情况下,可以考虑上拉电阻或选择具有5V输入容限的器件,甚至可以考虑电阻分压降低输入电压的办法。对于大量信号需要电平转换的情况,为了可靠传输数据,可以采用双电压(一边是3.3V,另一边是5V)供电的双向驱动器来实现电平转换。如仙童半导体公司的74LVX4245、TI公司的SN74ALVC164245、SN74ALVC4245 ECL:Emitter Coupled Logic 发射极耦合逻辑电路(差分结构) Vcc=0V;Vee:-5.2V;VOH=-0.88V;VOL=-1.72V;VIH=-1.24V;VIL=-1.36V。 速度快,驱动能力强,噪声小,很容易达到几百M的应用。但是功耗大,需要负电源。为简化电源,出现了PECL(ECL结构,改用正电压供电)和LVPECL。 PECL:Pseudo/Positive ECL Vcc=5V;VOH=4.12V;VOL=3.28V;VIH=3.78V;VIL=3.64V LVPELC:Low Voltage PECL Vcc=3.3V;VOH=2.42V;VOL=1.58V;VIH=2.06V;VIL=1.94V ECL、PECL、LVPECL使用注意:不同电平不能直接驱动。中间可用交流耦合、电阻网络或专用芯片进行转换。以上三种均为射随输出结构,必须有电阻拉到一个直流偏置电压。(如多用于时钟的LVPECL:直流匹配时用130欧上拉,同时用82欧下拉;交流匹配时用82欧上拉,同时用130欧下拉。但两种方式工作后直流电平都在1.95V左右。) 前面的电平标准摆幅都比较大,为降低电磁辐射,同时提高开关速度又推出LVDS电平标准。 LVDS:Low Voltage Differential Signaling 差分对输入输出,内部有一个恒流源3.5-4mA,在差分线上改变方向来表示0和1。通过外部的100欧匹配电阻(并在差分线上靠近接收端)转换为±350mV的差分电平。 LVDS使用注意:可以达到600M以上,PCB要求较高,差分线要求严格等长,差最好不超过10mil(0.25mm)。100欧电阻离接收端距离不能超过500mil,最好控制在300mil以内。 下面的电平用的可能不是很多,篇幅关系,只简单做一下介绍。如果感兴趣的话可以联系我。 CML:是内部做好匹配的一种电路,不需再进行匹配。三极管结构,也是差分线,速度能达到3G以上。只能点对点传输。 GTL:类似CMOS的一种结构,输入为比较器结构,比较器一端接参考电平,另一端接输入信号。1.2V电源供电。 Vcc=1.2V;VOH>=1.1V;VOL<=0.4V;VIH>=0.85V;VIL<=0.75V PGTL/GTL+: Vcc=1.5V;VOH>=1.4V;VOL<=0.46V;VIH>=1.2V;VIL<=0.8V HSTL是主要用于QDR存储器的一种电平标准:一般有V¬CCIO=1.8V和V¬¬CCIO= 1.5V。和上面的GTL相似,输入为输入为比较器结构,比较器一端接参考电平(VCCIO/2),另一端接输入信号。对参考电平要求比较高(1%精度)。 SSTL主要用于DDR存储器。和HSTL基本相同。V¬¬CCIO=2.5V,输入为输入为比较器结构,比较器一端接参考电平1.25V,另一端接输入信号。对参考电平要求比较高(1%精度)。 HSTL和SSTL大多用在300M以下。 RS232和RS485基本和大家比较熟了,只简单提一下: RS232采用±12-15V供电,我们电脑后面的串口即为RS232标准。+12V表示0,-12V表示1。可以用MAX3232等专用芯片转换,也可以用两个三极管加一些外围电路进行反相和电压匹配。 RS485是一种差分结构,相对RS232有更高的抗干扰能力。传输距离可以达到上千米 |

最后

以上就是灵巧大象最近收集整理的关于数字逻辑标准及接口技术的全部内容,更多相关数字逻辑标准及接口技术内容请搜索靠谱客的其他文章。

发表评论 取消回复