#悬崖上的花,越芬芳越无常。

今天来解决Robei EDA使用的时候遇到的问题的解决办法,这个有我自己遇到的,也有别人问我然后我帮着解决的。这几天刚好有学长来找我写代码,要仿真FPGA代码,结果电脑上的Modelsim好死不死出问题了,于是用了Robei 自带的仿真给了学长。学长还觉得挺方便的,至少对于初学者来说,很容易上手,不像我当年学FPGA,那叫一个泪流满面。

include 包含文件

在常见的Verilog代码中,会遇到包含 include 文件的写法,这样类似于定义一些全局的常量,方便调用。在quartus 里的写法是这样的:

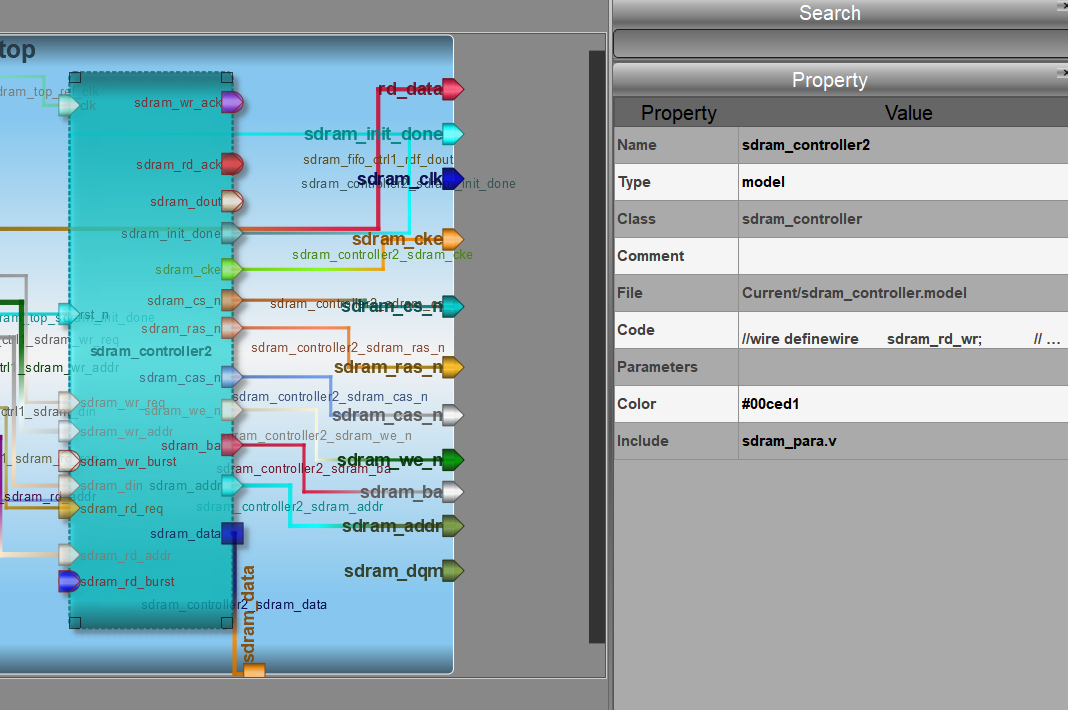

`include “sdram_para.v”而在Robei EDA里,include 无法直接写在Code 部分,而是在定义栏的地方添加。

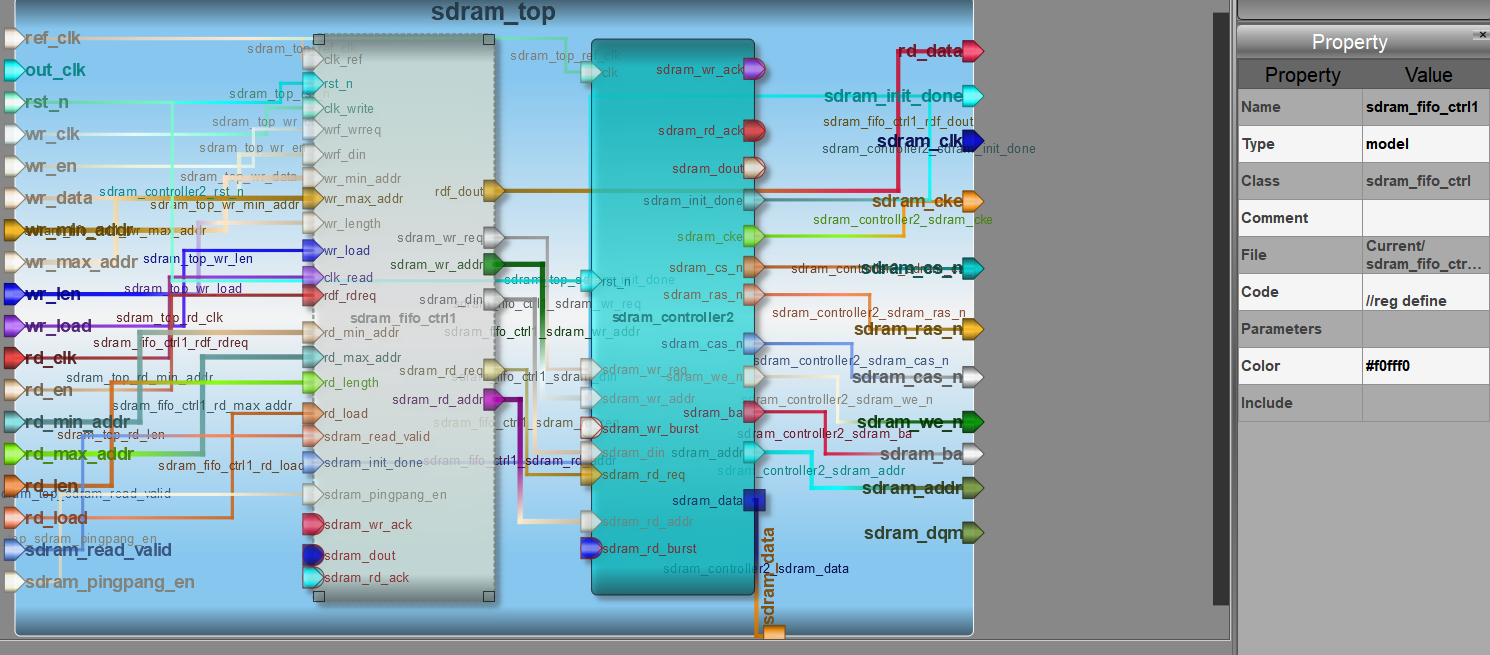

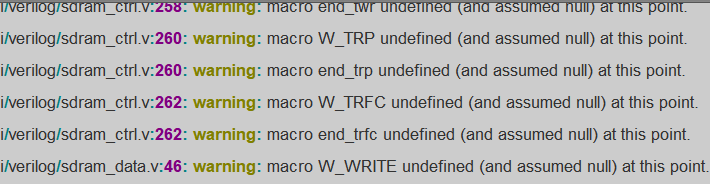

在右侧的定义栏,可以看到 “include” 的框子,将文件名称和后缀添加进去,在代码编译的时候就可以自动包含这个文件了。(注意,这个文件必须要放到Robei 模块的文件路径下,不然编译的时候软件会因为找不到文件而报错)

PS: 这里有一个问题,我在写SDRAM 的 子模块的时候,用到了这个sdram_para.v这个文件,但是我在上层文件综合的时候,并没有把这个文件加进去,它会报这样一个错误,就是告知你综合的时候,没有找到这个文件的声明。错误如下:

报这个错误的时候,就是我子模块里包含了这个文件,但是top文件里没有这个文件。

我解决这个问题的办法就在top文件的include里也加入这个文件,就不会报错了。

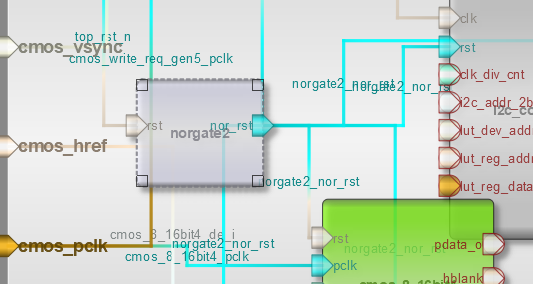

模块例化的问题

Robei EDA 里对于每一个模块被上层模块例化,信号线的连接方式有两种,一个是连线,另一个是通过connect连接内部信号。

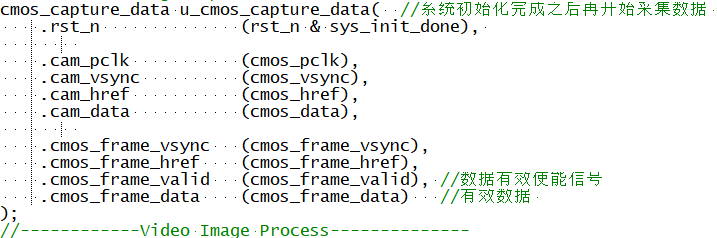

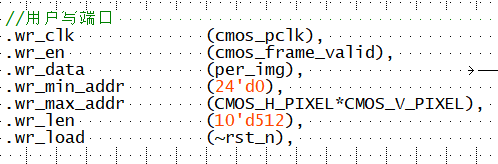

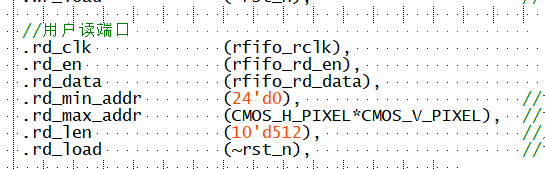

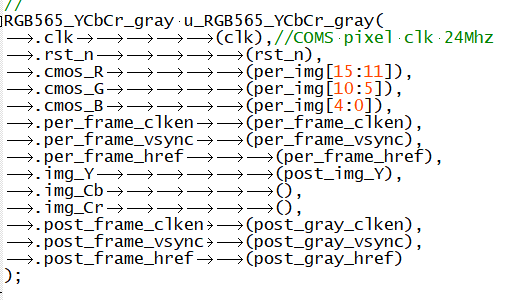

但是,事实上在FPGA里,例化方式稀奇古怪,就导致了有一些信号,不能直接像quartus的习惯那样连接。比如一下这类情况。

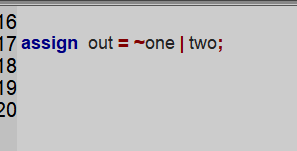

- 对信号取反一下在连接的。

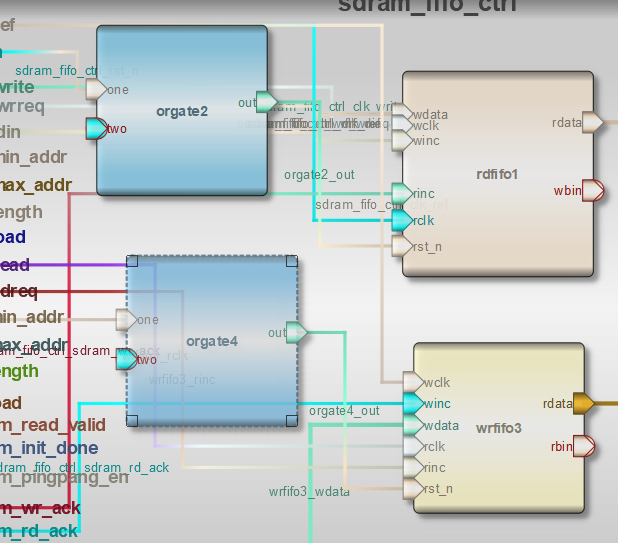

- 几个信号逻辑或、与一下的。

- 有数字还有乘法的

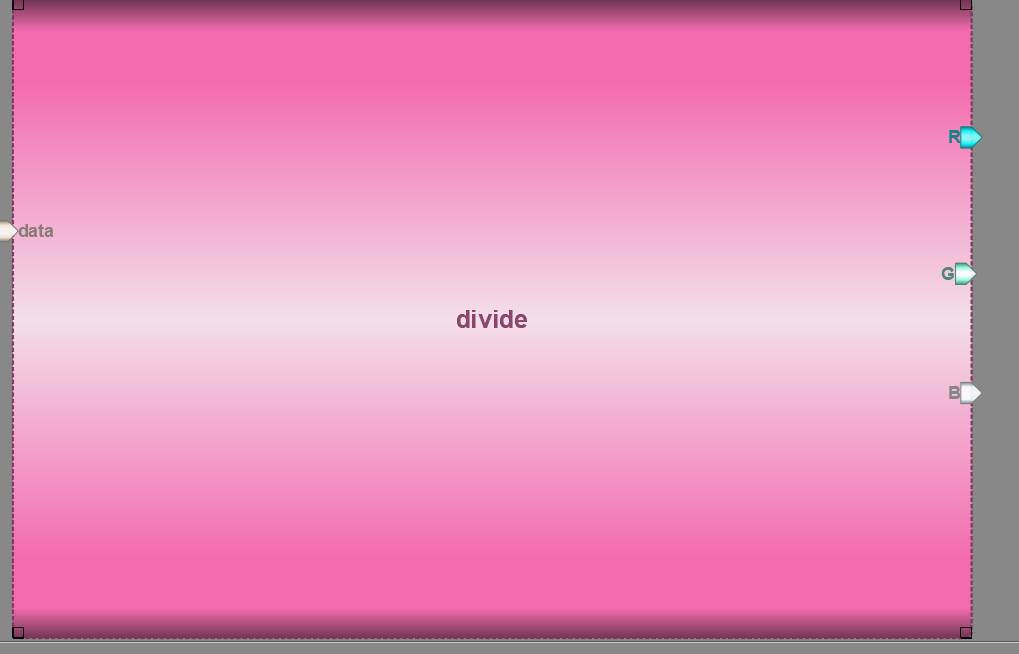

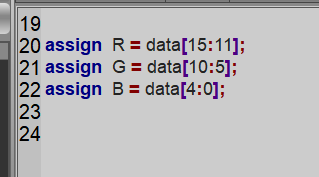

- 一个多位信号分开好几位的。(二值化的时候)

遇到这类随心所欲的数值例化,就很尴尬,一开始就不知道该怎么整。后来选择了一个办法,就是把这些信号再过一个模块,做一个初步的处理。 - 取反+逻辑或模块

ze_16,color_FFFFFF,t_70)

- 取反模块

- 信号分割模块

就是通过这样的简单的组合逻辑模块,有时候也可以是时序的,把原本的信号转换一下,改成符合要求的例化的信号线。因为其实在代码综合好后生成的RTL图里,在例化上的操作其实和我们现在定义模块是一个作用。

————————————————————正文结束的分割线———————————————

比赛马上要结束了,我们也在做最后的系统调试和综合,无论结果如何,都坦然面对。只是说,求仁得仁吧,这个对于我们来说也是成长。当我把人脸检测(伪)做出来的时候,我的一个学长和我说,我已经比他当年毕业的时候还厉害了,他的毕业设计也只是做了我前一部分而已。这是一个大我3届的学长,保研电科的大佬,算是我一入大学给我指引方向的人生导师,也是我一直追求的目标。他这么说很大程度上只是鼓励我,毕竟我和他的差距还是非常大的,但是不得不说我从比赛上却是学到了非常多,即使过程再艰辛,心之所向,九死不悔。(以后也要加油啊~)

最后

以上就是朴实便当最近收集整理的关于【FPGA】Robei EDA 常见问题解决 (3)——— include 问题 和模块例化问题的全部内容,更多相关【FPGA】Robei内容请搜索靠谱客的其他文章。

发表评论 取消回复