原文:https://www.jianshu.com/p/885913b7201c

ARMv8-A架构基础之系统控制寄存器

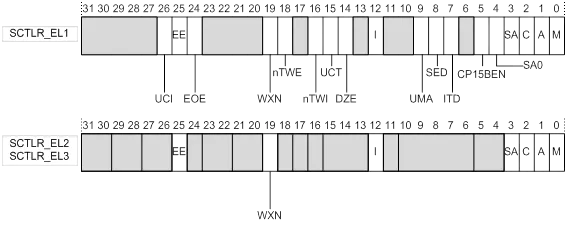

系统控制寄存器(SCTLR)用于控制标准内存和系统设备,并为在硬件内核中实现的功能提供状态信息。

cpsr_bits.png

并不是所有的位在EL1上都可用。 各个位代表以下内容:

| UCI | 设置此项时,在AArch64的EL0中可以访问DC CVAU,DC CIVAC,DC CVAC和IC IVAU指令。 |

|---|---|

| EE | 异常字节序。 0小端 1大端。 |

| EOE | EL0中数据访问的字节顺序。这个位的可能值是: 0小端。 1大端。 |

| WXN | 写入权限对XN(eXecute Never)的涵义。 0有写入权限的区域不被强制为XN。 1有写入权限的区域被强制为XN。 |

| nTWE | 值为0表示如果指令将导致硬件内核休眠,则WFE指令会陷入到EL1。 值为1表示WFE指令按正常执行。 |

| nTWI | 值为0表示如果指令将导致硬件内核休眠,则WFE指令会陷入到EL1。 值为1表示WFE指令按正常执行。 |

| UCT | 值为1表示在AArch64中的EL0访问CTR_EL0寄存器是允许的。 值为0表示在AArch64中的EL0访问CTR_EL0寄存器是禁止的。 |

| DZE | 在EL0上访问DC ZVA指令。 0不允许执行。 1允许执行。 |

| I | 这是EL0和EL1中指令缓存的使能位。 0指令访问普通内存不会被缓存。 1指令访问普通内存会被缓存 |

| UMA | 用户掩码访问。当EL0使用AArch64时,控制EL0中的中断掩码的访问。 0试图使用MSR或MSR指令访问DAIF被陷入在EL1。 1尝试使用MSR或MRS指令访问DAIF不被陷入在EL1处。 |

| SED | 在EL0使用AArch32时,禁用SETEND指令。 0 SETEND指令使能。 1 SETEND指令禁用。 |

| ITD | IT禁用位。这个位的可能值是: 0 IT指令可用。 1 IT指令被视为一个16位指令。只有另一个16位指令或32位指令的前一半可以跟随。这取决于实现。 |

| CP15BEN | CP15屏障启用。如果有实现,则它是AArch32 CP15 DMB,DSB和ISB屏障操作的使能位。 |

| SA0 | EL0中堆栈对齐检查启用。 |

| SA | 堆叠对齐检查启用。 |

| C | 数据缓存启用。这是EL0和EL1上数据高速缓存的使能位。数据访问可缓存普通内存将被缓存。 |

| A | 对齐检查使能位。 |

| M | 启用MMU。 |

访问SCTLR

要访问SCTLR_ELn,可使用:

MRS <Xt>,SCTLR_ELn //将SCTLR_ELn读入Xt

MSR SCTLR_ELn,<Xt> //将Xt写入SCTLR_ELn

如下例所示:

MRS X0,SCTLR_EL1 //读取系统控制寄存器配置数据

ORR X0,X0,#(1 << 2)//设置[C]位(位[2])启用数据缓存

ORR X0,X0,#(1 << 12)//设置[I]位(位[12])使能指令缓存

MSR SCTLR_EL1,X0 //写入系统控制寄存器配置数据

注意

在任何异常级别启用数据和指令高速缓存之前,必须使处理器中的高速缓存失效。

原文

https://developer.arm.com/products/architecture/a-profile/docs/100878/latest/the-system-control-register

最后

以上就是俭朴啤酒最近收集整理的关于ARMv8-A架构基础之系统控制寄存器ARMv8-A架构基础之系统控制寄存器的全部内容,更多相关ARMv8-A架构基础之系统控制寄存器ARMv8-A架构基础之系统控制寄存器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复