【ESP8266】ESP12S/12F 最小系统设计及typeC自动下载电路设计

0.引言

ESP8266面向物联网应用的,高性价比、高度集成的 Wi-Fi MCU。

芯片ESP8266EX采用的QFN无引脚封装,且需要搭配FLASH使用,以及设计天线;使用起来比较麻烦。

我希望使用起来更加方便,便想到了使用ESP12S/12F这种集成模组(集成FLASH、天线)。

我只需设计一个最小系统及typeC自动下载电路设计,就可以愉快的用到自己的项目中了。

解决两个问题:

1.设计最小系统

2.type C自动下载电路

本文目录

- 【ESP8266】ESP12S/12F 最小系统设计及typeC自动下载电路设计

- 0.引言

- 1.ESP8266 介绍

- 2.ESP12S设计的关键信息

- 2.1.ESP12S原理图

- 2.2.封装尺寸

- 2.3.ESP12S符号及管脚定义、PCB封装

- 2.3.1.ESP12S符号

- 2.3.2.ESP12S管脚功能说明

- 2.3.3.模组启动模式的管脚电平要求

- 2.3.4.PCB封装

- 3.最小系统电路设计

- 3.1.原理图

- 3.2.最小系统解释

- 4.type C自动下载电路设计

- 4.1.自动下载电路原理图

- 4.2.自动下载电路解析

- 4.2.1 Type C接口

- 4.2.1.1 Type C管脚定义

- 4.2.1.2 Type C 选型

- 4.2.1.3. Type C 16Pin接线总结

- 4.2.1.4.16Pin typeC接线图

- 4.2.2.CH340芯片

- 4.2.2.1 CH340介绍

- 4.2.2.2.CH340引脚定义

- 4.2.1.3.CH340C接线图

- 4.2.3.自动下载实现

- 4.2.3.1.自动下载时序

- 4.2.3.2.自动下载关键电路

- 5.打样及实验验证

1.ESP8266 介绍

- ESP8266EX 乐鑫官网的简介图

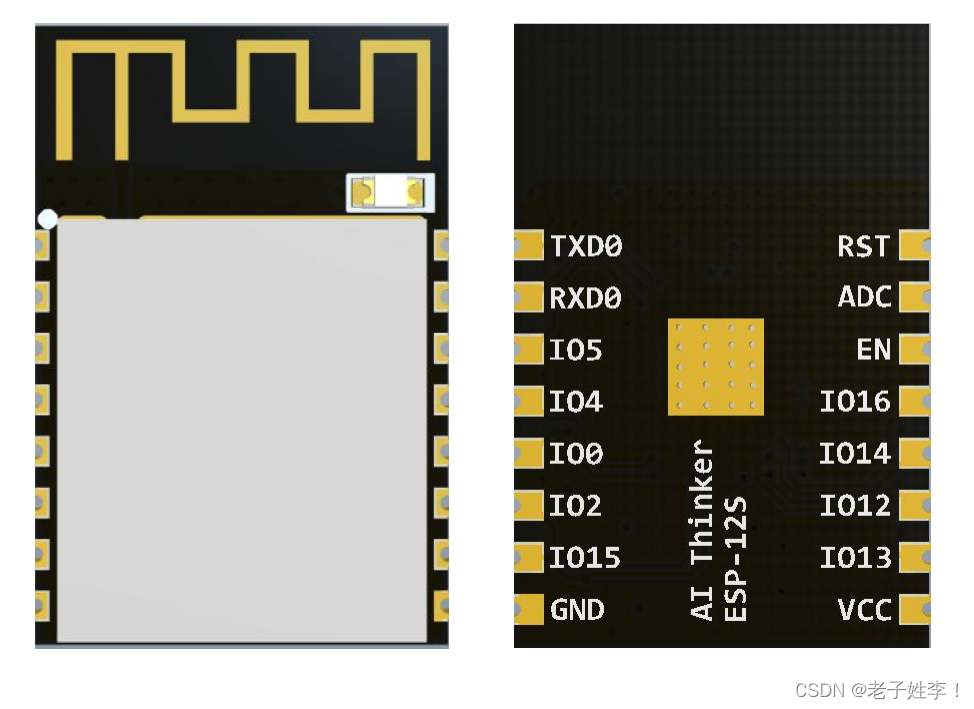

- ESP12S模组

ESP12S和ESP12F模组,主要是封装不同,其他没什么大的区别。

ESP-12S 是由安信可公司开发的 Wi-Fi 模块,基于ESP8266EX高性能无线 SoC。该模块在较小尺寸封装中囊括了晶振、FLASH、天线等元件。支持80MHz和160MHz主频,完整的 TCP/IP 协议栈。该模块既可以嵌入到现有设备添加联网功能,也可以构建独立的网络控制器。

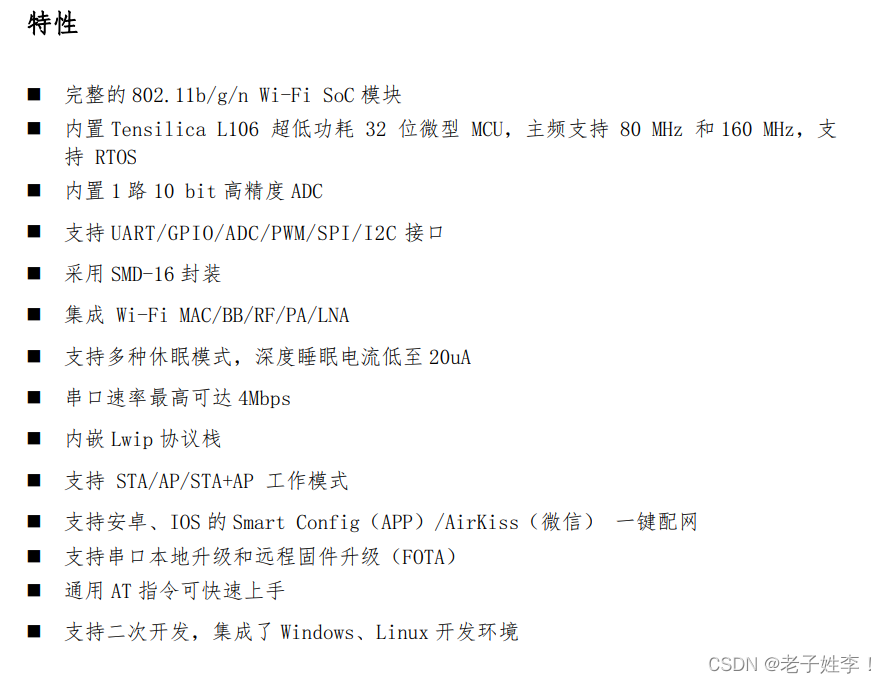

特性介绍如下。

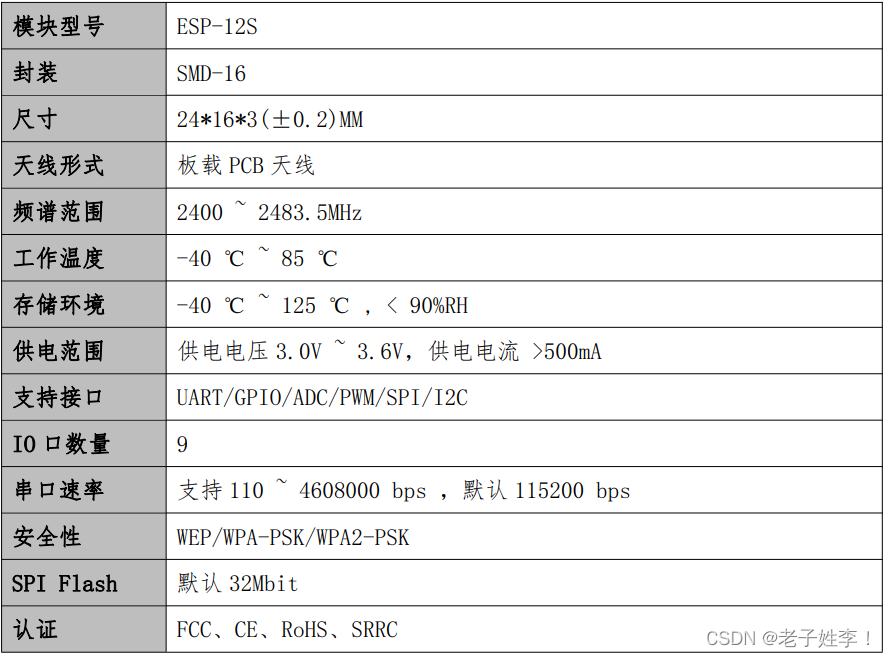

主要参数说明

2.ESP12S设计的关键信息

ESP12S采用SMD16封装,我们要设计的自己电路,需要了解一下模组的原理图、管教定义、封装尺寸等等。

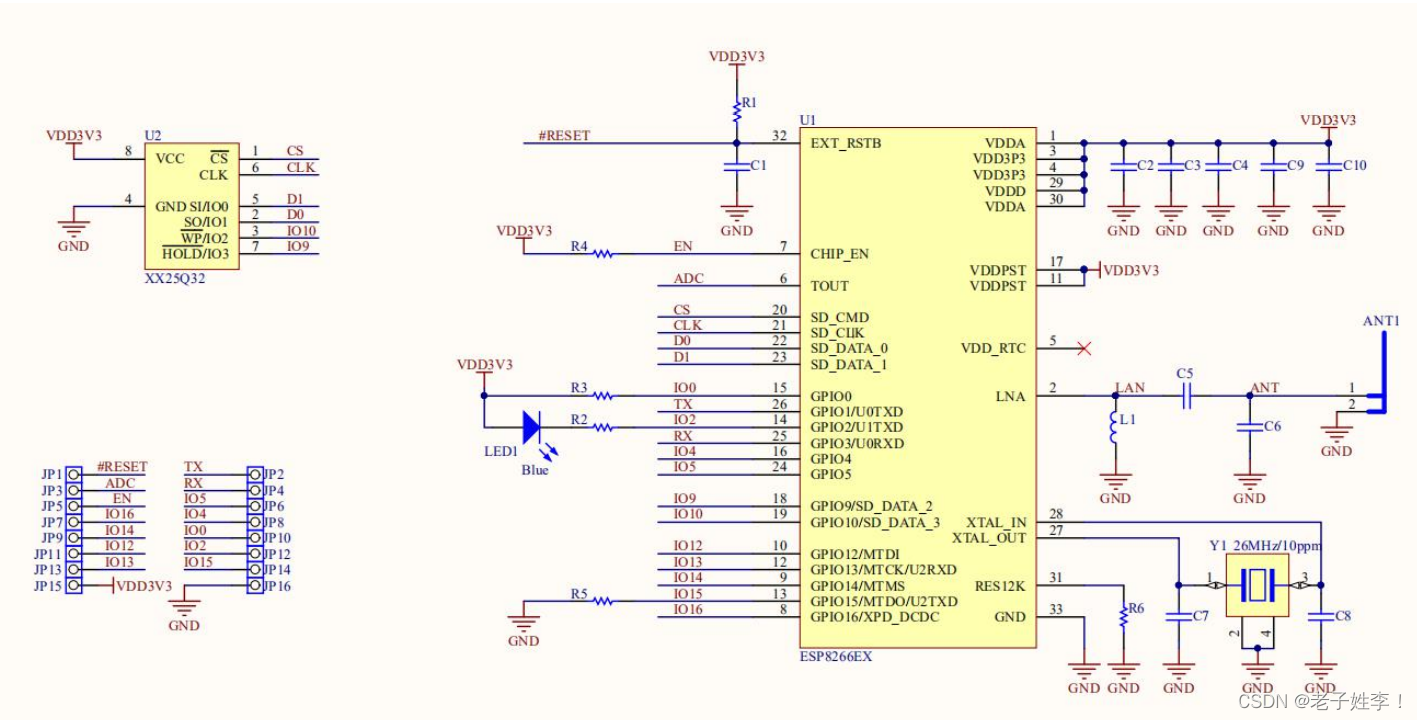

2.1.ESP12S原理图

截取自 规格书。

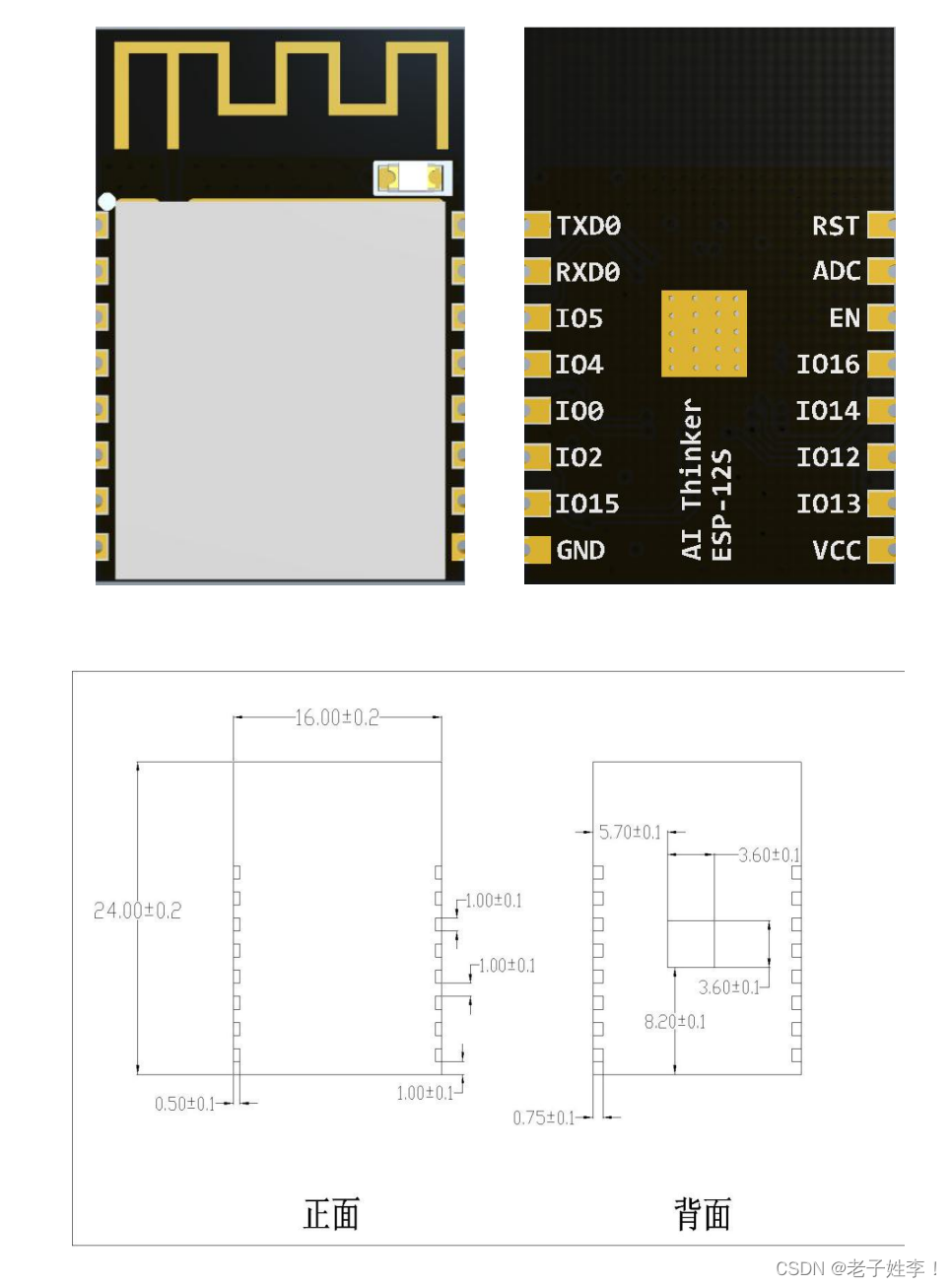

2.2.封装尺寸

实物图,以及尺寸说明。

2.3.ESP12S符号及管脚定义、PCB封装

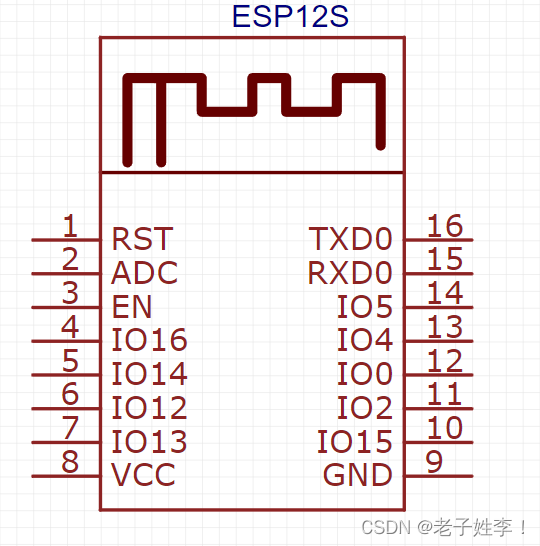

2.3.1.ESP12S符号

2.3.2.ESP12S管脚功能说明

管脚功能说明表:

| 脚序 | 名称 | 功能说明 |

|---|---|---|

| 1 | RST | 复位引脚,低电平有效 |

| 2 | ADC | A/D 转换结果。输入电压范围 0~1V,取值范围:0~1024 |

| 3 | EN | 芯片使能端,高电平有效 |

| 4 | IO16 | GPIO16,与 RST 管脚相连时可做 deep sleep 的唤醒 |

| 5 | IO14 | GPIO14/HSPI_CLK/IR_T/IC_SCL/I2SI_WS |

| 6 | IO12 | GPIO12/HSPI_MISO |

| 7 | IO13 | GPIO13/HSPI_MOSI/UART0_CTS |

| 8 | VCC | 3.3V VDD;外部供电电源输出电流建议在 500mA 以上 |

| 9 | GND | 接地 |

| 10 | IO15 | GPIO15/I2SO_BCK/HSPICS/UART0_RTS |

| 11 | IO2 | GPIO2/UART1_TXD/I2C_SDAˈI2SO_WS |

| 12 | IO0 | GPIO0下载模式:外部拉低,运行模式:悬空或者外部拉高 |

| 13 | IO4 | GPIO4 |

| 14 | RXD | UART0_RXD/GPIO3/I2SO_DATA |

| 15 | IO5 | GPIO5/IR_R |

| 16 | TXD | UART0_TXD/GPIO1 |

2.3.3.模组启动模式的管脚电平要求

模组启动模式,对应的管脚电平要求说明。

| 模式 | CH_PD(EN) | RST | GPIO15 | GPIO0 | GPIO2 | TXD0 |

|---|---|---|---|---|---|---|

| 下载模式 | 高 | 高 | 低 | 低 | 高 | 高 |

| 运行模式 | 高 | 高 | 低 | 高 | 高 | 高 |

总结:

主要是GPIO0电平不同(低:下载;高:运行)。

其他管脚的高低电平使用上拉或下拉电阻控制。(见,前面的原理图)

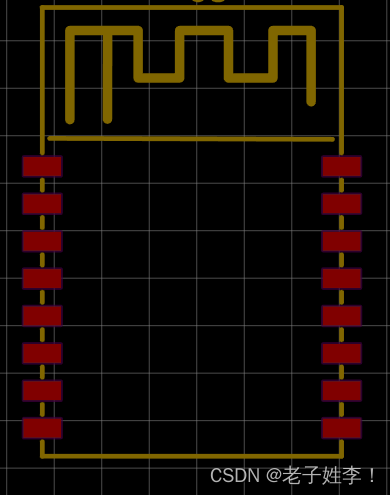

2.3.4.PCB封装

3.最小系统电路设计

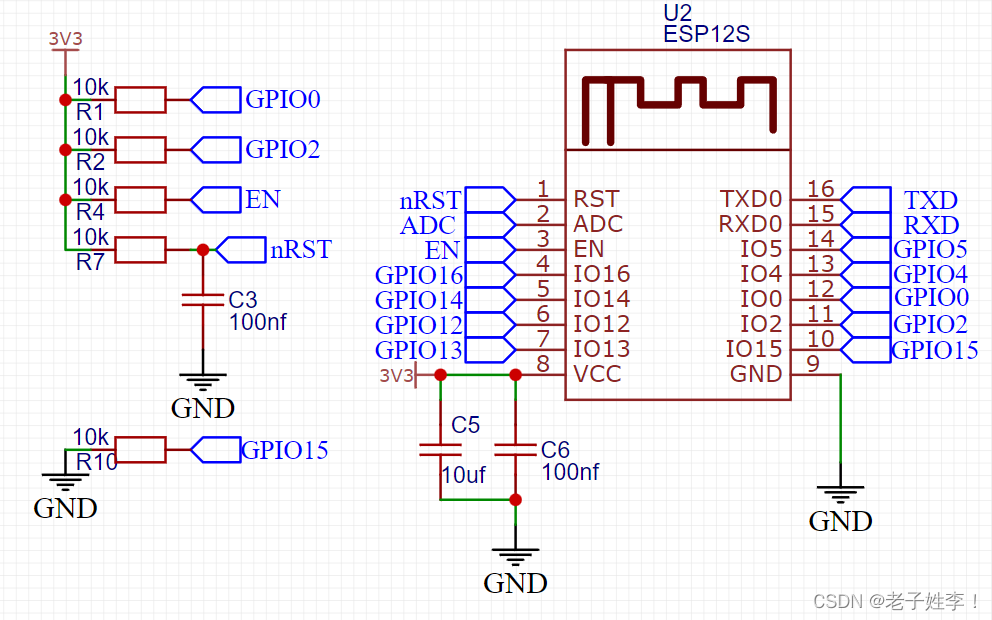

3.1.原理图

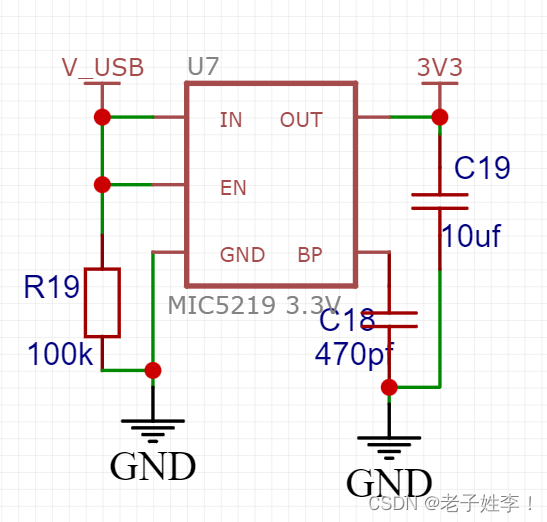

采用LDO供电。将USB输入的5V降压到3.3V,给系统供电。

3.2.最小系统解释

参考引脚定义以及启动模式要求,依据推荐的应用电路设计,

ESP12S模组原理图并未说明上下拉电阻的大小,还是再加了一些上下拉电阻。

实测可以正常运行。(理论上,不加上下拉电阻也可以)

4.type C自动下载电路设计

自动下载实现思路:

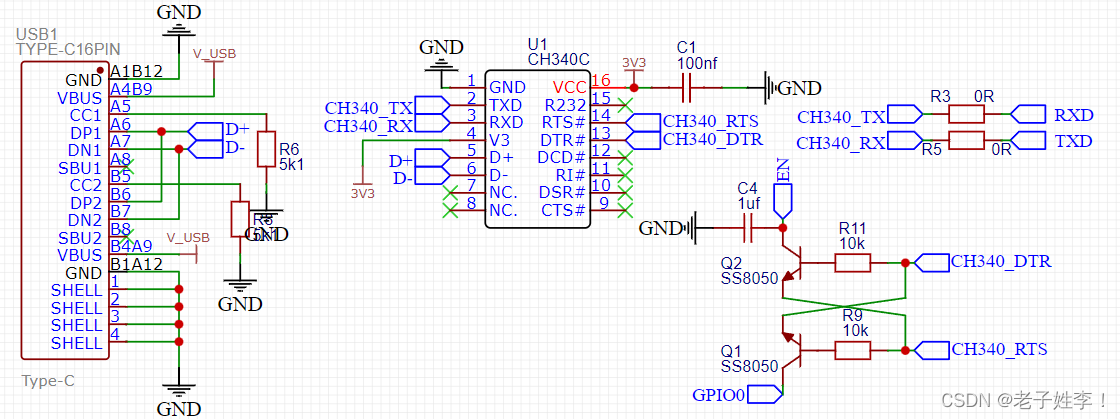

使用CH340芯片将Type C的USB信号转换为TTL串口信号;

用DTR和RTS流控信号引脚,将ESP8266由运行模式变更为下载模式,这样就可以自动进入固件烧录而不需要手动复位等操作。

4.1.自动下载电路原理图

4.2.自动下载电路解析

4.2.1 Type C接口

4.2.1.1 Type C管脚定义

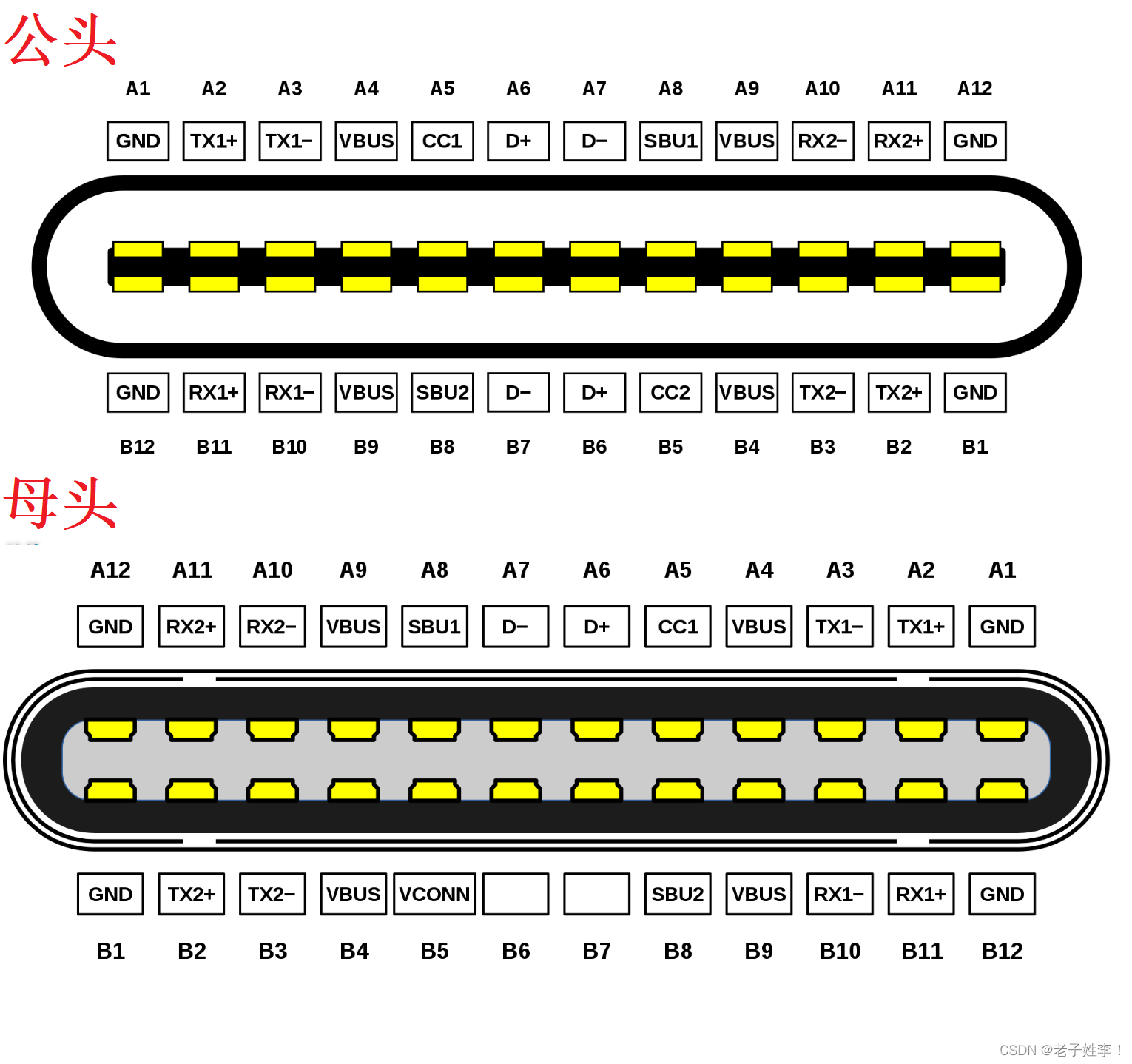

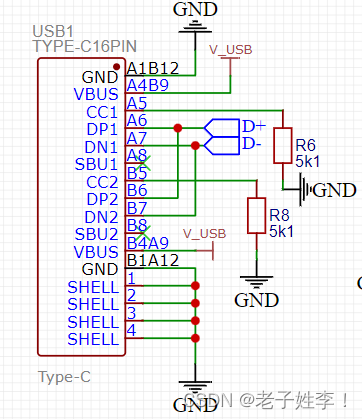

type c全功能有24pin,上下各12个。(如下图所示)

引脚功能定义

| Pin | 名称 | 功能描述 | Pin | 名称 | 功能描述 |

|---|---|---|---|---|---|

| A1 | GND | 接地 | B12 | GND | 接地 |

| A2 | SSTXp1 | SuperSpeed差分信号#1,TX,正 | B11 | SSRXp1 | SuperSpeed差分信号#1,RX,正 |

| A3 | SSTXn1 | SuperSpeed差分信号#1,TX,负 | B10 | SSRXn1 | SuperSpeed差分信号#1,RX,负 |

| A4 | VBUS | 总线电源 | B9 | VBUS | 总线电源 |

| A5 | CC1 | Configurationchannel | B8SBU2 | Sideband | use(SBU) |

| A6 | Dp1 | USB2.0差分信号,position1,正 | B7 | Dn2 | USB2.0差分信号,position2,负 |

| A7 | Dn1 | USB2.0差分信号,position1,负 | B6 | Dp2 | USB2.0差分信号,position2,正 |

| A8 | SBU1 | Sidebanduse(SBU) | B5 | CC2 | Configurationchannel |

| A9 | VBUS | 总线电源 | B4 | VBUS | 总线电源 |

| A10 | SSRXn2 | SuperSpeed差分信号#2,RX,负 | B3 | SSTXn2 | SuperSpeed差分信号#2,TX,负 |

| A11 | SSRXp2 | SuperSpeed差分信号#2,RX,正 | B2 | SSTXp2 | SuperSpeed差分信号#2,TX,正 |

| A12 | GND | 接地 | B1 | GND | 接地 |

4.2.1.2 Type C 选型

这里只是用作MCU的USB 2.0下载电路,用不上全功能的24Pin的typeC;而6Pin的没有usb 2.0的通信引脚,一般只用作给MCU供电。

故采用16pin的TypeC接口最为合适。(实际只有12个焊盘,因为VBUS、GND对应合并成一个大焊盘)

16Pin TypeC在24Pin的基础上阉割了USB3.0的TX1/2、RX1/2,其他功能上区别不大,同样支持 PD快充、音频设备、HDMI传输、调试模式等功能。

当然,16Pin TypeC在价格、焊接难度上,比24Pin会更友好一些。

4.2.1.3. Type C 16Pin接线总结

16Pin Type C接线总结,如下表格所示。

| 名称 | 功能 | 接线说明 |

|---|---|---|

| VBUS | 电源总线 | USB输入的电源,接网络V_USB |

| GND | 地 | 接GND |

| CC1 | Configurationchannel | 5.1k下拉电阻接GND |

| CC2 | Configurationchannel | 5.1k下拉电阻接GND |

| Dp1 | USB2.0差分信号,position1,正 | 接差分正极,网络D+ |

| Dn1 | USB2.0差分信号,position1,负 | 接差分负极,网络D- |

| SBU1 | Sidebanduse(SBU) | 用不上悬空 |

| SBU2 | Sidebanduse(SBU) | 用不上悬空 |

| SHELL | 外壳的四个固定引脚 | 接GND |

4.2.1.4.16Pin typeC接线图

注意:

做从机:CC1、CC2接5.1K电阻接地;做主机时:CC1、CC2接上拉电阻VBUS。

MCU这里用做从机,PC作主机。

4.2.2.CH340芯片

4.2.2.1 CH340介绍

CH340 是一个 USB 总线的转接芯片,实现 USB 转串口或者 USB 转打印口。

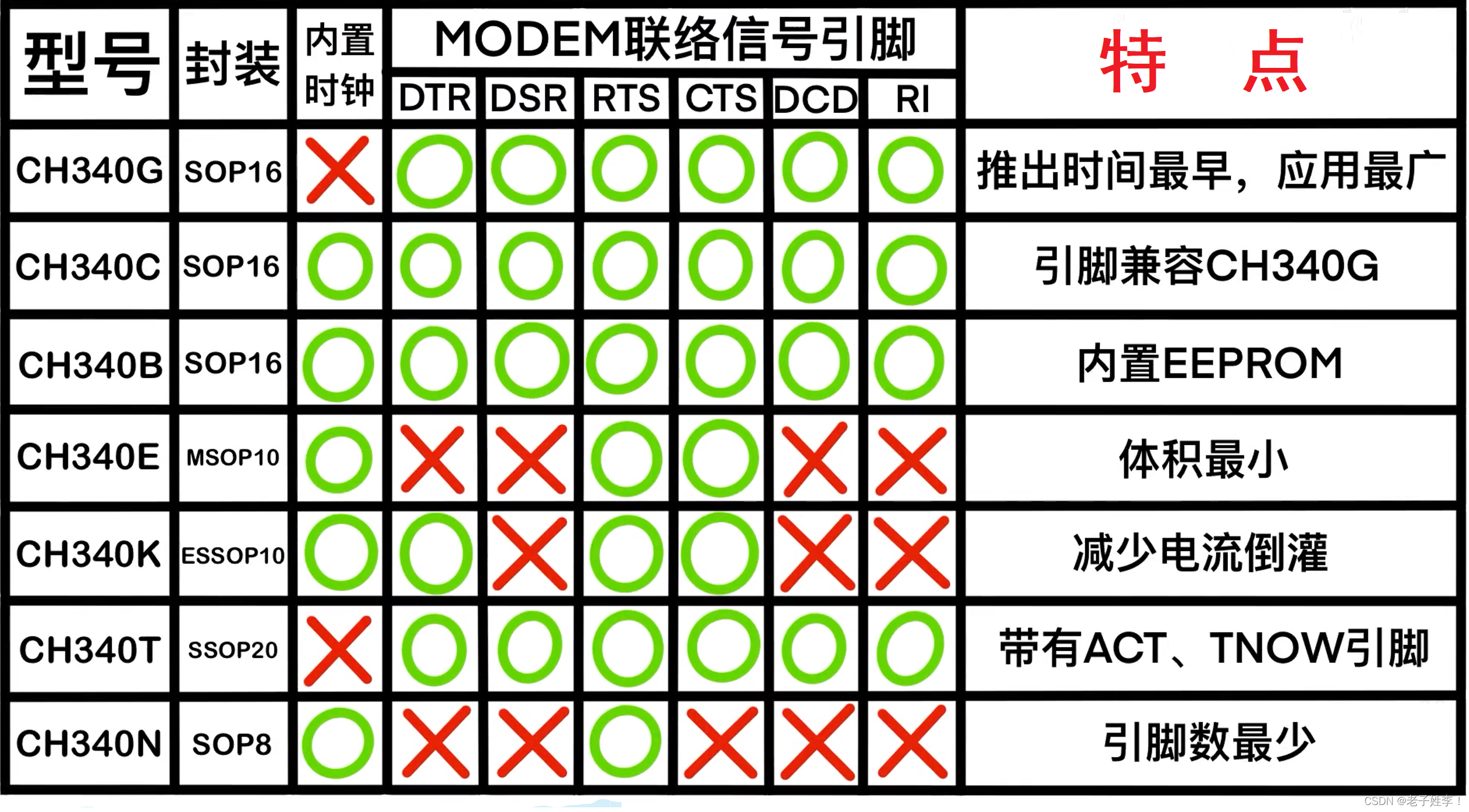

常用ch340封装总结如下。

实现自动下载电路需要用到DTR和RTS流控引脚,推荐使用CH340K芯片。由于CH340K比较贵,所以还是采用CH340C全功能的芯片。

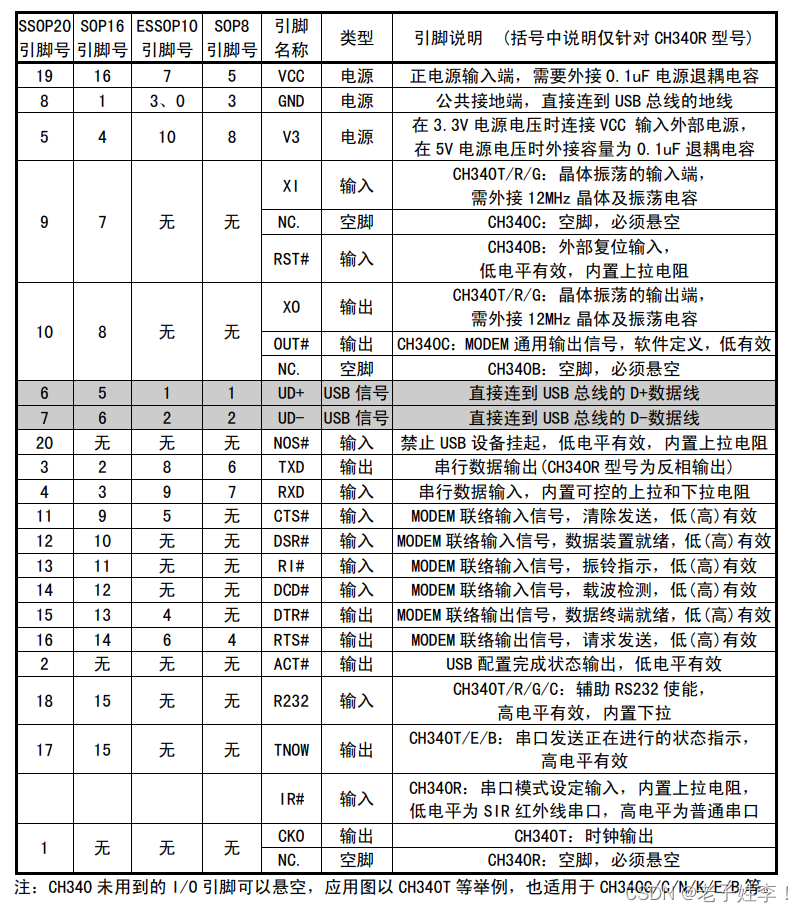

4.2.2.2.CH340引脚定义

规格书中引脚定义如下。

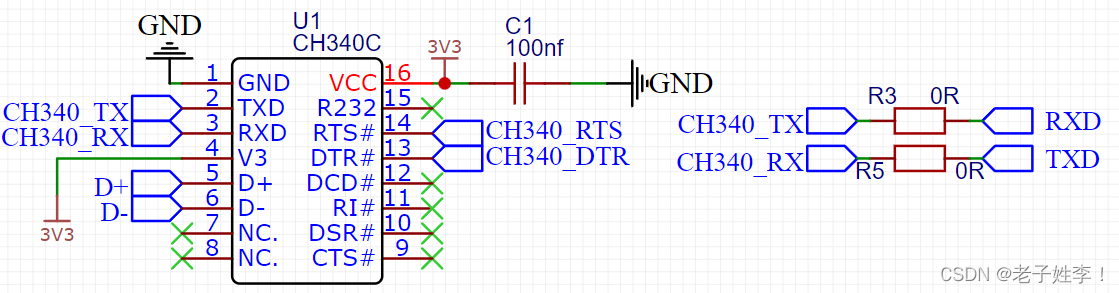

4.2.1.3.CH340C接线图

根据上面的CH340C引脚定义,接线图如下。

注意:

ESP12S采用3.3V供电,CH340C建议也保持一致,避免5V的串口信号损坏ESP12S里面的芯片。

4.2.3.自动下载实现

4.2.3.1.自动下载时序

ESP8266EX 的 Pin7 CHIP_EN 为使能管脚,当为低电平时,ESP8266EX 会下电。此管脚

也可作为复位管脚,当输⼊电平低于 0.6 V 并持续 200 μs 以上时,ESP8266EX 会重启。

推荐使⽤ CHIP_EN 进⾏芯⽚复位。

使用DTR和RTS引脚,控制GPIO0和EN(CHIP_EN)实现自动下载。

自动下载的时序图。

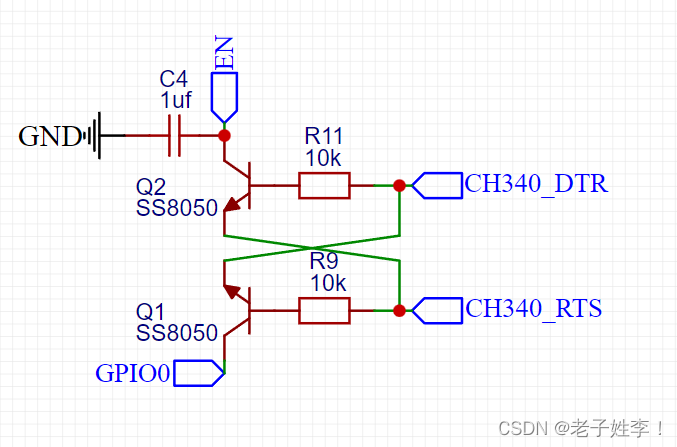

4.2.3.2.自动下载关键电路

注意EN引脚必须接一个电容和一个上拉电阻,形成RC电路,借助电容充放电,延时EN达到高低电平的时间,以满足时序图的要求。

在下图中,C4 1uf(也可以选择10uf),10k的上拉电阻在ESP12S模组旁边。

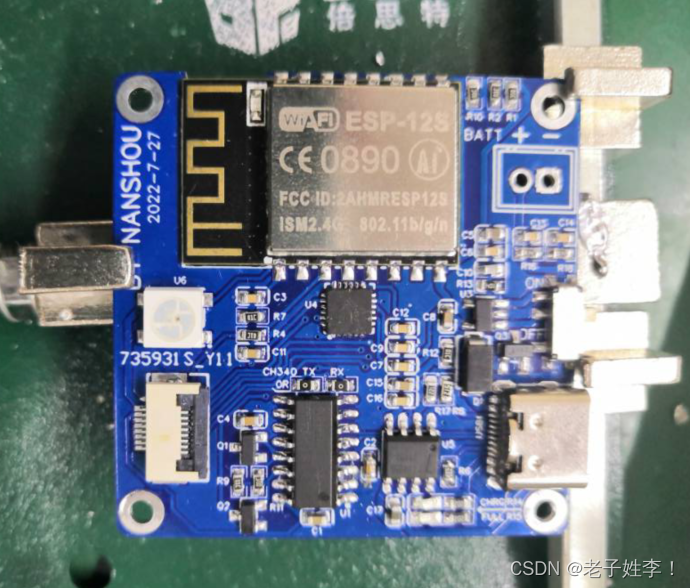

5.打样及实验验证

打样的电路如下:

烧录验证参考:【ESP8266 快速入门】0.详细步骤-Arduino IDE开发环境搭建(基于安信可NodeMCU、C/C++)

根据上面的参考,搭建好开发Arduino IDE环境,烧录Blink例程。

成功烧录,且ESP12S板子LED正常闪烁。

最后

以上就是纯真大炮最近收集整理的关于【ESP8266】ESP12S/ESP12F最小系统设计及typeC自动下载电路设计的全部内容,更多相关【ESP8266】ESP12S/ESP12F最小系统设计及typeC自动下载电路设计内容请搜索靠谱客的其他文章。

发表评论 取消回复