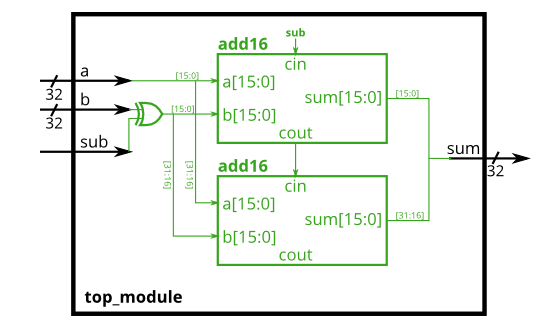

要实现一个32位的加减器,加减由变量sub来决定,sub为0时,实现add,否则,实现sub。

输入输出变量有:

input [31:0] a,

input [31:0] b,

input sub,

input cin,

output cout,

output [31:0] out;

要实现相加,则a和b相加;要实现相减,则a加上-b的补码。

相减,在数字电路中,可以用加法器实现,也即a加上-b的补码,-b的补码等于b取反加1;

具体实现方法参考:addsub

具体的Verilog实现为:

module top_module(

input [31:0] a,

input [31:0] b,

input sub,

output [31:0] result

);

wire [31:0] sub1, sub2;

wire [31:0] b1;

//assign sub1 = 32'b0;

//assign sub2 = 32'b1;

//assign b1 = sub ? b^sub2 : b^sub1;

assign b1 = sub ? ( b^( {32{sub}} ) ) : ( b^( {32{sub}} ) );

wire [15:0] sum1, sum2;

wire cout1;

add16 inst1(

.cin(sub),

.a(a[15:0]),

.b(b1[15:0]),

.cout(cout1),

.sum(sum1)

);

add16 inst2(

.cin(cout1),

.a(a[31:16]),

.b(b1[31:16]),

.cout(),

.sum(sum2)

);

assign result = {sum2, sum1};

endmodule

其中16位的数据加法为:

module add16(

input [15:0] a,

input [15:0] b,

input cin,

output cout,

output [15:0] sum

);

assign {cout, sum} = a + b + cin;

endmodule当然,可以采用先进进位加法器,怎么实现可以参考:https://blog.csdn.net/Reborn_Lee/article/details/99634895

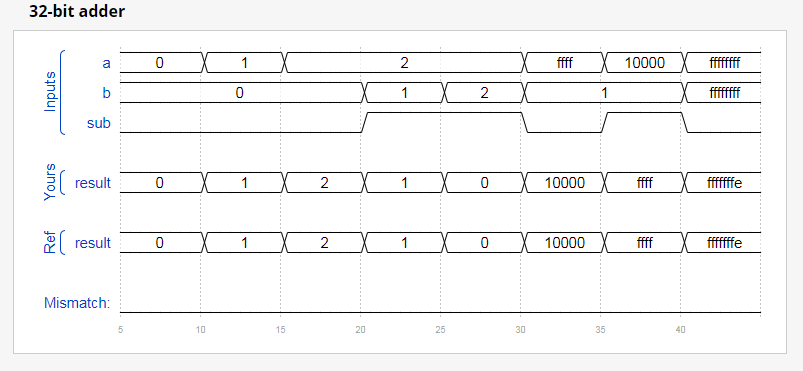

仿真结果为:

最后

以上就是娇气豆芽最近收集整理的关于【 FPGA/IC 】addsub 的实现的全部内容,更多相关【内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复