(EDA工具未完待续)

(EDA工具未完待续)

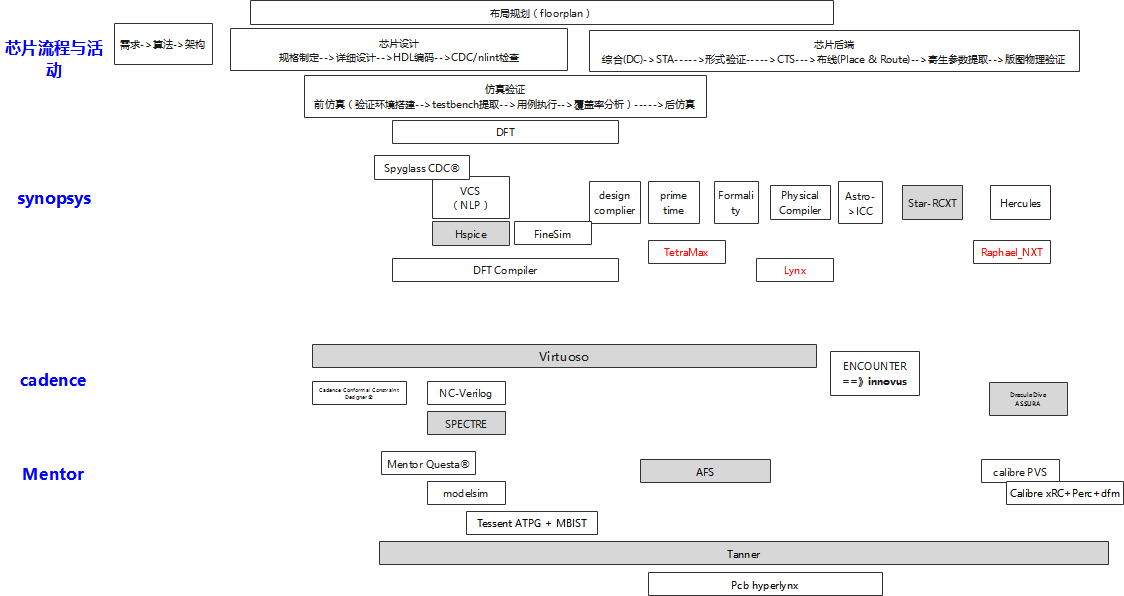

Synopsys:

1、spyglass:CDC相关工具。CDC,跨时钟域设计,是设计工作中很重要的技术点。

2、VCS工具:verilog仿真工具。

3、design complier-NXT:综合工具。综合需要具备的知识:综合概念和流程、库文件类别、时序约束的基本知识,多时钟与复杂设计约束、DC Ultra综合技巧、SPG flow,DC工具进行综合基本操作、编写综合约束文件、综合结果的时序和congestion分析等贯穿综合全流程的实践技能。详情请见:https://mp.weixin.qq.com/s/0vO763XfCSoSqt-gloegpA

4、Prime Time:静态时序分析工具和SI工具。静态时序分析(Static Timing Analysis,STA)是流片成功的关键环节,验证设计在时序上的正确性。STA过程中设计环境和时序约束的设定、时序结果的分析和问题解决都需要设计工程师具有专门的知识和技能。同时,集成电路设计进入了超深亚微米领域,金属层增加、线宽减小,串扰延迟、噪声等信号完整性问题(SI)对工程师的时序分析能力和水平要求越来越高,在一些大的芯片设计企业会设置有专门的信号完整性工程师岗。静态时序分析要具备的知识:时序分析概念和流程、时序约束含多时钟约束、时序报告、PBA等,熟练使用EDA工具Prime Time进行时序分析和sign-off,掌握识别不完整/不正确约束、高效分析与调试的方法和实践技巧。详情请见:https://mp.weixin.qq.com/s/_Rlr2k6s4TakfjkDOdbjTg

5、Formality:等价性验证工具。

6、ICC(老版本:Astro):布局布线工具。数字后端布局布线(P&R,place-and-route)是Netlist-to-GDSII的过程,是决定能否流片的首要前提,也直接关系到芯片设计时序收敛、PPA、可制造性与良品率等。P&R对工具的依赖性较强,工具操作相对复杂。后端工程师要具备的知识:布局布线所需的工艺文件与库、floorplan、CTS、place、route、MCMM等,熟练使用EDA工具IC Compiler II进行布局布线各阶段的设置与优化,掌握congestion改善、时钟树分析、全局和布局skew优化、timing violation fixing、功能和时序ECO等技巧。详情请见:https://mp.weixin.qq.com/s/wLlBRAkYmkwHBJboPH-mcg

7、Star-RCXT:寄生参数提取工具。

8、Hspice:模拟仿真工具;

Cadence:

1、Virtuoso:电路及版图设计工具。

2、NC-Verilog:verilog仿真工具。

3、innovus(ENCOUNTER):自动布局布线工具。

4、PVS:物理验证工具。

5、SPECTRE:模拟仿真工具。

Mentor:

1、modelsim:verilog仿真工具。

2、calibre:https://tech.hqew.com/xinpin_1898184

3、AFS:快速模拟仿真工具。

4、Tanner:Mentor Graphics的Tanner EDA软件是一套针对定制集成电路(IC)、模拟/混合信号(AMS)和MEMS设计的工具。

注:若有错误请指正,共同提升,谢谢;

最后

以上就是慈祥红酒最近收集整理的关于芯片开发流程对应的三大EDA厂商工具的全部内容,更多相关芯片开发流程对应内容请搜索靠谱客的其他文章。

发表评论 取消回复