模块代码

module mealy(

input wire clk,

input wire rst_n,

input wire a,

output reg k

);

parameter S1 = 6'b000_001;

parameter S2 = 6'b000_010;

parameter S3 = 6'b000_100;

parameter S4 = 6'b001_000;

parameter S5 = 6'b010_000;

parameter S6 = 6'b100_000;

reg [5:0] curr_st;

always @(posedge clk or negedge rst_n)

if(rst_n == 1'b0)

curr_st <= S1;

else

case(curr_st)

S1:if(a == 1'b1)

curr_st <= S2;

else

curr_st <= S1;

S2:if(a == 1'b1)

curr_st <= S3;

else

curr_st <= S1;

S3:if(a == 1'b1)

curr_st <= S4;

else

curr_st <= S1;

S4:if(a == 1'b0)

curr_st <= S5;

S5:if(a == 1'b1)

curr_st <= S6;

else

curr_st <= S1;

S6:curr_st <= S1;

default:curr_st <= S1;

endcase

always @(posedge clk or negedge rst_n)

if(rst_n == 1'b0)

k <= 1'b0;

else if(curr_st == S5 && a == 1'b1)

k <= 1'b1;

else

k <= 1'b0;

endmodule

仿真文件

`timescale 1ns/1ns

module mealy_tb;

reg sclk;

reg rst_n;

reg a_in;

wire k_out;

initial begin

sclk = 0;

rst_n = 0;

#200

rst_n = 1;

end

always #10 sclk <= ~sclk;

initial begin

#200

rand_bit();

end

mealy mealy_inst(

.clk (sclk),

.rst_n (rst_n),

.a (a_in),

.k (k_out)

);

task rand_bit();

integer i;

begin

for(i=0;i<255;i=i+1)

begin

@(posedge sclk);

// a_in <= $random %10 ; //产生-10 ..9

// a_in <= {$random} %10; //产生0 ..9

a_in <= {$random} %2 ; //产生0 1

end

end

endtask

endmodule

modsim脚本文件

#退出当前仿真

quit -sim

#清除命令行显示信息

.main clear

#创建文件夹

vlib ./lib

vlib ./lib/work_a/

vlib ./lib/design/

#映射逻辑库base_space到指定路径work_a

vmap base_space ./lib/work_a/

#映射逻辑库design到指定路径design

vmap design ./lib/design/

#编译指定路径的代码文件到base_space库中

vlog -work base_space ./mealy_tb.v

#编译指定路径的代码文件到design库中

vlog -work design ./../design/*.v

#启动仿真

#-t 运行仿真的时间精度是ns

#-L 链接库

#指定base_space路径下的mealy_tb为顶层文件

vsim -t ns -voptargs=+acc -L base_space -L design base_space.mealy_tb

#添加虚拟信号

#创建枚举对照表 注意virtual type+空格+{ }+空格+vir_new_signal

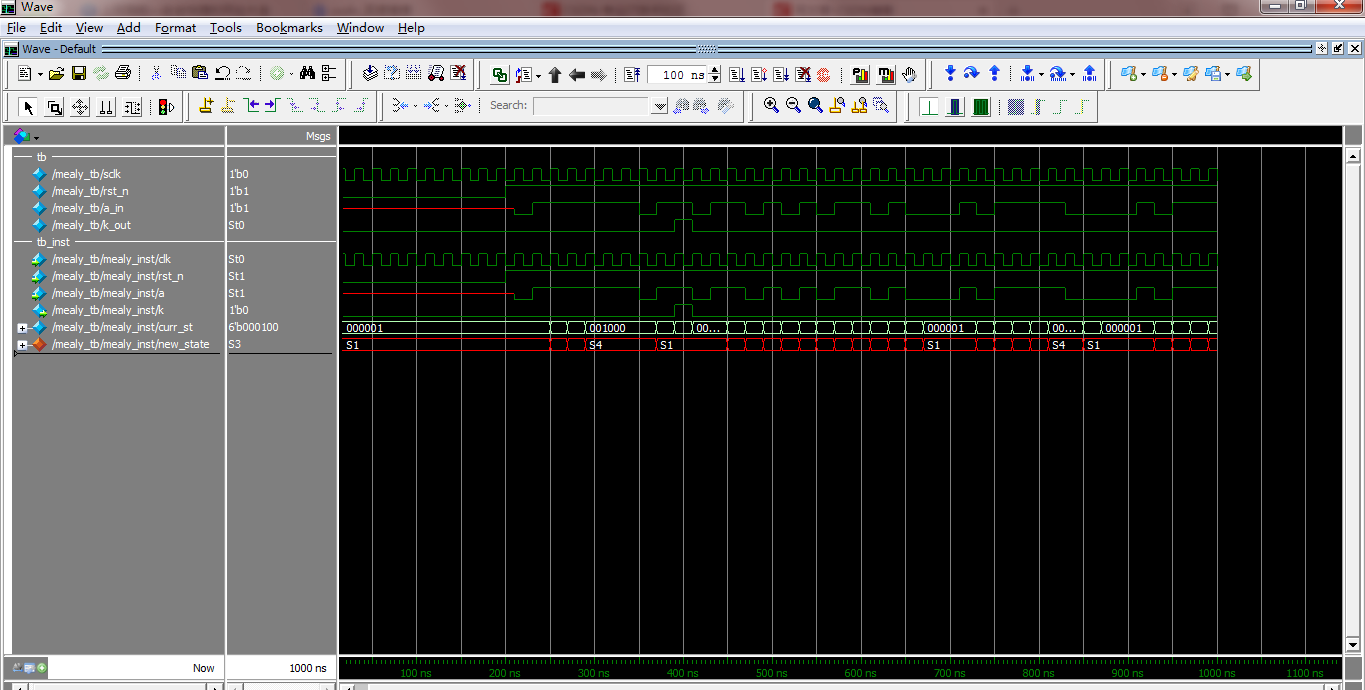

virtual type {

{01 S1}

{02 S2}

{04 S3}

{08 S4}

{10 S5}

{20 S6}

} vir_new_signal

#区分模块 tb随意取名

add wave -divider {tb}

#匹配mealy下的所有信号 *为通配符

add wave mealy_tb/*

#区分模块 tb_1随意取名

add wave -divider {tb_inst}

#通配符匹配所用信号

add wave mealy_tb/mealy_inst/*

#创建一个vir_new_signal类型信号,也就是把curr_st进行类型转换

virtual function {(vir_new_signal) mealy_tb/mealy_inst/curr_st} new_state

add wave -color red mealy_tb/mealy_inst/new_state

#启动仿真

run 1us

最后

以上就是俭朴溪流最近收集整理的关于11101序列检测状态机(含有仿真do文件)的全部内容,更多相关11101序列检测状态机(含有仿真do文件)内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复