设计一个序列检测器。要求检测器连续收到串行码1110后,输出检测标志1,否则输出0。

Mealy型状态机输出是由现状态和输入决定。

状态机设计步骤:

1.分析设计要求,列出全部可能状态;

2.画出状态转移图;

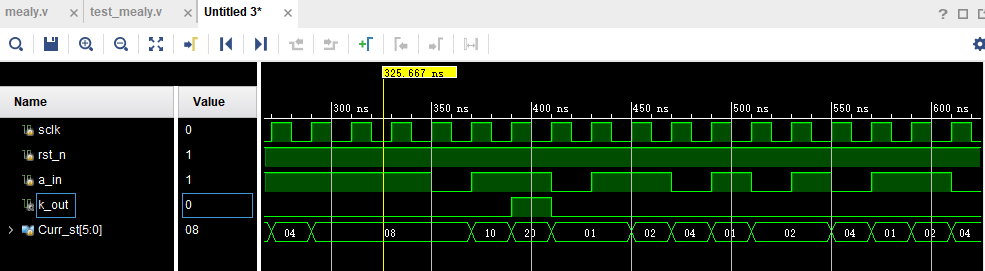

3.用Verilog hdl描述状态机,编写testbench验证。

`timescale 1ns / 1ps

module mealy(

input wire clk,

input wire rst_n,

input wire A,

output reg K

);

parameter S1 = 6'b00_0001;

parameter S2 = 6'b00_0010;

parameter S3 = 6'b00_0100;

parameter S4 = 6'b00_1000;

parameter S5 = 6'b01_0000;

parameter S6 = 6'b10_0000;

reg [5:0] Curr_st;

reg [5:0] Next_st;

// always @*

// Curr_st = Next_st;

always @(posedge clk or negedge rst_n)

if(rst_n == 1'b0)

Curr_st <= S1;

else

case(Curr_st)

S1:if(A == 1'b1)

Curr_st <= S2;

else

Curr_st <= S1;

S2:if(A == 1'b1)

Curr_st <= S3;

else

Curr_st <= S2;

S3:if(A == 1'b1)

Curr_st <= S4;

else

Curr_st <= S1;

S4:if(A == 1'b0)

Curr_st <= S5;

S5:if(A == 1'b1)

Curr_st <= S6;

else

Curr_st <= S1;

S6:Curr_st <= S1;

default:Curr_st <= S1;

endcase

always @(posedge clk or negedge rst_n)

if(rst_n == 1'b0)

K <= 1'b0;

else if(Curr_st == S5 && A == 1'b1)

K <= 1'b1;

else

K <= 1'b0 ;

endmodule

testbench文件

`timescale 1ns / 1ps

module test_mealy();

reg sclk,rst_n;

reg a_in;

wire k_out;

initial begin

sclk =0;

rst_n=0;

#100 rst_n=1;

end

initial begin

#200;

rand_bit();

end

always #10 sclk <= ~sclk;

mealy mealy_inst(

.clk (sclk),

.rst_n (rst_n),

.A (a_in),

.K (k_out)

);

task rand_bit();

integer i;

begin

for(i=0;i<255;i=i+1)

begin

@(posedge sclk)

a_in <= {$random} %2;

end

end

endtask

endmodule

最后

以上就是机智铃铛最近收集整理的关于mealy状态机序列检测器设计的全部内容,更多相关mealy状态机序列检测器设计内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复