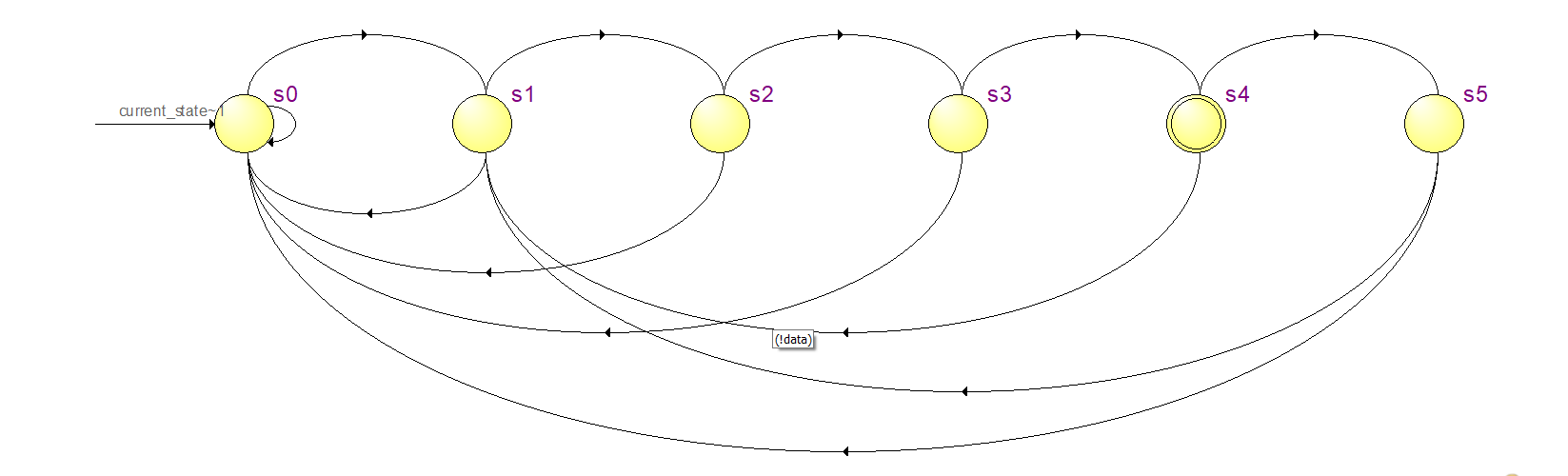

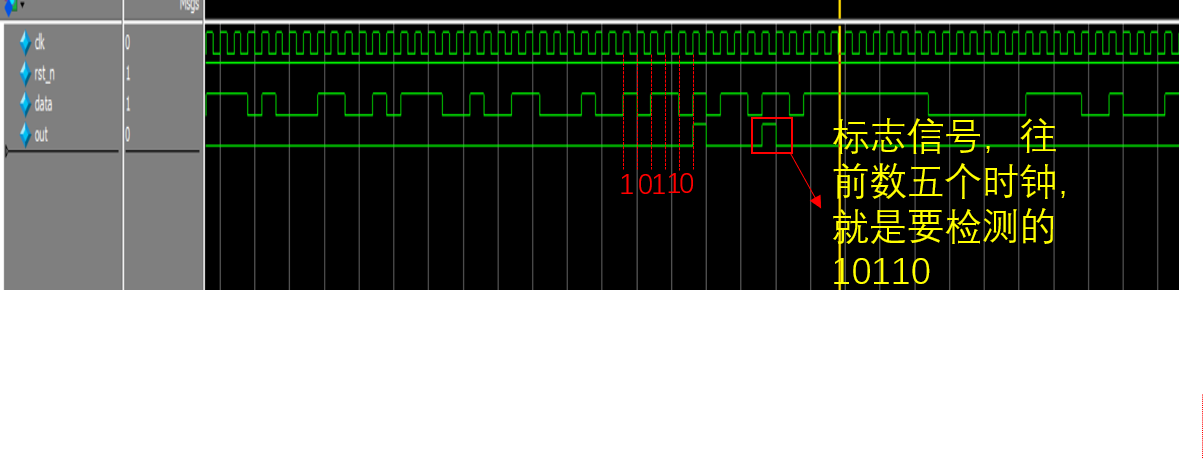

1、用3段状态机设计,请给出序列检测码“10110”的检测状态图和verilog code

2.代码实现

/*----------------------------------------------

Filename: sequential_detector.v

Function: 检测输入数据中的存在的10110序列

Date: 2021-7-25

----------------------------------------------*/

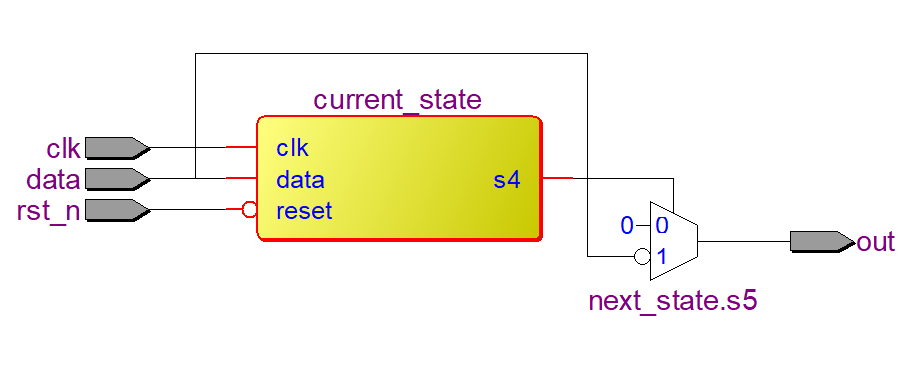

module sequential_detector(clk, rst_n, data, out);

//输入输出端口定义

input clk, rst_n, data;

output reg out; //完成标志位:1

reg [2:0]next_state, current_state; //定义下一状态、当前状态寄存器

//状态编码

parameter s0 = 3'b000, s1 = 3'b001, s2 = 3'b010, s3 = 3'b011,

s4 = 3'b100, s5 = 3'b101;

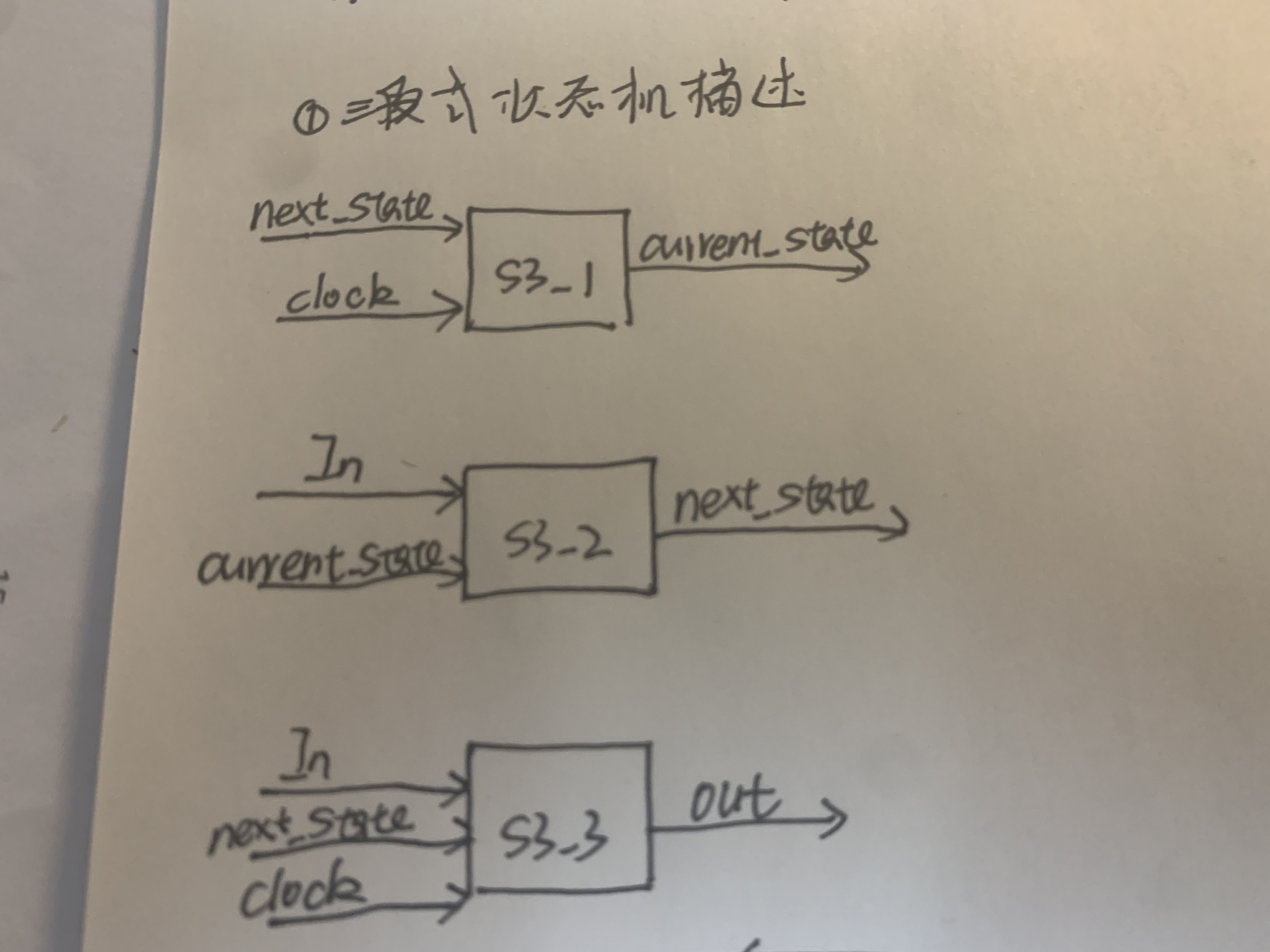

//第一个进程,同步时序always模块,格式化描述次态寄存器迁移到现态寄存器

always@(posedge clk or negedge rst_n)

begin : FSM_3_1_CN

if(rst_n == 1'b0)

current_state <= s0;

else

current_state <= next_state;

end

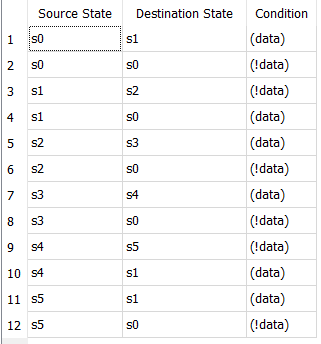

//第二个进程,组合逻辑always模块,描述状态转移条件判断

always@(*)

begin : FSM_3_2_ON

next_state = 3'bx;

case(current_state)

s0: begin

if(data == 1'b1) next_state = s1;

else next_state = s0;

end

s1: begin

if(data == 1'b0) next_state = s2;

else next_state = s0;

end

s2: begin

if(data == 1'b1) next_state = s3;

else next_state = s0;

end

s3: begin

if(data == 1'b1) next_state = s4;

else next_state = s0;

end

s4: begin

if(data == 1'b0) next_state = s5;

else next_state = s1;

end

s5: begin

if(data == 1'b0) next_state = s0;

else next_state = s1;

end

default: next_state = s0;

endcase

end

//第三个进程,同步时序always模块,格式化描述次态寄存器输出

always@(posedge clk or negedge rst_n)

begin : FSM_3_3_CN

if(rst_n == 1'b0)

out<= 1'b0;

case(next_state)

s0: out <= 1'b0;

s1: out <= 1'b0;

s2: out <= 1'b0;

s3: out <= 1'b0;

s4: out <= 1'b0;

s5: out <= 1'b1;

default: out <= 1'b0;

endcase

end

endmodule

3、tb文件

/*---------------------------------------------

Filename: sequential_detector_tb.v

Function: 测试sequential_detector模块逻辑功能

Date: 2021-7-25

---------------------------------------------*/

`timescale 1ns/1ns

module sequential_detector_tb();

//定义要观察的的信号

reg clk, rst_n, data;

wire out;

//实例化调用序列检测器模块

sequential_detector sequential_detector_inst(

.clk(clk),

.rst_n(rst_n),

.data(data),

.out(out)

);

//产生是时钟信号

initial clk = 1'b1;

always #10 clk = ~clk;

initial begin

rst_n = 1'b0;

data = 1'b0;

#200 rst_n = 1'b1;

forever begin

#20 data = {$random} % 2; // 01

end

end

endmodule

最后

以上就是疯狂小懒虫最近收集整理的关于3段状态机设计序列检测器的全部内容,更多相关3段状态机设计序列检测器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复