【温故而知新】【2】时钟分频-奇数50%占空比

昨天写了个时钟分频的Verilog代码,今天继续写,只不过这次写的是:奇数分频,50%占空比

实现方法很简单:

- 计数器,时钟正边沿计数

- 上升沿触发的时钟分频

- 下降沿触发的时钟分频

- 合并上述两种时钟分频信号

Verilog代码如下,依然是参数化的设计:

这里写代码片

//===========================================================

// Author: seuchenrui@126.com

//

// Description:

// This is a simple verilog code for clock frequency division

// this code can be used to get

// 1. odd integer division (duty = 50%)

//===========================================================

module clock_div_odd_50

#(parameter DIV_NUMBER=31)

(

input iCLK,

input iRESET,

output oCLK

);

reg [clogb2(DIV_NUMBER)-1:0] count;

reg tPCLK;

reg tNCLK;

always@(posedge iCLK or negedge iRESET)

begin

if(!iRESET)

count <= 'd0;

else if(count == DIV_NUMBER -1)

count <= 'd0;

else

count <= count + 1'b1;

end

always@(posedge iCLK or negedge iRESET)

begin

if(!iRESET)

tPCLK <= 1'b0;

else if(count == (DIV_NUMBER+1)/2-1)

tPCLK <= ~tPCLK;

else if(count == DIV_NUMBER -1)

tPCLK <= ~tPCLK;

else

tPCLK <= tPCLK;

end

always@(negedge iCLK or negedge iRESET)

begin

if(!iRESET)

tNCLK <= 1'b0;

else if(count == (DIV_NUMBER+1)/2-1)

tNCLK <= ~tNCLK;

else if(count == DIV_NUMBER -1)

tNCLK <= ~tNCLK;

else

tNCLK <= tNCLK;

end

assign oCLK = tPCLK | tNCLK;

//================================

// this function is used to check

// bitwidth of the data

//================================

function integer clogb2;

input [31:0] depth;

begin

for(clogb2 = 0; depth>0;clogb2=clogb2+1)

depth = depth>>1;

end

endfunction

endmodule以下是3分频和17分频的仿真波形:

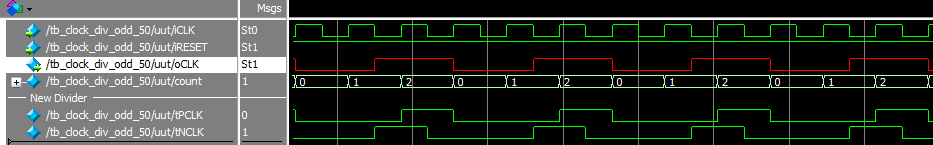

3分频仿真波形

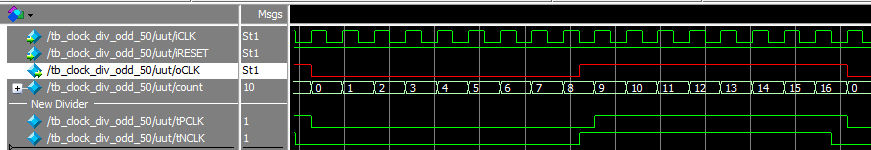

17分频仿真波形

从仿真波形可以看出,代码功能是正确的,可以实现奇数分频,并且是50%占空比的时钟信号。

最后

以上就是平常河马最近收集整理的关于【温故而知新】【2】时钟分频-奇数50%占空比的全部内容,更多相关【温故而知新】【2】时钟分频-奇数50%占空比内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复