本文为明德扬原创文章,转载请注明出处!

本模块的功能,是从一串输入的数据中,检测出指令头55D5,检测出包文头后,获取到紧接着的4个数据(2字节),并按字节为单位送给下游模块。指令头和无效数据则丢弃。

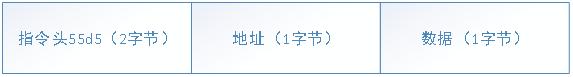

输入的包文指令格式:

输入的数据din为4比特,假设其依次输入:

5、5、d、5、0、2、9、9、1、5、5、d、5、0、1、0、3

其中前两个字节55d5就表示指令头,后一个字节02表示地址,再一个字节99表示数据。紧跟着后面的1为无效数据,往后又检测到55d5,则01为地址,03为数据。把指令头、无效的数据过滤掉(即dout_vld为0),最终输出以字节为单位的02、99、01、03。

一、设计架构

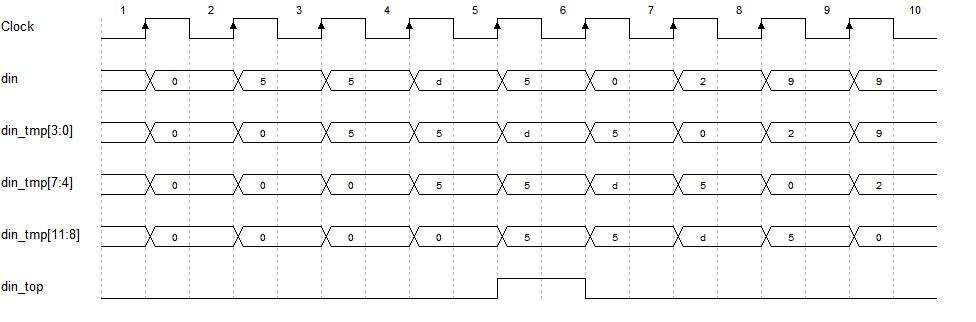

检测出指令头的方法如下:

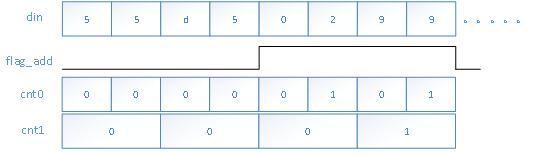

检测出包文头后,需要对后面的4个数据进行计数。每2个数据组成1个字节,一共有2个字节。所以指令检测模块采用两个计数器的结构,这两个计数器分别对应接收一个字节需要的数据个数和接收字节数,其结构图如下所示:

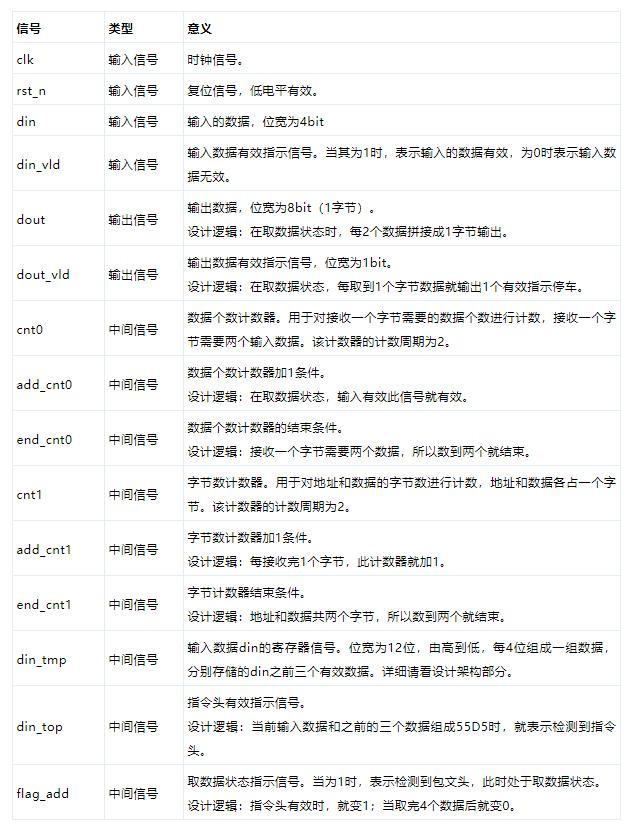

计数器cnt0:数据个数计数器。对接收一个字节需要的数据进行计数,接收一个字节需要2个数据。该计数器的计数周期为2。

计数器cnt1:字节数计数器。对接收的字节数进行计数,地址加上数据共两个字节。该计数器的计数周期为2。

二、信号的意义

三、参考代码

module opcode_dect(

clk ,

rst_n ,

din ,

din_vld ,

dout_vld ,

dout

);

//参数定义

parameter DOUT_W = 8;

parameter DIN_W = 4;

//输入信号定义

input clk ;

input rst_n ;

input[DIN_W-1:0] din ;

input din_vld ;

wire [DIN_W-1:0] din ;

wire din_vld ;

//输出信号定义

output[DOUT_W-1:0] dout ;

output dout_vld;

//输出信号reg定义

reg [DOUT_W-1:0] dout ;

reg dout_vld;

//中间信号定义

reg [2-1:0] cnt0;

wire add_cnt0;

wire end_cnt0;

reg [2-1:0] cnt1;

wire add_cnt1;

wire end_cnt1;

reg [11:0] din_tmp;

wire [15:0] din_top;

reg flag_add ;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt0 <= 0;

end

else if(add_cnt0)begin

if(end_cnt0)

cnt0 <= 0;

else

cnt0 <= cnt0 + 1;

end

end

assign add_cnt0 = flag_add&&din_vld;

assign end_cnt0 = add_cnt0 && cnt0== 2-1;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt1 <= 0;

end

else if(add_cnt1)begin

if(end_cnt1)

cnt1 <= 0;

else

cnt1 <= cnt1 + 1;

end

end

assign add_cnt1 = end_cnt0;

assign end_cnt1 = add_cnt1 && cnt1== 2-1;

assign din_top = {din_tmp[11:0],din}==16'h55d5;

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

flag_add <= 0;

end

else if(din_vld&&flag_add==0&&din_top)begin

flag_add <= 1;

end

else if(end_cnt1)begin

flag_add <= 0;

end

end

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

din_tmp <= 0;

end

else if(din_vld&&flag_add==0)begin

din_tmp <= {din_tmp[7:0],din};

end

end

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

dout <= 0;

end

else if(din_vld)begin

dout <= {dout[3:0],din};

end

end

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

dout_vld <= 1'b0;

end

else if(end_cnt0)begin

dout_vld <= 1'b1;

end

else begin

dout_vld <= 1'b0;

end

end

endmodule

最后

以上就是妩媚冷风最近收集整理的关于at指令解析代码_边缘检测项目:指令检测模块代码解析的全部内容,更多相关at指令解析代码_边缘检测项目内容请搜索靠谱客的其他文章。

发表评论 取消回复