文章目录

- 寄存器

- ARM指令

- MOV

- MVN

- SUB

- ADD

- AND

- ORR

- BIC

- CMP

- TST

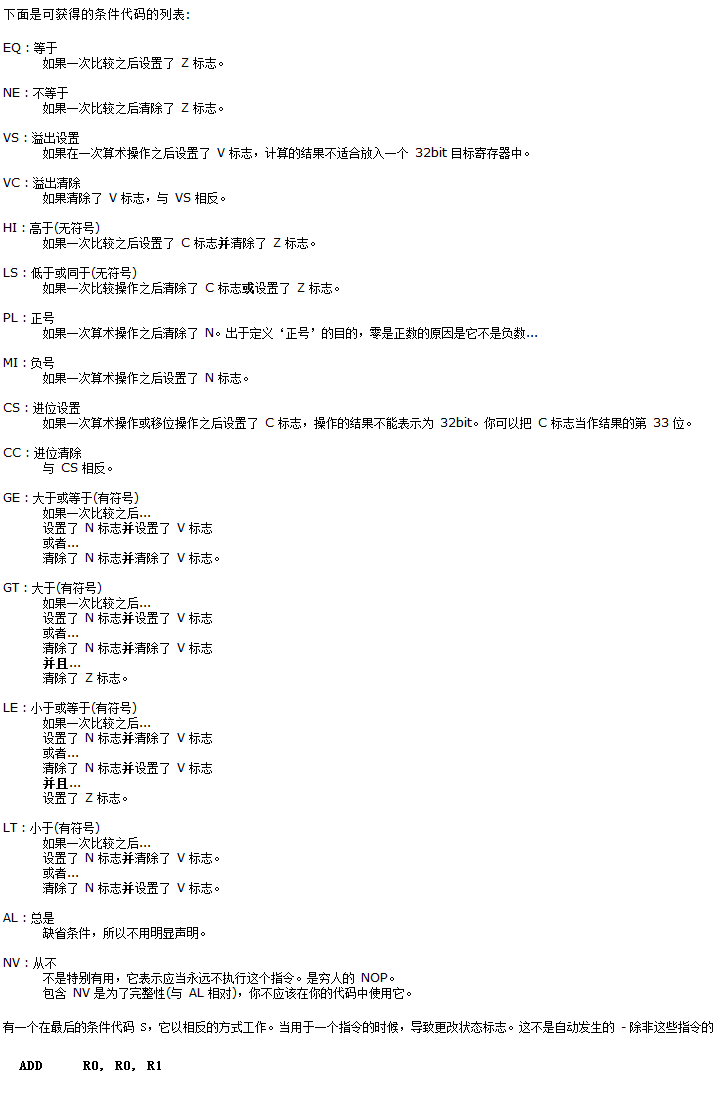

- 条件

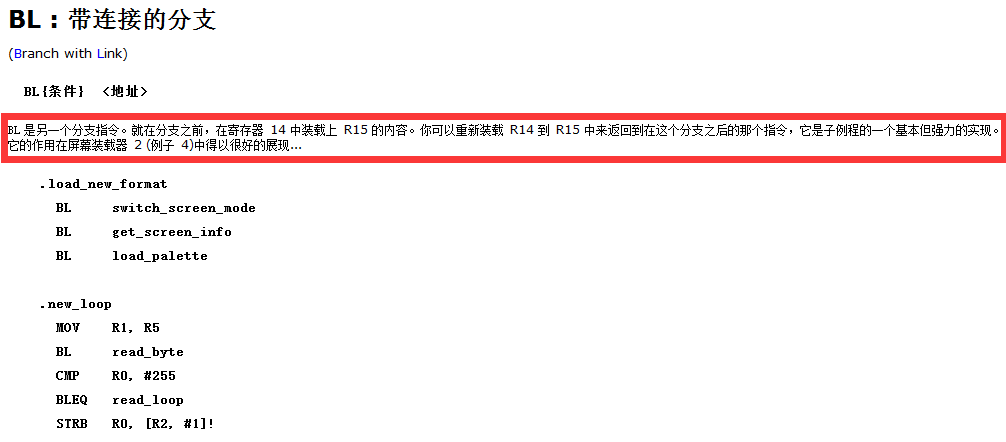

- BL

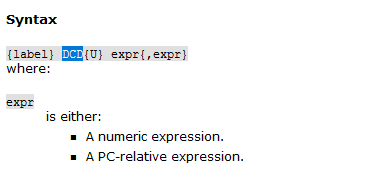

- DCD

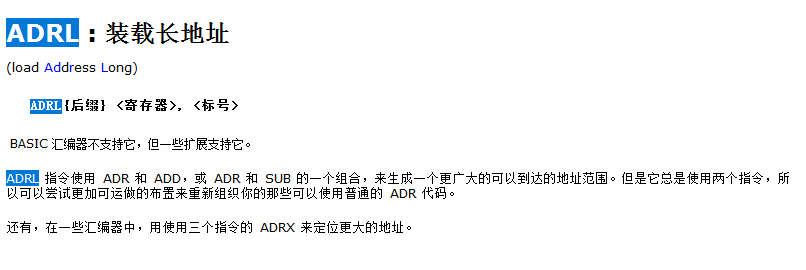

- ADRL

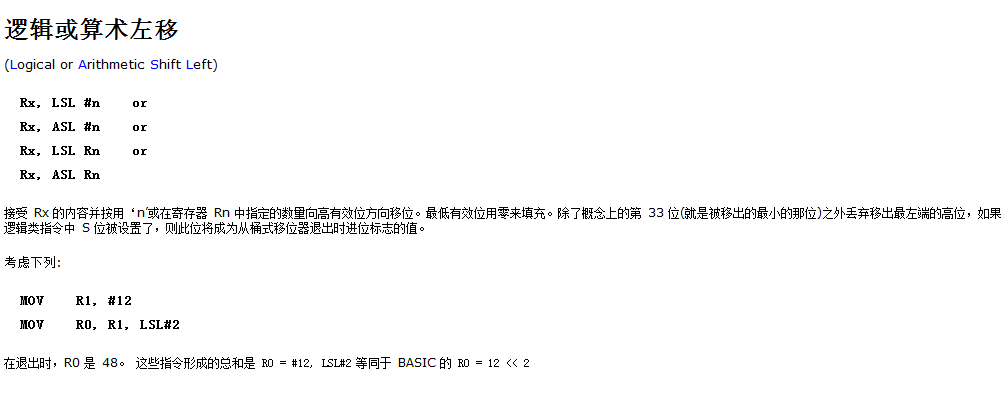

- LSL

- ROR

- MRS MSR

- 寄存器装载和存储

- 伪指令

- 数据伪指令

- 操作类伪指令

- 协处理器访问指令

- 协处理器访问

寄存器

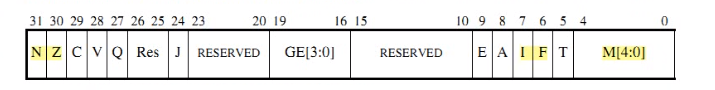

ARM总共有37个寄存器,31个通用寄存器,6个状态寄存器

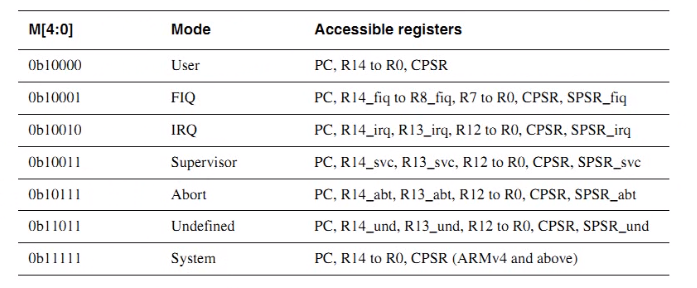

应用程序工作在user模式,内核工作在supervisor svc模式

R13 堆栈指针

R14 LR链接寄存器(函数返回,中断返回)

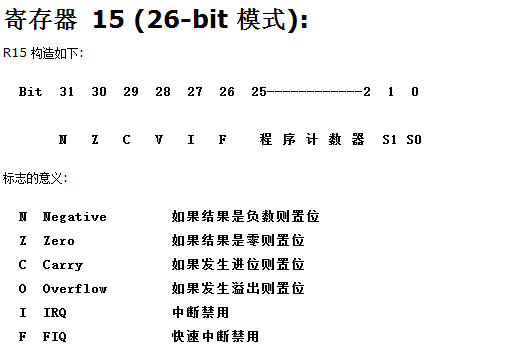

R15 PC指针

SPSR save保存进入中断后的CPSR,中断退出让其值恢复

N:代表negtive

Z:代表zero(相等)

I:代表取消中断

F:代表取消快速中断

M:代表模式

寻址方式

- 立即数寻址

ADD R0, R0, #0x3f; R0<-R0+0x3f - 寄存器寻址

ADD R0, R1, R2; R0<-R1+R2 - 寄存器间接寻址

LDR R0, [R2]; R0<-[R2] - 基址变址寻址(将R1+4的地址里面的 值 给R0)

LDR R0, [R1, #4]; R0<-[R1+4] - 相对寻址

BL NEXTMOV PC, LR跳转链接寄存器

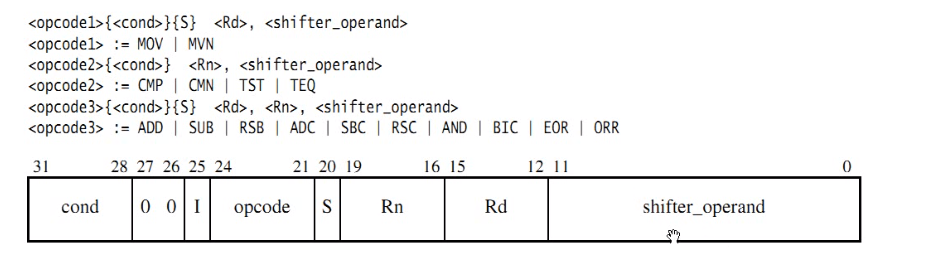

ARM指令

使用@符号来表示注释

{}表示可写可不写的,<>表示一定要写的

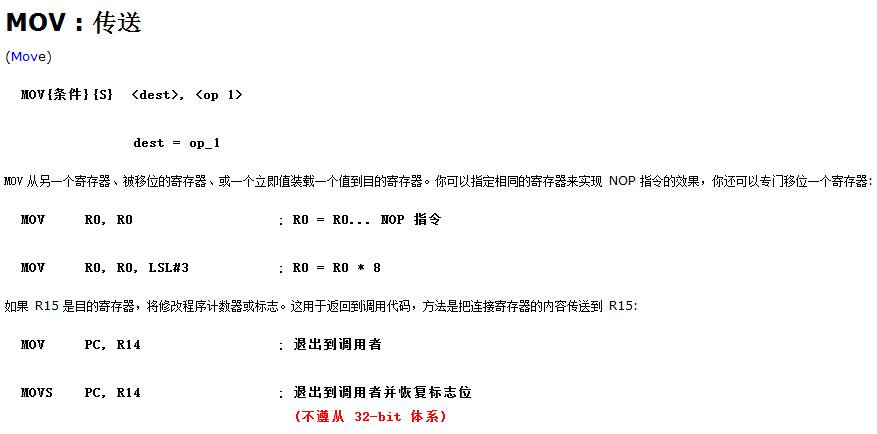

MOV

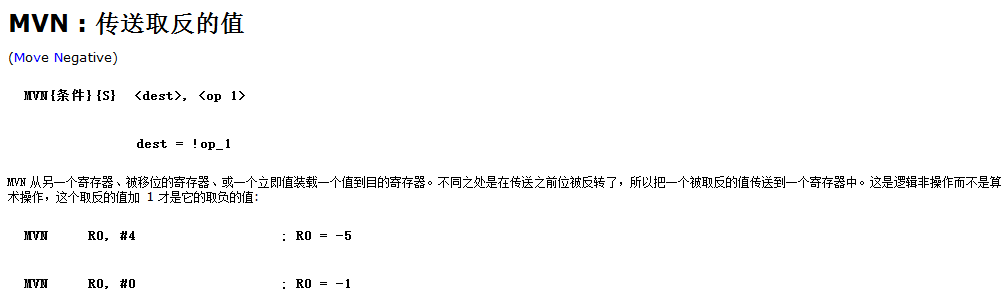

MVN

#4 = 0b0100 取反 符号位1后面为0b1011,因为是负数,因此真正的值为符号位不变,其余位置取反加1,0b0100+0b1 = 0b0101也就是5,算上符号位就是-5.

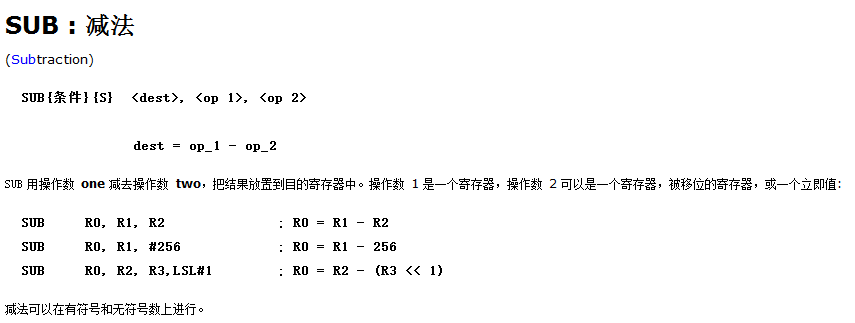

SUB

操作数1必须是寄存器!

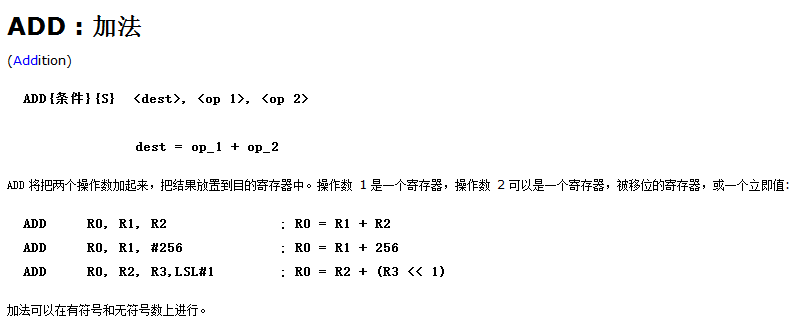

ADD

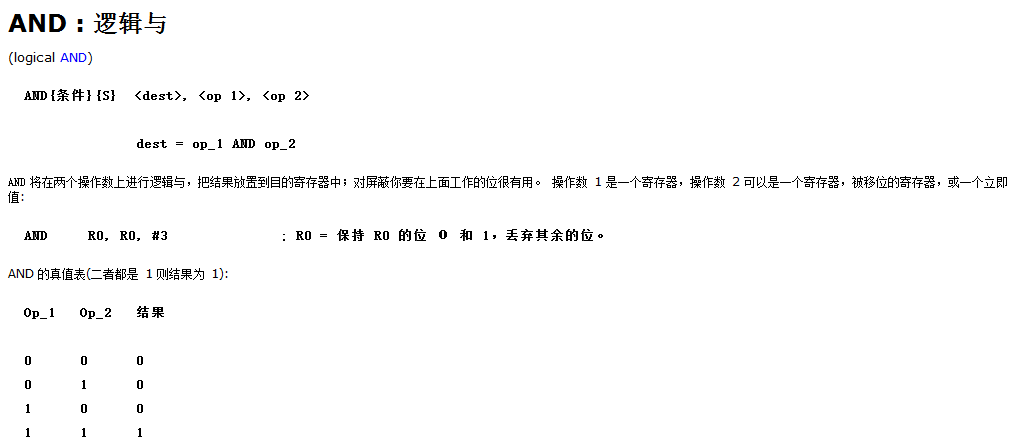

AND

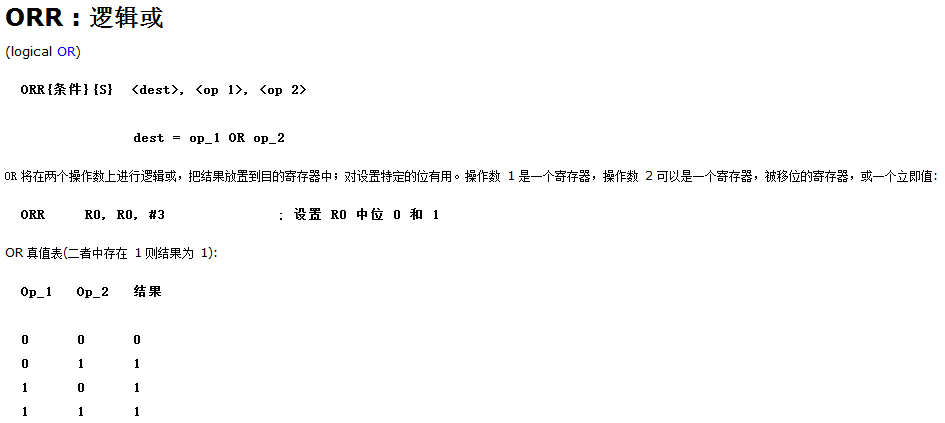

ORR

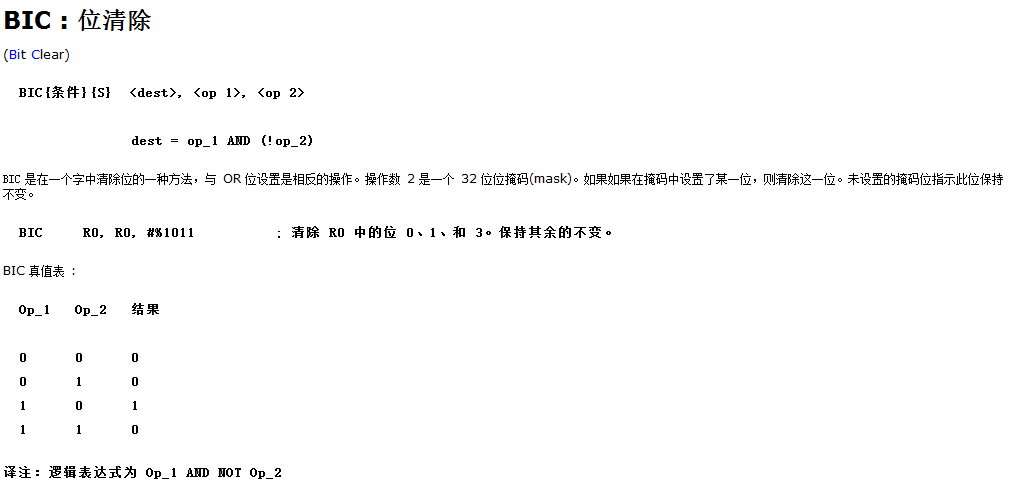

BIC

标准ARM汇编%表示二进制,GNU中使用0b

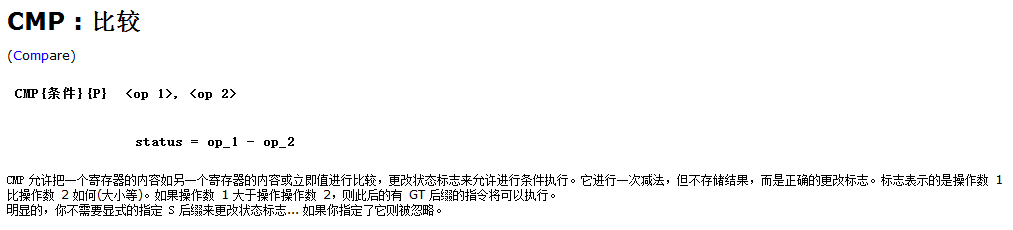

CMP

比较结果在状态寄存器N表示

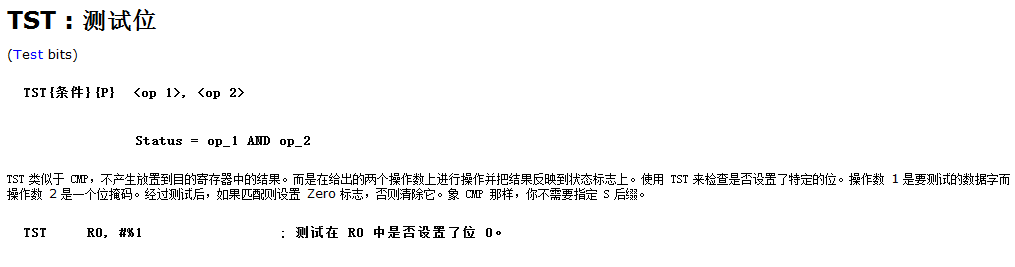

TST

条件

BL

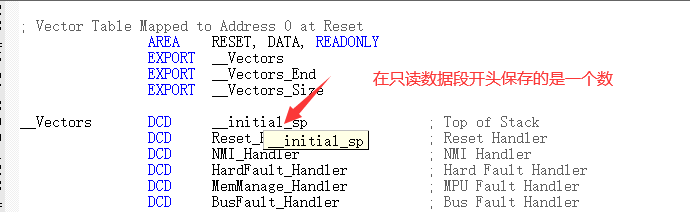

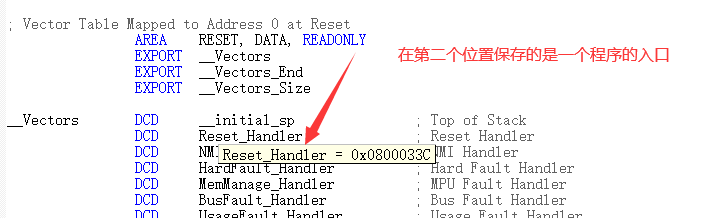

DCD

DCD 指令分配一个或多个字的内存,按4字节边界对齐,并定义内存的初始运行内容。DCDU是相同的,除了其内存对齐是任意的。

比如:

ADRL

LSL

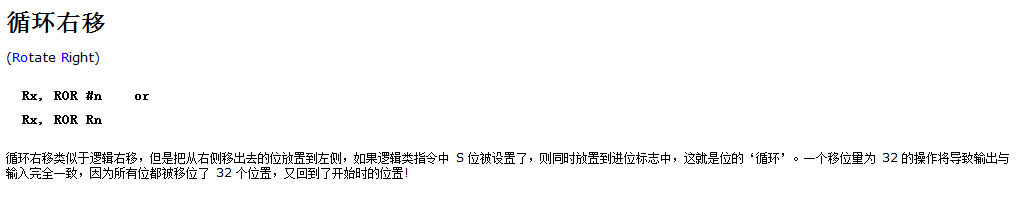

ROR

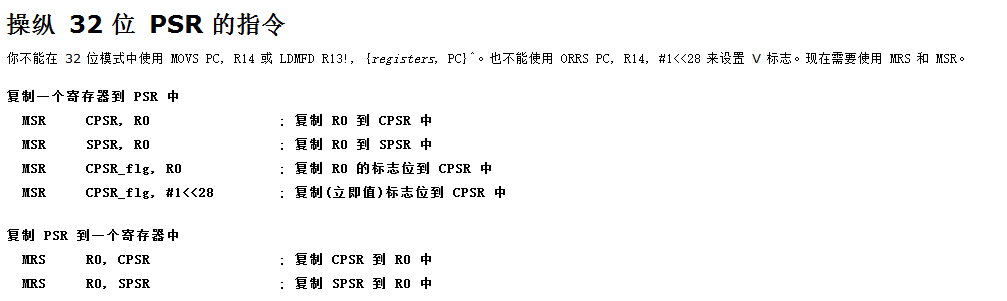

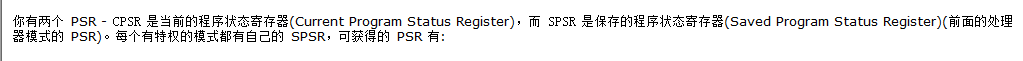

MRS MSR

move register to status register

move status register to register

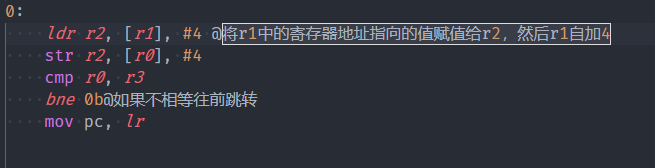

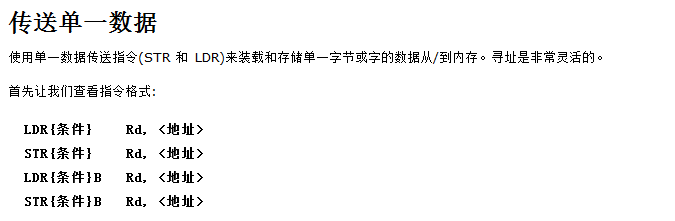

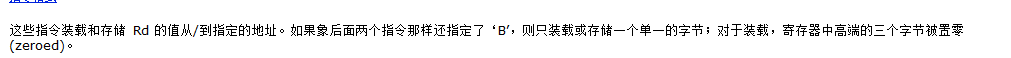

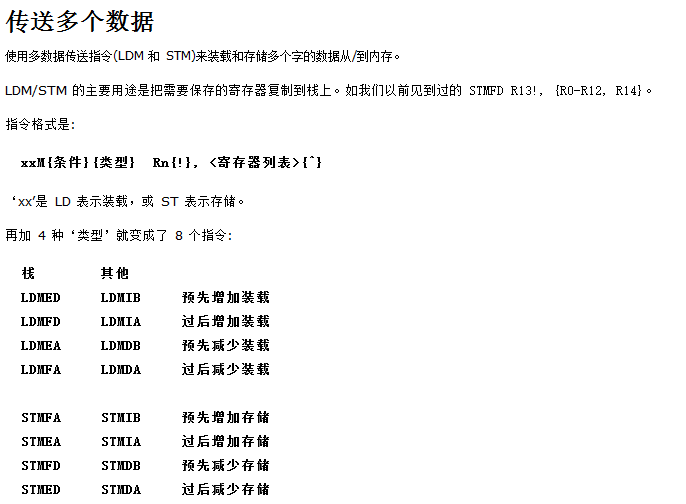

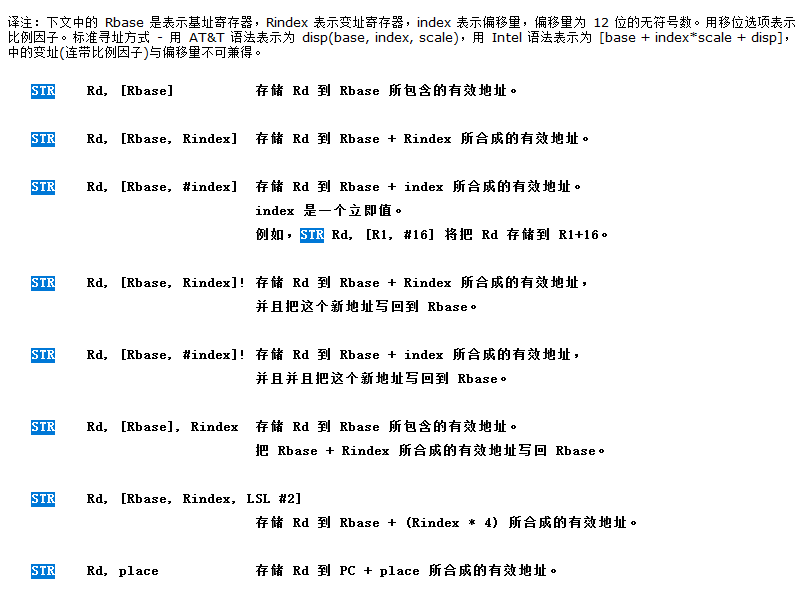

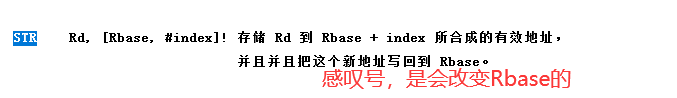

寄存器装载和存储

store register

loader register

伪指令

数据伪指令

伪/指令本身并没有所对应的机器码,它只是在编译的时候起作用,或者转

化为其他的实际指令来运行。

- global(全局符号,后面c语言也可以调用)

- ascii(字符串)

- byte(字节)

- word

- data(数据段)

- equ(宏)

- align(下面的数据对齐)

.data@数据段

hello:

.ascii "helloworld"@定义一个hello数据值为helloworld

.equ DA, 0x89@宏定义

操作类伪指令

mov指令所使用操作数不能超过8位,后面shifter_operand12位不是全部用来装数据,其中还有4位是用来看这个数据是否左移或者右移的!

使用ldr伪指令就可以达到超过8位数据赋值给寄存器,只不过ldr用伪指令的方式立即数要使用=号表示

ldr r0, =0x1ff

nop 是空操作,其实质是mov r0, r0没有意义,消耗时间

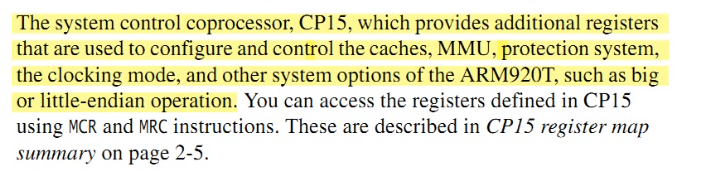

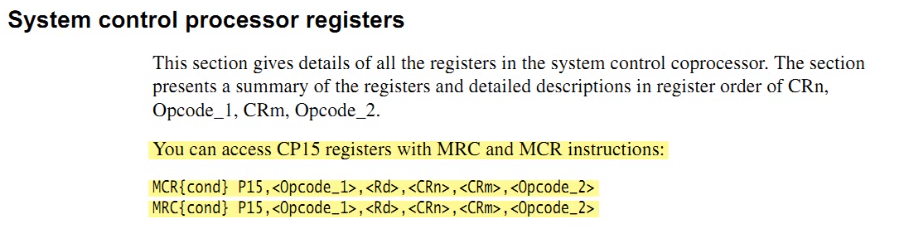

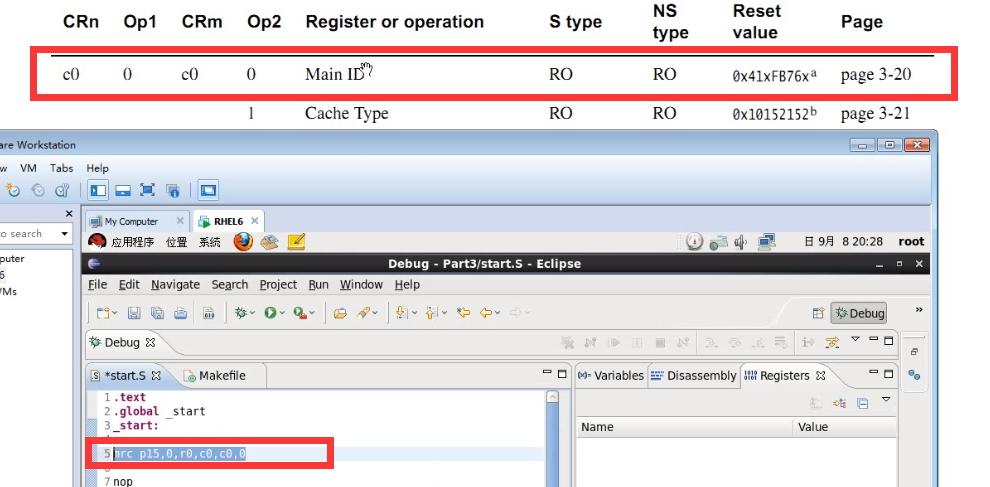

协处理器访问指令

CP15:coproces

提供16组寄存器

协处理器访问

使用mcr, mrc

0x080003D4 E8940007 LDM r4,{r0-r2}

将r4寄存器地址的内容,顺序加载3个到r0,r1,r2中,如果r4后面加!,则加载完后,r4的值会成为r4当前+3个位置。

arm汇编指令之数据块传输(LDM,STM)详见

最后

以上就是沉默超短裙最近收集整理的关于ARM指令寄存器ARM指令ADRL伪指令协处理器访问指令的全部内容,更多相关ARM指令寄存器ARM指令ADRL伪指令协处理器访问指令内容请搜索靠谱客的其他文章。

发表评论 取消回复