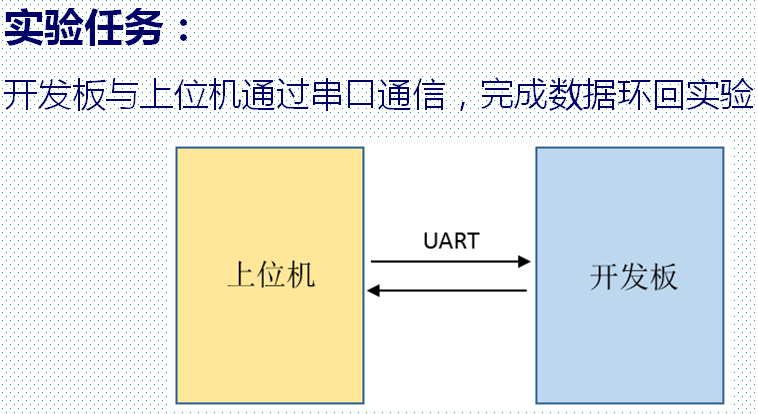

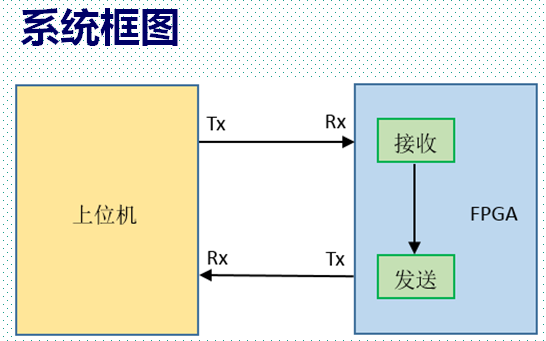

首先,上位机发送数据给FPGA开发板;然后,FPGA开发板收到数据,再回发给上位机。

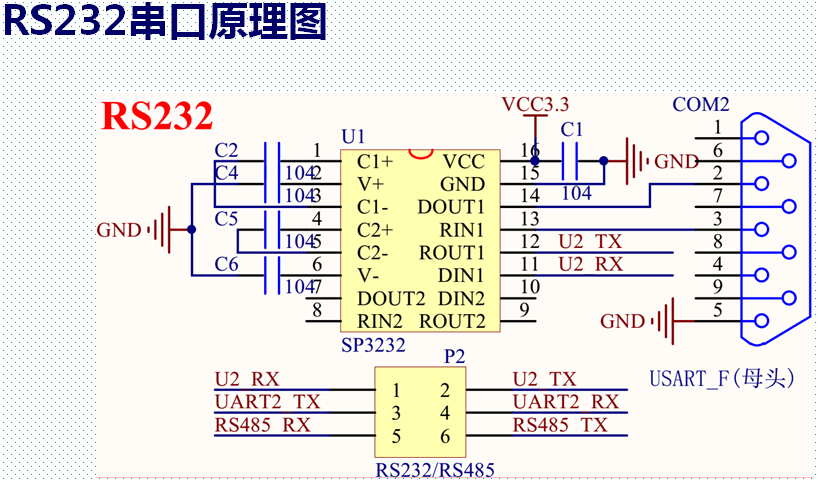

首先,上位机>>RS232通讯_SP3232_TTL通讯>>FPGA

上位机通过串口COM2的发送脚PIN3,发送的RS232信号

>>SP3232的接收脚RIN1,接收信号后(芯片内部电平转换和逻辑转换,把RS232转换成TTL信号)

>>转变成TTL信号后,从ROUT1脚输出

>>FPGA的接收引脚UART2_RX

然后,FPGA>>TTL通讯_SP3232_RS232通讯>>上位机

FPGA的发送引脚UART2_T,发送的TTL信号

>>SP3232的接收脚DIN1(芯片内部电平转换和逻辑转换,把TTL转换成RS232信号)

>>转变成RS232信号后,从DOUT1脚输出

>>通过串口COM2的接收脚PIN2,发送到上位机

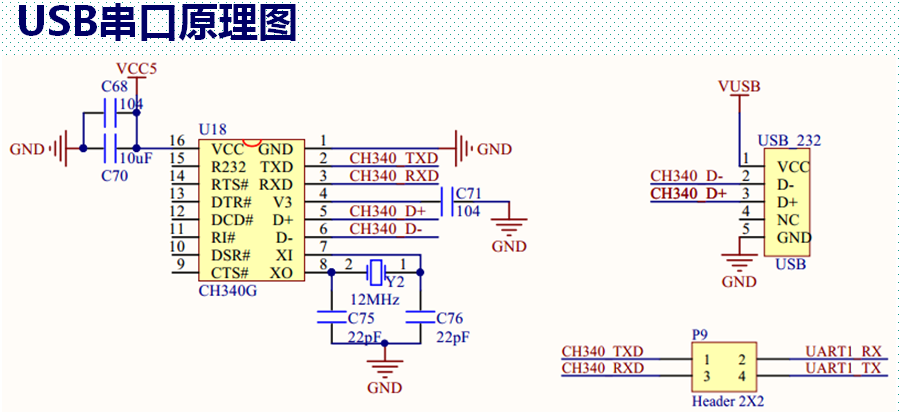

首先,上位机 <<USB通讯>> CH340G

上位机通过USB串口的发送脚D+D-信号

>>CH340G的接收脚D+D-,接收信号后(芯片内部把USB信号转换成TTL信号)

芯片可以实现USB通讯协议和TTL协议的转换.

然后,CH340G <<TTL通讯>> FPGA

CH340G发送脚TXD发送信号>>FPGA接收脚

FPGA发送脚>>CH340G接收脚。

verlog 程序部分

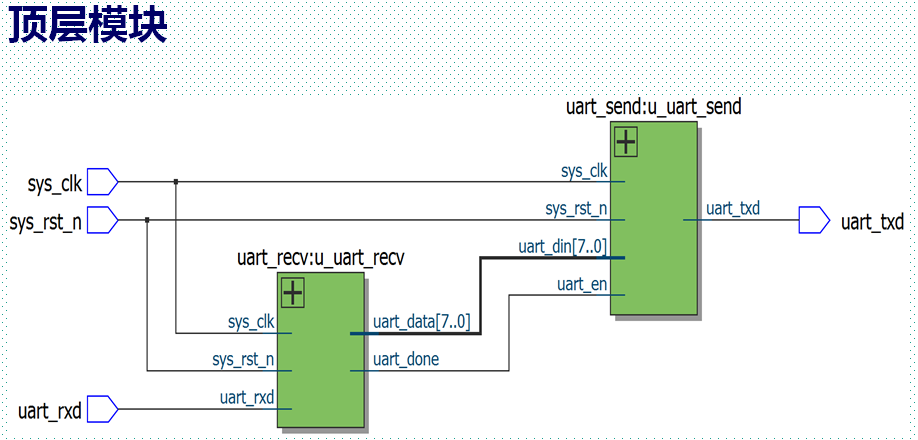

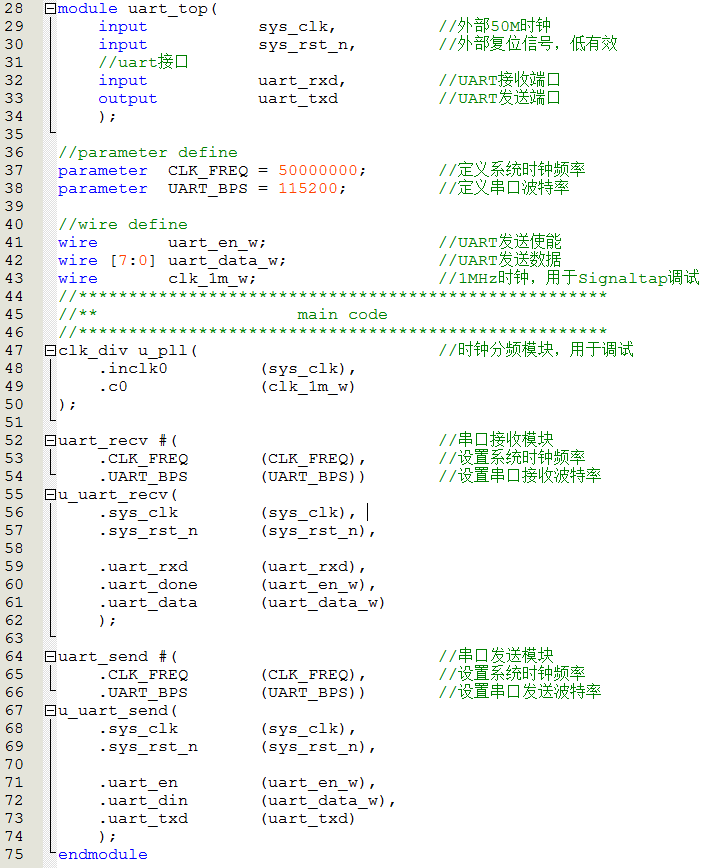

顶层文件

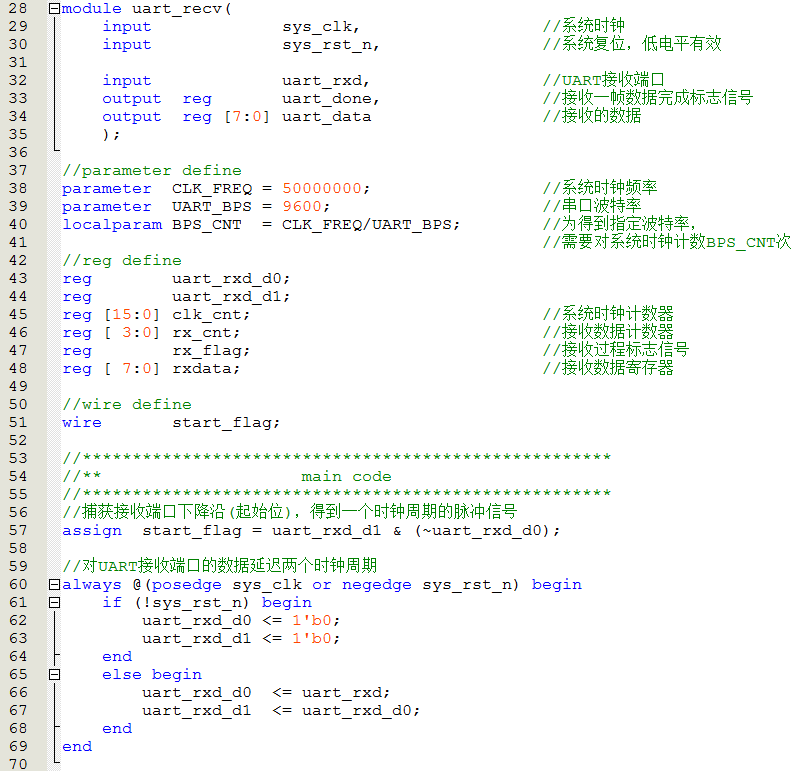

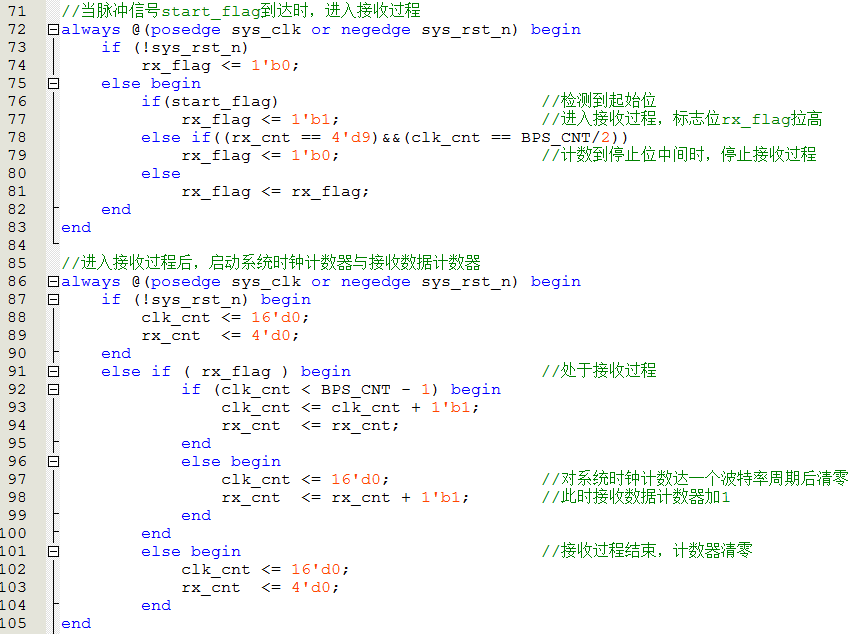

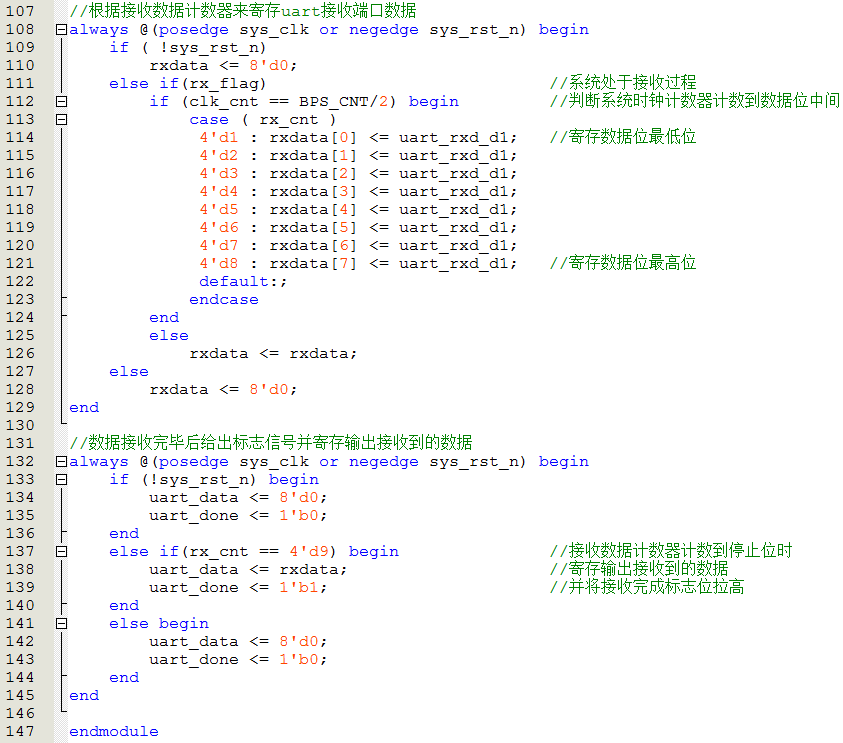

串口接收程序

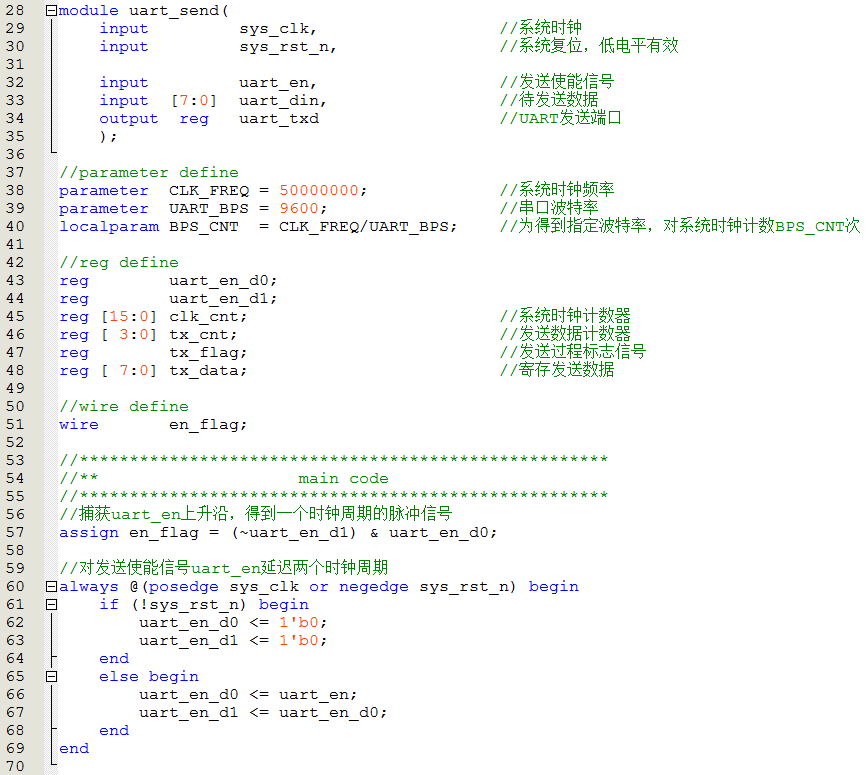

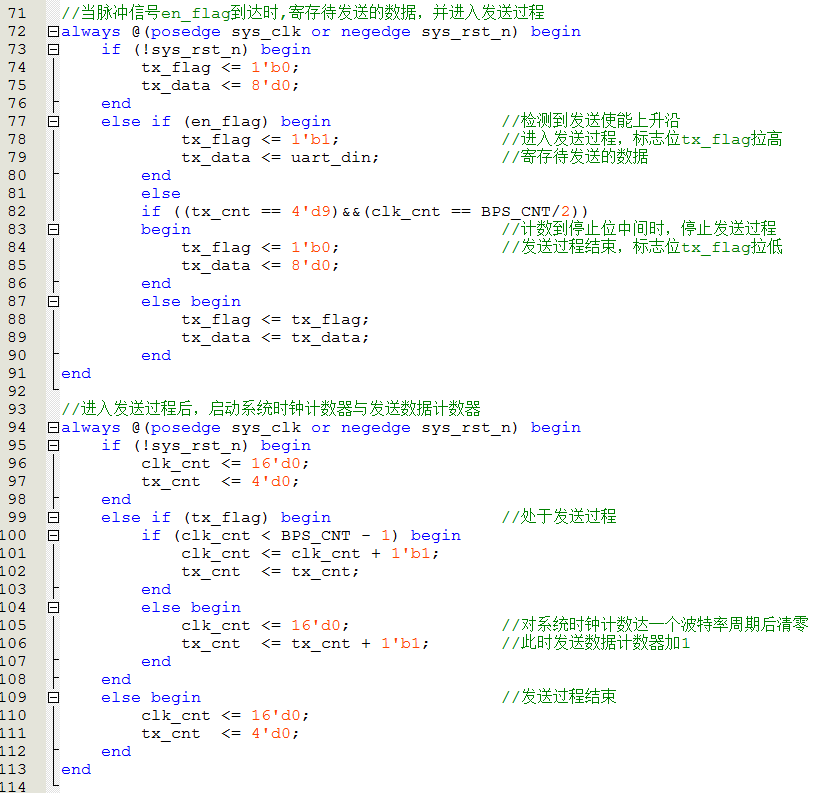

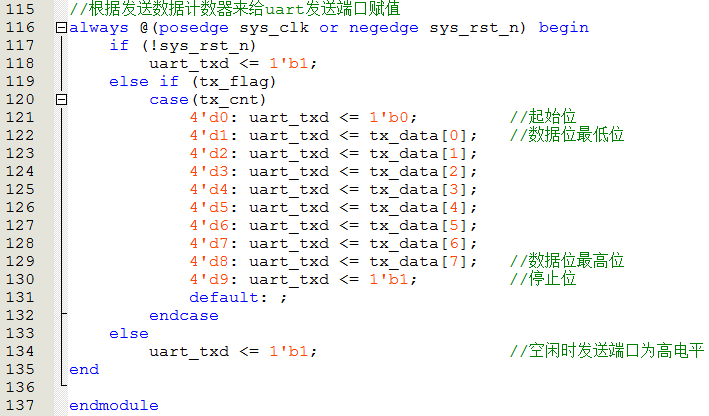

串口发送程序

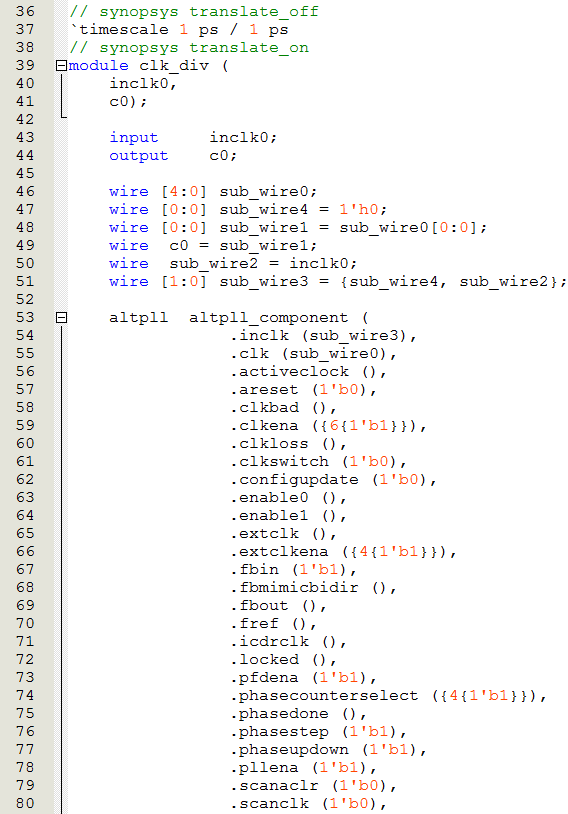

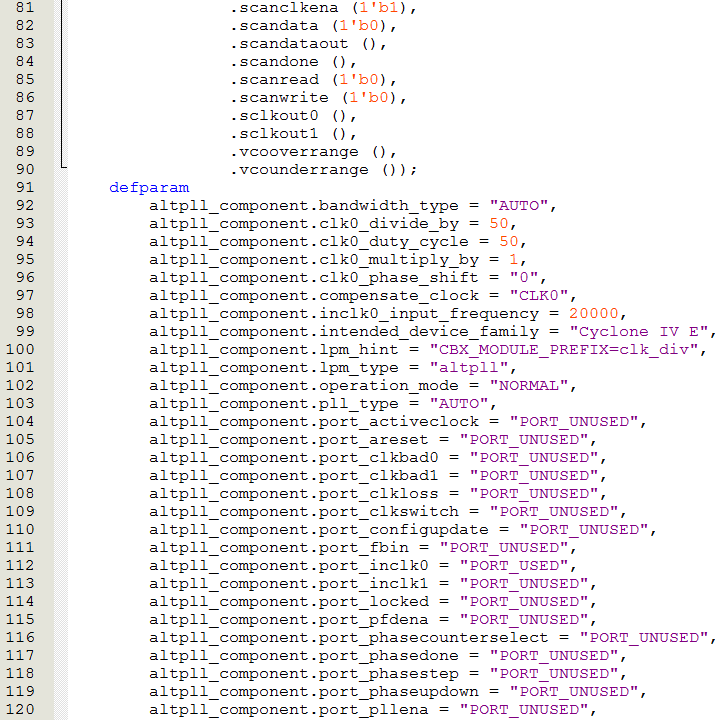

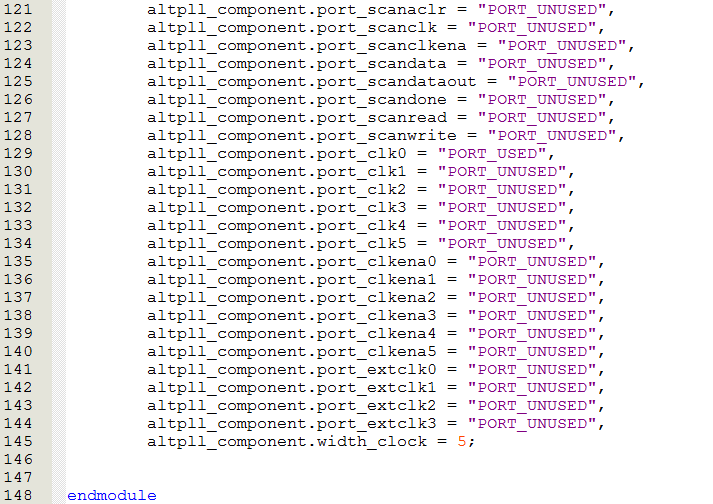

IPcore clk_div

致谢

感谢正点原子,欢迎购买开拓者开发板学习。

淘宝店铺:http://openedv.taobao.com 技术论坛:www.openedv.com

最后

以上就是虚拟棒棒糖最近收集整理的关于上位机和FPGA开发板--串口通信实验verlog 程序部分的全部内容,更多相关上位机和FPGA开发板--串口通信实验verlog内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复