疯雨-版权所有,转载请注明【http://blog.csdn.net/u010346967】

本人菜鸟一枚,有错误的话欢迎指正。

1.什么是上/下拉电阻

上拉就是将不确定的信号通过一个电阻嵌位在高电平,电阻同时起限流作用,下拉同理. 上拉是对器件注入电流,下拉是输出电流,弱强只是上拉电阻的阻值不同,没有什么严格区分。这是网上搜索到的官方说法,那么什么叫不确定信号呢?比如说引脚悬空,如果芯片工作在恶劣的环境下(如有电磁干扰)或者刚上电期间电源供电不稳定,引脚的电平值就会产生波动,这就是不确定信号。

2.上/下拉电阻的由来

那么怎么解决这个引脚电平不确定的问题呢??于是工程师们就想了一个办法,在GPIO端口驱动电路外围加上拉电阻,连到电源,将其限制在高电平状态即为上拉。将上拉电阻接到地端,将电位限制在低电平即为下拉。

3.上/下拉电阻对GPIO口的影响

上(下)拉电阻在有输入的情况下,并不会导致GPIO的输入电压一直为高(低)电平。当输入信号不确定(即悬空时有电磁干扰),才会将GPIO口的电压值拉高(低)。至于为什么是这样?我想隔离的概念应该能很好的解释。

我们来举个列子:

在做压电陶瓷驱动电源的一个项目中,控制芯片选的是STM32f103zet6,通过一个选择开关对其实现内外部控制的转换,外部输入是通过一个信号发生器产生方波,显然当选择开关打到外部控制时,GPIO口与外部信号发生器电路相连,选择内部控制时,拨动选择开关,让GPIO引脚悬空。这时候问题来了,引脚悬空电压能否稳定的一直保持高电平(或低电平)呢???这个问题的根据芯片的工作环境来判断。我的做法是,将GPIO口配置为上(下)拉输入。这样引脚悬空时,电平就能保持稳定高(低)电平。

更多关于拉电阻的信息请参照如下网址:点击打开链接

下面做下补充:

对于常见的ARM处理器,它们的GPIO口基本上可以配置为输入模式、输出模式、开漏或推挽模式。

下面讲讲开漏和推挽模式:

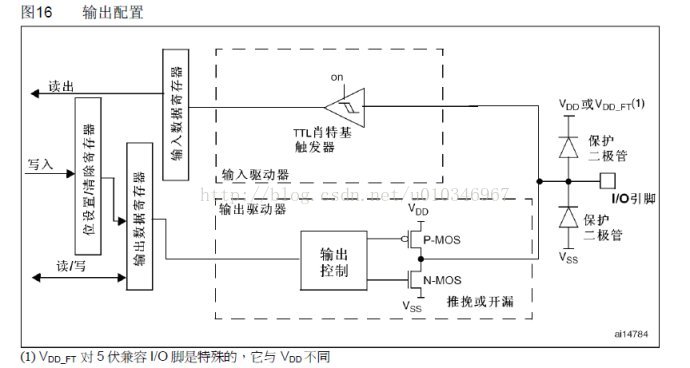

STM32 GPIO电路图如下:

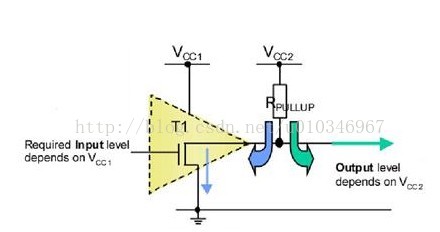

GPIO口配置为输出时:开漏输出不接上拉电阻只能输出低电平。

开漏输出原理图(内部集成了上拉电阻)

常见的GPIO的模式可以配置为open-drain或push-pull,具体实现上,常为通过配置对应的寄存器的某些位来配置为open-drain或是push-pull。当我们通过CPU去设置那些GPIO的配置寄存器的某位(bit)的时候,其GPIO硬件IC内部的实现是,会去打开或关闭对应的top transistor。相应地,如果设置为了open-d模式的话,是需要上拉电阻才能实现,也能够输出高电平的。因此,如果硬件内部(internal)本身包含了对应的上拉电阻的话,此时会去关闭或打开对应的上拉电阻。如果GPIO硬件IC内部没有对应的上拉电阻的话,那么你的硬件电路中,必须自己提供对应的外部(external)的上拉电阻。而push-pull输出的优势是速度快,因为线路(line)是以两种方式驱动的。而带了上拉电阻的线路,即使以最快的速度去提升电压,最快也要一个常量的R×C的时间。其中R是电阻,C是寄生电容(parasitic capacitance),包括了pin脚的电容和板子的电容。但是,push-pull相对的缺点是往往需要消耗更多的电流,即功耗相对大。而open-drain所消耗的电流相对较小,由电阻R所限制,而R不能太小,因为当输出为低电平的时候,需要sink更低的transistor,这意味着更高的功耗。

最后

以上就是优秀母鸡最近收集整理的关于上/下拉电阻对GPIO的影响的全部内容,更多相关上/下拉电阻对GPIO内容请搜索靠谱客的其他文章。

发表评论 取消回复