前言

上篇文章讲了8B/10B编码功能模块,这篇文章讲的是TX Buffer,但是在正式进入主题之前,为了内容的完整性,提一下Tx Gearbox,这是个什么?

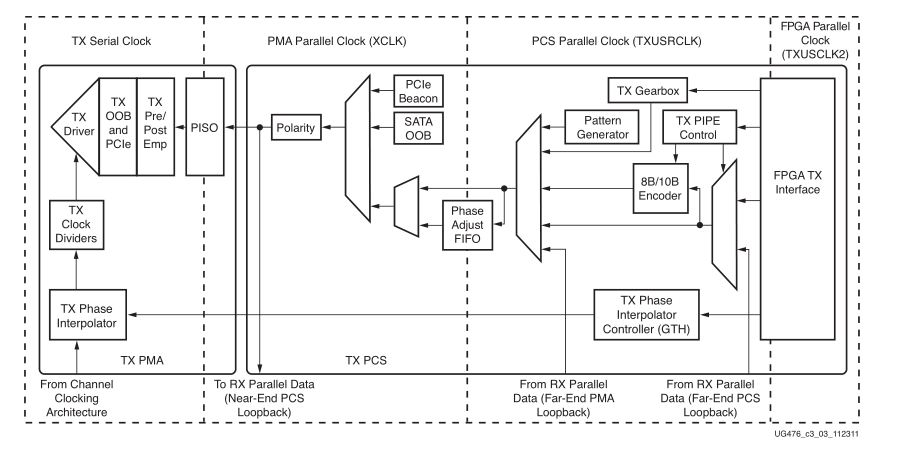

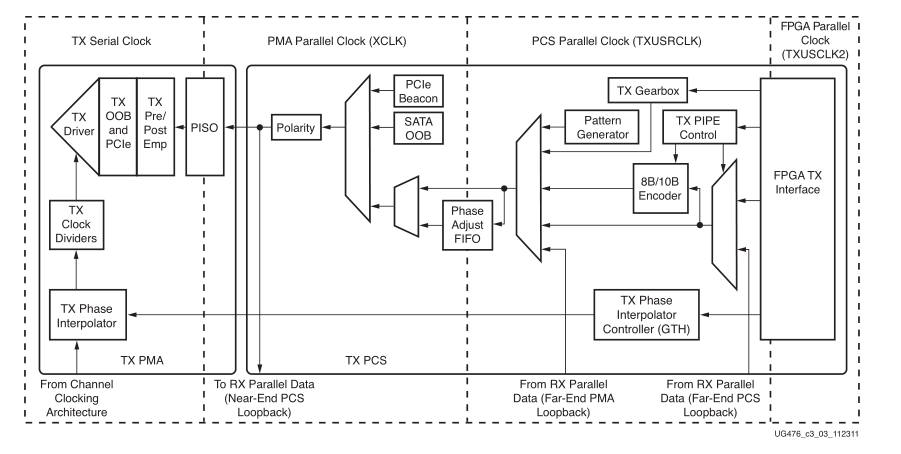

我们看下图:

TX Gearbox和8B/10B Encoder从电路结构上看,地位相同,都是进入一个选择器。

其作用是提供64B/66B编码,一些高速数据率协议使用64B/66B编码,以减少8B/10B编码的开销,同时保留编码方案的好处。

关于其具体的功能,以及使用注意事项,一时半会也弄不清楚,这里暂时就不讲了。深入了解,请看手册。

正文

TX buffer的作用

GTX/GTH收发器的TX数据通路有两个用于PCS的内部并行时钟域:PMA并行时钟域(XCLK)和TXUSRCLK域。为了传输数据,XCLK速率必须与TXUSRCLK速率相匹配,并且必须解决两个域之间的所有相位差。下图显示了XCLK和TXUSRCLK域的情况。

GTX/GTH Transmitter包括一个TX缓冲器和一个TX相位校准电路,以解决XCLK和TXUSRCLK域之间的相位差异。当TX buffer被旁路时,TX相位校正电路(phase alignment)被使用。所有的TX数据路径必须使用TX缓冲器或TX相位对准电路。

TX buffer与TX phase alignment的优缺点

下面给出缓冲区和相位对齐之间的权衡。

- 易用性:

-

在可能的情况下,建议使用TX缓冲器。它很稳定,而且更容易操作。

-

相位对齐是一个高级功能,需要额外的逻辑和对时钟源的额外限制。TXOUTCLKSEL必须选择GTX/GTH收发器参考时钟作为TXOUTCLK的来源,以驱动TXUSRCLK。

- 延迟

-

如果低延迟是关键,必须绕过TX缓冲器。

-

相位对齐在TX数据通路中使用较少的寄存器,以实现较低的和确定的延时。

- TX Lane-to-Lane Deskew

- TX相位对齐电路可用于减少独立的GTX/GTH收发器之间的线路偏移(lane skew)。所有涉及的GTX/GTH收发器必须使用相同的线路速率。

Tx buffer的部分端口与属性

下面介绍一下TX buffer的端口TXBUFSTATUS[1:0]:

TX缓冲区状态。

TXBUFSTATUS[1]: TX缓冲区的溢出或下溢状态。

当TXBUFSTATUS[1]被设置为高电平时,它一直保持高电平,直到TX缓冲器被复位。

1:TX FIFO有溢出或下溢。

0:TX FIFO没有溢出或下溢错误。

TXBUFSTATUS[0]: TX缓冲区的满度。

1:TX FIFO至少满了一半。

0:TX FIFO小于半满。

再介绍两个属性:

TX_XCLK_SEL:

选择用于驱动PMA并行时钟域(XCLK)的时钟源。

TXOUT: 选择TXOUTCLK作为XCLK的来源。在使用TX缓冲器时使用。

TXUSR:选择TXUSRCLK作为XCLK的来源。在绕过TX缓冲器时使用。

TXBUF_RESET_ON_RATE_CHANGE:

GTX/GTH收发器在速率变化时内部产生的TX缓冲器复位。

TRUE: 启用速率变化时的自动TX缓冲区复位。

FALSE: 禁用速率变化时的自动TX缓冲器复位。

TX buffer的复位

每当TXBUFSTATUS表明出现溢出或下溢情况时,就应复位TX缓冲区。可以通过使用 GTTXRESET、TXPCSRESET 或当 TXBUF_RESET_ON_RATE_CHANGE = TRUE 时 GTX/GTH 收发器内部生成的 TX 缓冲器在速率变化时复位。

GTTXRESET的断言会触发一个序列,复位GTX/GTH收发器的整个发射器。

这些设置用于启用TX缓冲器,以解决XCLK和TXUSRCLK域之间的相位差异:

- TXBUF_EN = TRUE

- TX_XCLK_SEL = TXOUT

近期回顾

-

TX的8B/10B编码功能

-

GT Transceiver的动态重配置端口

-

GT Transceiver的回环模式

-

GT Transceiver的电源控制

-

GT Transceiver的复位与初始化(4)RX初始化和复位流程

-

GT Transceiver的复位与初始化(3)TX初始化和复位流程

-

GT Transceiver的复位与初始化(2)CPLL复位以及QPLL复位

-

GT Transceiver的复位与初始化(1)Transceiver复位的两种类型和两种模式

-

GT Transceiver中的重要时钟及其关系(10)RXOUTCLK的来源及其生成

-

GT Transceiver中的重要时钟及其关系(9)RXUSERCLK和RXUSER_CLK2的生成

-

GT Transceiver中的重要时钟及其关系(8)TXOUTCLK的来源及其产生

-

GT Transceiver中的重要时钟及其关系(7)TXUSRCLK以及TXUSRCLK2的产生

-

FPGA 核和FPGA Fabric的区别是什么?

-

GT Transceiver中的重要时钟及其关系(6)TXUSRCLK以及TXUSRCLK2的用途与关系

-

GT Transceiver中的重要时钟及其关系(5)QPLL的工作原理介绍

-

GT Transceiver中的重要时钟及其关系(4)CPLL的工作原理介绍

-

GT Transceiver中的重要时钟及其关系(3)多个外部参考时钟使用模型

-

GT Transceiver中的重要时钟及其关系(2)单个外部参考时钟使用模型

-

GT Transceiver中的重要时钟及其关系(1)GT Transceiver参考时钟

-

FPGA的设计艺术(11)FPGA的构建过程

-

FPGA的设计艺术(8)最佳的FPGA开发实践之严格遵循过程

-

GT Transceiver的总体架构梳理

-

Vivado中用于时钟操作的几个Tcl命令

-

高速串行总线设计基础(六)揭秘SERDES高速面纱之数据包与参考时钟要求

-

高速串行总线设计基础(八)揭秘SERDES高速面纱之CML电平标准与预加重技术

-

FPGA基础知识极简教程(1)从布尔代数到触发器

-

FPGA基础知识极简教程(7)详解亚稳态与跨时钟域传输

-

静态时序分析中的四类时序路径

-

时序分析中的关键术语

-

高速串行总线设计基础(一)同步时序模型介绍

-

高速串行总线设计基础(四)眼图的形成原理

-

FPGA设计心得(10)关于行为仿真的一点观点

-

Vivado如何计算关键路径的保持时间裕量?

-

Vivado如何计算关键路径的建立时间裕量?(实践篇)

-

Vivado如何计算关键路径的建立时间裕量?(理论分析篇)

-

TCL中Ports/Pins/Nets/Cells/Clocks之间的交互关系?

-

TCL中关于Nets的一些用法?

-

TCL中关于Cells的一些使用方法?

-

TCL中关于Pins的一些使用方法?

-

TCL中关于管脚(Ports)的一些使用方法?

-

逻辑设计中复位的稳妥处理方法?

-

逻辑设计中需要显式地使用IBUF以及OBUF类似的原语吗?

-

FPGA的设计艺术(1)FPGA的硬件架构

最后

以上就是英俊冰棍最近收集整理的关于GT Transceiver的TX Buffer功能块的全部内容,更多相关GT内容请搜索靠谱客的其他文章。

发表评论 取消回复