滤波器原理:滤波器就是对特定的频率或者特定频率以外的频率进行消除的电路,被广泛用于通信系统和信号处理系统中。从功能角度,数字滤波器对输入离散信号的数字代码进行运算处理,以达到滤除频带外信号的目的。

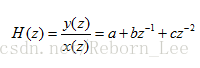

有限冲激响应(FIR)滤波器就是一种常用的数字滤波器,采用对已输入样值的加权和来形成它的输出。其系统函数为:

其中 表示延时一个时钟周期,

表示延时一个时钟周期, 表示延时两个周期。

表示延时两个周期。

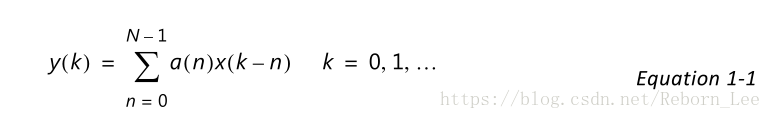

传统的单速率 FIR 版本的核(IP核)的生成通过计算如下的卷积和公式:

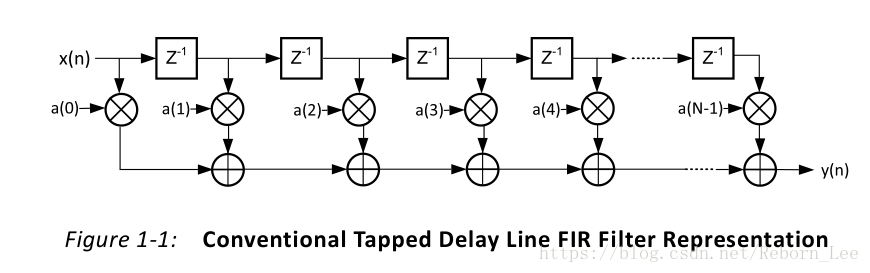

与之对应的传统抽头延迟线 FIR滤波器实现如下:

上式表达的是一个N-1阶的FIR滤波器,它有N个抽头(系数)。因此有N个乘法器,N-1个累加器组成。

虽然上图以及上式对于概念的理解一目了然,也很有用,但实际上FPGA并不是这么实现的。

那么实际上FPGA是怎么实现的呢?

FPGA中的FIR滤波器由IP核来生成,下篇博文将介绍IP核使用哪些架构来实现所需的滤波器。

下篇博文地址:【 FPGA 】FIR 滤波器的结构

下面部分是摘自电子发烧友上的文章的一部分,仅供参考:

有两种基本类型的数字滤波器:有限脉冲响应( FIR )和无限脉冲响应( IIR)。

IIR滤波器使用反馈,而且往往是模仿传统的模拟滤波器的响应。反馈的用途意味着他们的脉冲响应是递归的,并延伸到无限的时段。虽然可以用比FIR滤波器更少的计算来实施IIR滤波器,IIR滤波器可能有稳定性的问题,他们可能与用FIR滤波器完成的性能不匹配。

相比之下, FIR滤波器没有反馈,这意味着它的脉冲响应在一个有限的时间范围之内。 FIR滤波器拥有优于IIR滤波器的几个优点,其中包括一个事实,即在整个频谱范围,他们有完全恒定的群时延,在所有频率范围内,不论滤波器的大小,他们是完全稳定的。

通用FIR滤波器的图形表示如图10所示。在这种情况下,输入样本xn通过一系列的缓冲寄存器(这些都标记为z-1,对应延时单元的Z变换)。

图10 经典FIR滤波器的通用表示

滤波器的工作原理是用一系列的常数(称为抽头系数)乘以一系列最新的n个数据采样,并对所得到的数组的单元进行求和。通过改变系数和滤波器抽头数目的加权(值),FIR滤波器实际上可实现几乎任何所需的频率响应特性。

问题是FIR滤波器可能需要大量的抽头(有时数百个),以实现其预定的目标。每一个抽头需要消耗逻辑资源的乘法器累加器( Mac )单元。另外在每个时钟,每个抽头执行消耗功率2的乘法和加操作。

http://www.elecfans.com/tongxin/rf/20171212600987.html

最后

以上就是有魅力墨镜最近收集整理的关于【 FPGA 】FIR滤波器开篇之传统抽头延迟线FIR滤波器实现介绍的全部内容,更多相关【内容请搜索靠谱客的其他文章。

发表评论 取消回复