目录

概述

背景

为什么需要低功耗设计

CMOS IC功耗分析

基本概念

功耗的分类

功耗相关构成

不同层次低功耗设计方法

芯片中的功耗分布以及对应的低功耗方案

低功耗方案

系统算法级的低功耗技术

编码阶段的低功耗技术

门控时钟 Clock Gating

物理实施的低功耗技术

操作数分离(Operand Isolate)

门级电路的功耗优化(Gate Level Power Optimization,简称GLPO)

多电压供电

电源门控(Power Gating)

其他

概述

背景

低功耗设计是IC设计基础能力的组成部分,也是IC设计能力地图中重要的一部分。

对于深亚微米(DSM,deep sub-micron)芯片,例如:0.35um,0.25um,0.18um的物理实施与纳米级(nm,nanometer)的设计中≤130nm,需要在物理实施中考虑的更多,也更复杂。同时互连线延时也会随着工艺的更加先进更加严重。现代电子的发展趋势是:半导体的几何尺寸越来越小、供电电压越来越低、单元的阈值电压越来越小、电路规模越来越大,功耗密度越来越高,漏电流越来越大,在90nm或一下的工艺,静态功耗占整个设计功耗的20%以上。因此对于静态功耗也需要有足够的重视,进行相关的优化与设计。

本文首先分析需要低功耗设计的原因,进一步的,对基本的概念进行介绍以及功耗分析的相关概述。进而针对功耗的问题,在多个layer给出对应的低功耗技术及其优缺点。个人学习总结,水平有限,有问题欢迎指出~

为什么需要低功耗设计

- 便携设备的要求 便携设备电池容量有限,低功耗是决定长时间待机的关键

- 可靠性的要求 功耗越大,芯片的有源区温度越高,芯片失效率越高 ,寿命越低

- 芯片性能持续发展的要求 2004年后,功耗超过100W,能耗密度过大加上散热成本过高导致芯片温度超过能忍受的限度,时钟频率无法再提升(饱和值3~4GHz)

- 节约能源的需求 例:世界范围内的4亿台个人电脑(2000年数据),每年消耗0.16T kW/h(1011度电)的电能,与26个核电站的发电能力相当

CMOS IC功耗分析

基本概念

能耗:执行特定任务所消耗的能量,单位J

功耗:单位时间的能耗,单位W

功耗密度:单位面积或单位体积消耗的功率,单位W/CM²,W/CM³

吞吐率:or 吞吐量,单位时间执行的操作次数、指令个数或者运算次数

MOPS(Million Operation Per Second):每秒执行多少百万次操作

MIPS(Million Instruction Per Second):每秒执行多少百万次指令

GFLOPS(Giga Float-Point Operation Per Second):每秒执行多少个10亿次浮点运算

功耗效率

消耗单位功率能达到的吞吐率

有MIPS/mW、 GFLOPS/W等

功耗的分类

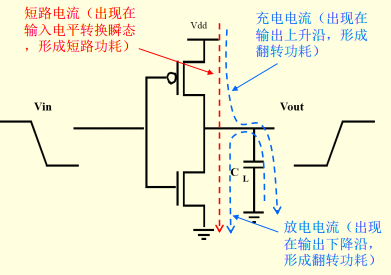

除此之外,一般使用反相器来对功耗相关的概念进行介绍,反相器的电路图如下所示:

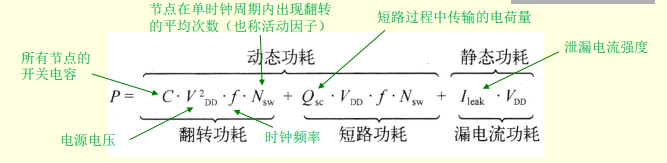

从动静态来分,可以分为动态功耗与静态功耗,其中动态功耗又分为翻转功耗与短路功耗,其中时钟频率,电源电压对翻转功耗有着较大的影响,静态功耗指得是漏电流功耗。动态功耗是在电路条件下的功耗,静态功耗是即使电路状态不改变也会产生的功耗~翻转功耗是实现电路功能必须的,称为有效功耗,短路功耗与静态功耗不是实现电路功能所必须的,称为无效功耗。这里单独开一个小节CMOS IC功耗类型及其影响因素,详细的分析这些功耗的影响因素。这里只是大致定性的有所了解。小节中将会更进一步的解释,同时结合单元库,对一个反相器进行功耗的计算,不在这里展开。

功耗相关构成

本节提供一些顶层的数据,对于功耗在各个层次的相关数据进行展示

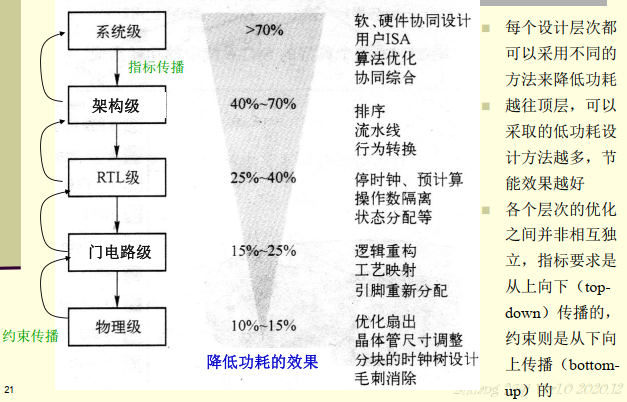

不同层次低功耗设计方法

苹果就是软件+硬件共同实现自己的产品,因此在很多方面做的很优秀~同时我们需要在架构设计的时候就将低功耗方案作为一个设计标准,不能仅仅在编码层次进行功耗的优化。该图来自庄老师PPT

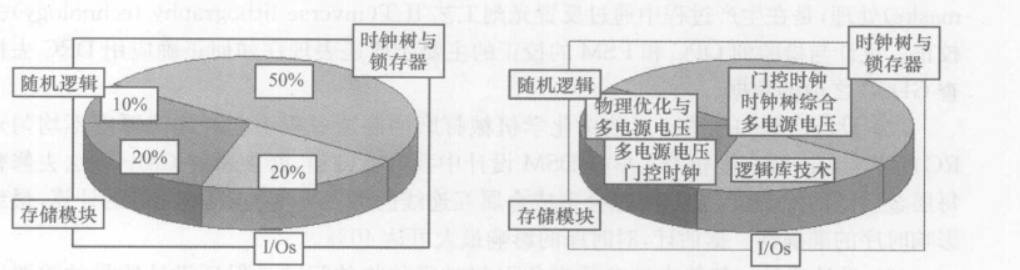

芯片中的功耗分布以及对应的低功耗方案

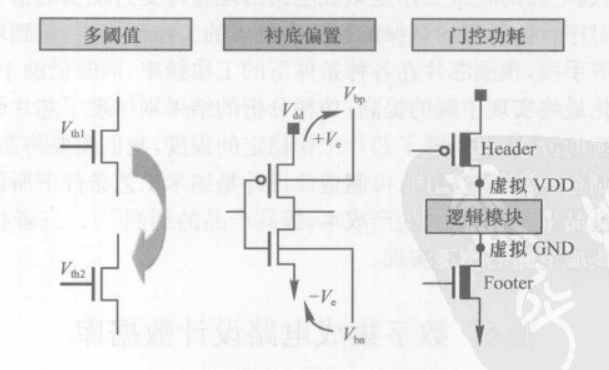

一般时钟树与latch占50%,因此在不需要高频的时候降频,加时钟门控思路是很重要的。I/O占用20%,标准单元占10%,存储模块占用20%。根据设计实验,采用多电源电压的方法可以使得功耗减少30%,门控电路方法可以使得功耗减少50%,衬底电压偏置方式功耗可以减少70%。当然,想来也是一个common部分,不是绝对的,只是一个参考~

该节对应的图片来自《数字集成电路物理设计》

低功耗方案

我们前面了解了功耗的来源,组成,及其计算方式,下面将介绍一些各个阶段的低功耗方案

功耗设计决策方案有

系统设计-编码与算法

设计架构-多电源电压,睡眠模式

设计实施阶段有

RTL门控时钟,多域值,微架构(RTL编码阶段),综合布局布线(物理实现阶段)

那么据此,我们作为前端设计,重点应该学习了解的是编码阶段以及物理实现阶段可以做的优化,在更高层的方案需要结合项目需求,不太具有总领性质的内容,不在这里进行总结。后续有合适的demo在这里补充上例子,同时这里需要考虑是否结合工具的使用,若是有需要,将单独开一篇,这里不进行强制要求。同时没有什么是没有代价的,低功耗方案也是,必定会引入时序或者是面积上的问题,需要根据需求进行取舍。

系统算法级的低功耗技术

系统算法级别的解决方案为系统分割,内存组织管理,电源管理,电压频率选择,算法评估,算法转换。这些可能看起来比较笼统,但是确实在设计中是很重要且相对来说比较困难的部分。需要经验丰富,能力全面的工程师来做。同时这些将决定后面步骤的实现。个人理解这里是对每一个功能的解耦,将不同的功能单独分割开,方便后续的实现。

编码阶段的低功耗技术

本节主要介绍编码阶段的低功耗技术:门控时钟(Clock Gating工具自动加,但是要注意编码风格)

门控时钟 Clock Gating

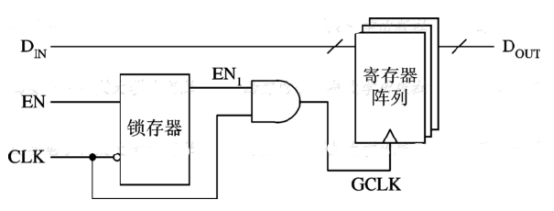

- 基本概述与物理实现

时钟门控可以说是编码阶段,作为数字前端人员可以进行优化的,这是一种有效的降低动态功耗的手段,门控时钟电路可以有效的节省20%-60%的功耗。那么什么是时钟门控技术呢?简单来解释:就是使用一个门将时钟给控制住,让其不进行翻转。我们知道时钟是一个设计中翻转最频繁的信号,前面介绍时钟相关的功耗占整个芯片功耗组成的50%。同时触发器都是使用边沿触发的,在当这个触发器不需要使用时钟的时候,可以将该触发器的时钟关掉,就可以节省其动态功耗,从而减少不必要时钟跳变产生的功耗。这就是门控时钟的工作逻辑。

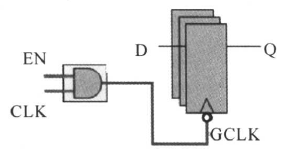

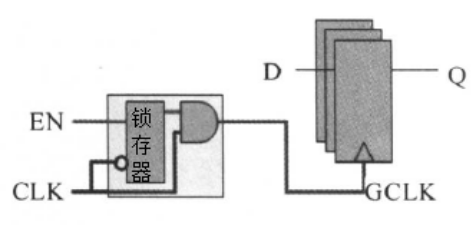

下面是一个简单的门控时钟

当EN为0时,GCLK始终没有沿触发,Q端保持输出。但是这样处理EN可能会带来以下问题:当EN信号到来可能会引起时钟毛刺!显然这是一种为危险的行为,根本原因是不受控制的EN引起的。因此只需要将EN进行控制就可以得到一个没有毛刺的时钟了。

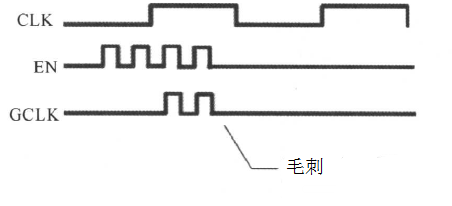

我们引入了锁存器来帮助EN稳定。D锁存器,又称透明锁存器,的功能表如下所示:

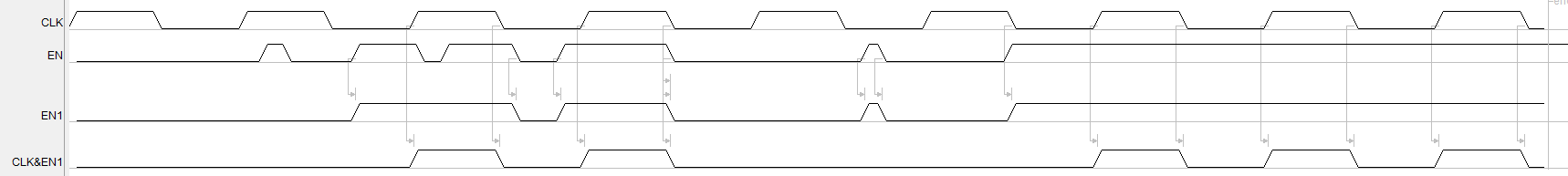

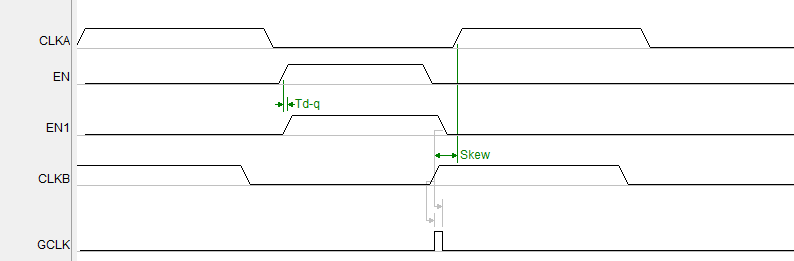

在E为0的时候,保持,E为1的时候跟随D端的输入。优化后的功能实现的电路及其时序图如下所示。需要注意,锁存器的E端接时钟,由于有一个取反,因此低有效,D端接EN,可以将其毛刺滤去。因此在CLK为低的时候,为跟随逻辑。当CLK为高电平时候,为保持逻辑。输出的EN就会是一个受控制的EN信号。

根据波形可以看到,EN1的毛刺,仅仅在CLK低电平期间会有,输出的时钟通过与门,就会将其滤去,在CLK高电平期间,为保持逻辑,不会有毛刺的产生。

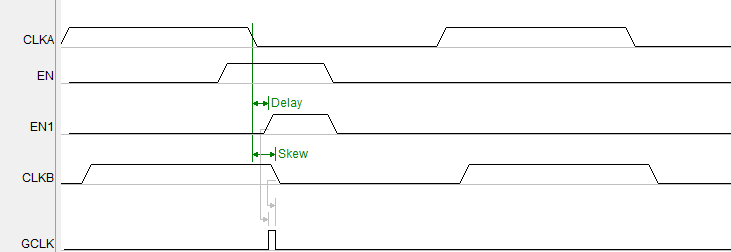

不过需要注意的是,如果在电路中,锁存器与与门相隔很远,到达锁存器的时钟与到达与门的时钟有较大的延迟差别,则仍会出现毛刺,同样是这个电路,时钟在latch的E端与与门的输入端的skew时钟偏移较大,并且大于latch的D-Q的delay的时候,就会出现毛刺。

上边的例子是CLKB相对于CLKA有延时,那么当CLKB较早与CLKA到来的时候呢?就会有如下的问题,当Td-q的延时>Skew的时候,还是会有毛刺产生。

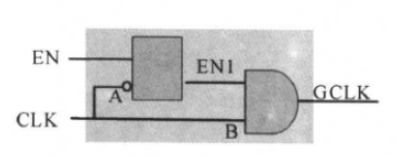

仅通过与门进行时钟门控不足以满足所有设计要求。仅仅加入一个锁存器也是有可能带来时钟毛刺的,这是由于CLKA与CLKB需要满足一定的时序关系,这个时候ICG Integrated Clock Gating Cell 的引入非常引人注目,它轻松解决了传统方法的问题。如下图所示:将锁存器与与门作为一个单元,就可以解决上述的毛刺。

我们在使用中可以直接使用ICG,而不需要自己搭建门控时钟,ICG门控单元是对Skew作了控制,不存在前面描述的毛刺问题。

同时我们了解到,停时钟就会使得Q的输出保持为Q本身,因此这也是我们使用门控时钟的条件。

- 编码技巧

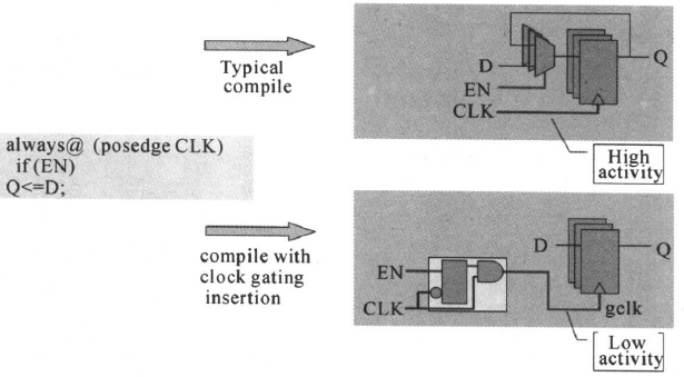

根据前面的使用门控时钟的条件可得知,保持逻辑是我们综合出来ICG的必须条件。如下图所示

因此在代码中多写保持逻辑,就可以优化功耗,同时需要看gating的插入率,过低的插入率并不能有效的降低功耗,尽可能使得gating的插入率在80%以上

- 物理实现

在综合时候使用特定的综合指令,即可指导综合工具帮我们集成ICG。门控时钟的实现主要有两步,一步是设置门控时钟的风格,通过命令set_clock_gating_stale 及其选项来实现;另一步就是在网表中加入门控时钟,通过命令insert_clock_gating来实现

-sequential_cell 选项设置是否采用基于锁存器的风格。

基于锁存器的离散门控单元是默认值,可以通过下面的命令来设置:set_clock_gating_style -sequential_cell latch

不使用锁存器的门控单元,可以通过下面的命令来设置:set_clock_gating_style -sequential_cell none

使用集成的门控单元则不需要使用这个-sequential_cell来设置了,因为-sequential_cell 选项设置是否采用基于锁存器的风格。使用集成的门控单元直接设置参数就可以:set_clock_gating_style “integrated”(推荐)

-positive_edg_logic选项(简写为-positive或-pos)设置在RTL代码中用上升沿锁存的寄存器(也就是上升沿沿触发的寄存器)采用何种门控逻辑

-negative_edg_logic选项(简写为-negative或-neg)设置在RTL代码中用下降沿锁存的寄存器(也就是下降沿触发的寄存器)采用何种门控逻辑。

举例:

set_clock_gating_style -sequential_cell none -pos “or”

该命令设置了不适用锁存器的风格,然后对于上升沿触发的寄存器,其门控单元使用或门逻辑构成。

set_clock_gating_style -positive “integrated” -negative “integrated”

该命令设置RTL代码中,无论你的寄存器是上升沿触发还是下降沿触发,控制该寄存器的时钟单元都是使用集成门控时钟单元。

set_clock_gating_style -minimum_bitwidth 4

上述命令意味着一个门控时钟至少要触发4个寄存器(这是由于引入ICG不可避免的会引入额外的面积,因此需要关注门控时钟至少需要gating寄存器的个数)

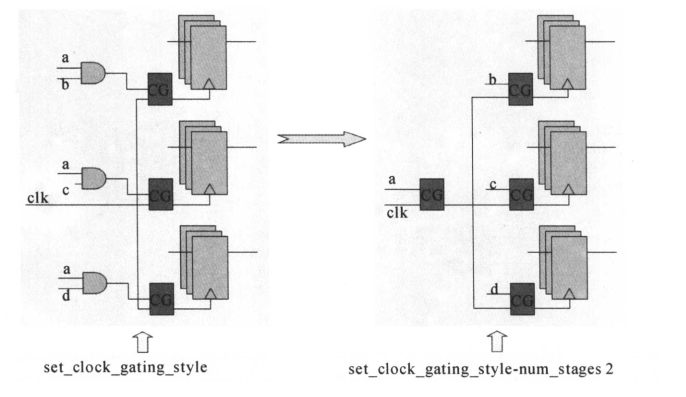

-num_stages选项用于设置一个多级门控的级数,在有些设计中,顶层的门控信号会分解成不同的子门控信号。在缺省情况下 为1,仅对跟寄存器阵列相连的门控制信号生成门控逻辑

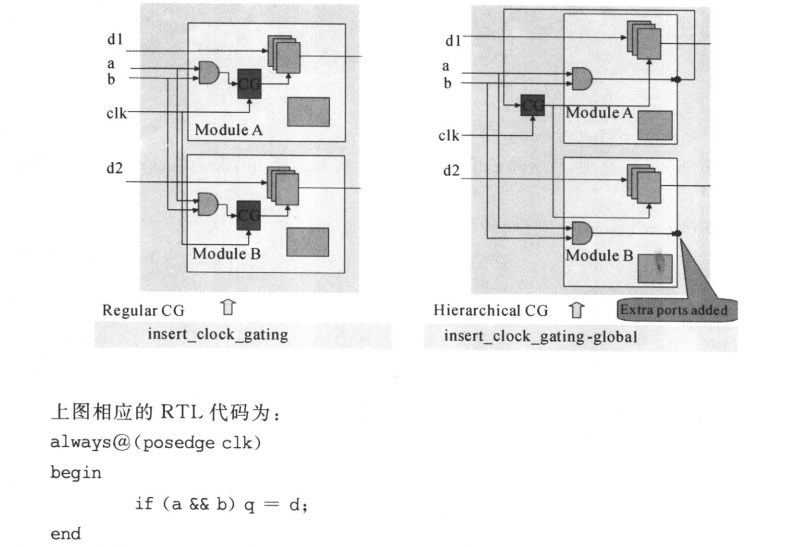

-galbal选项可以使得门控时钟穿越层次结构,如下图所示:

-control_point与-control_signal选项跟DFT有关,用于设置该门控单元在DFT时是否可控,DFT控制信号是scan-enable还是test-mode,以及DFT控制信号与EN信号的组合逻辑是放在门逻辑中的锁存器之前还是之后

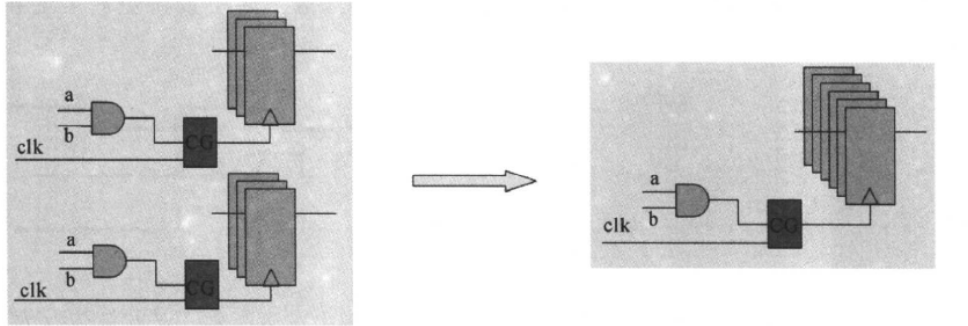

合并的命令为"merge_clock_gating_cells",如果两个或以上的门控时钟单元的输人逻辑相等,它们可以被合并。合并只能在一个层次内部进行。合并后,冗余的逻辑被删除。如下图所示:

有时候,我们需要删除某些门控时钟,这个时候我可以使用remove_clock_gating命令.

该部分参见《专用集成电路设计使用教程》9.3.1

举一个例子,例子来源于庄老师PPT,MPEG-4编码器中,90%的寄存器被门控时钟控制,70%的功耗降低都归功于门控时钟,使得其总功耗从30.6mW降到了8.5mW,近似为之前功耗的1/3

至此,门控时钟的概述,编码推荐与物理实现部分均已经介绍,后面就是物理实施的低功耗技术。

物理实施的低功耗技术

本节主要介绍物理实施,或者是数字后端阶段进行的低功耗技术:操作数分离(一般由工具来做,手工做若是有时序问题,将很难处理)、门级电路的功耗优化、多电压供电、电源门控(Power Gating)。

操作数分离(Operand Isolate)

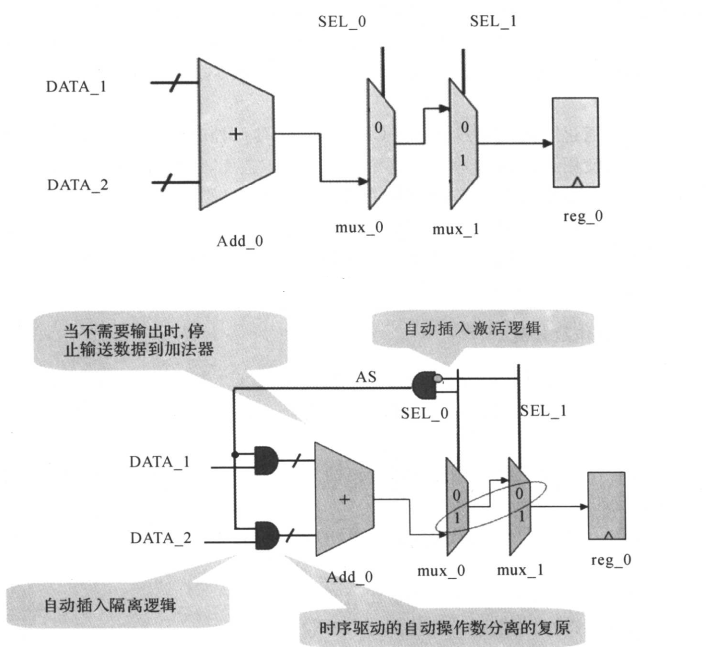

操作数隔离(简称OI)的核心思路是在不需要计算的时候,使用使能控制信号将输入数置于某一个固定值,使之不再进行计算,从而降低动态功耗~实现方式可以使用RTL编码的实行或者是指导综合工具(新思的Power Compiler)来执行。这里我们更多的关注基本的原理,就像CDC问题一样,对于工具的使用其实也是根据这些基本原理作为其原则来工作的,工具的使用可以关注UG,有需要的可以进行学习。先看下面的图示

上图当SEL_0不等于1、SEL_1不等于0的时候,加法器Add_0的结果不需要送到寄存器的输入。为了节省功耗,我们将通过改变电路的方式来控制当不需要加法输入的时候,停止送数据到加法器的输入。

我们可以看到这种方式带来的问题很明显的有面积的增大,时序变得更差。功耗再一定程度上有所改善。需要结合设计需求进行选择。同时可以在编码的时候进行相关操作,但是引入的问题是在时序过紧的时候,过多的OI可能会导致时序问题,过少的OI又很难有一个明显的功耗优化~算是有些难以理解的,当然一般还是根据需求,设计人员自行决定是否需要加做OI。使用工具加OI的好处是可以根据时序,时序不紧的路径添加,紧的路径不添加,来实现一个时序(性能),面积,功耗的折中PPA。

门级电路的功耗优化(Gate Level Power Optimization,简称GLPO)

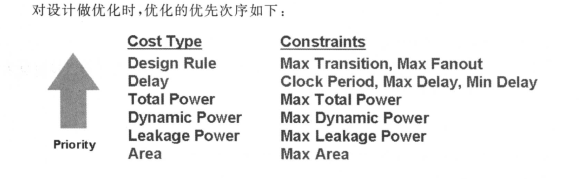

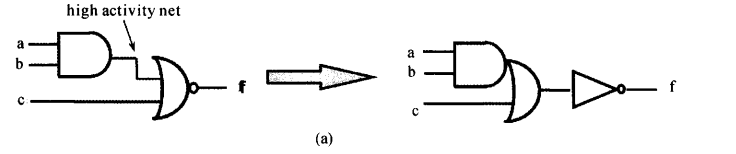

门级优化是从已经映射的门级网表开始,对设计进行功耗优化以满足功耗的约束,同时保证设计性能,满足设计规则与时序。门级电路的功耗优化包括了设计总功耗,动态功耗以及漏电功耗的优化。在进行优化时,优化的优先次序如下图所示。

优化的相关原则如下图所示

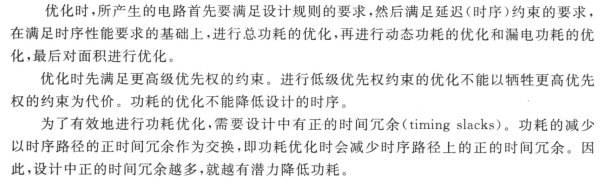

阈值电压和漏电功耗(静态功耗)有如下关系

我们可以利用多阈值电压工艺库的特点进行漏电的功耗优化,设计静态功耗低,性能高的电路。一般可以将关键路径选择延时较短的,将非关键路径选择延时长的路径(漏电较小)。

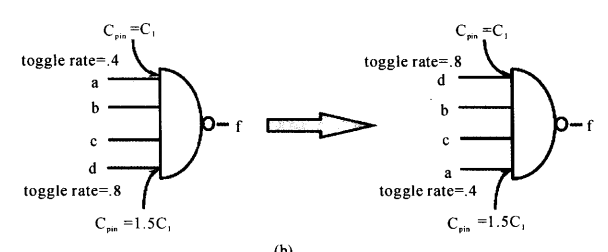

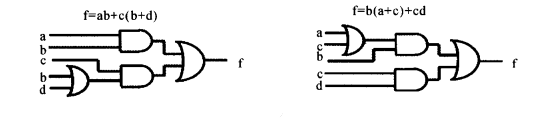

对于动态功耗的优化有如下方式:

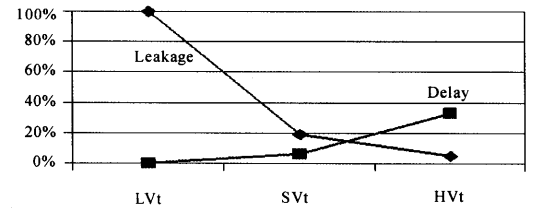

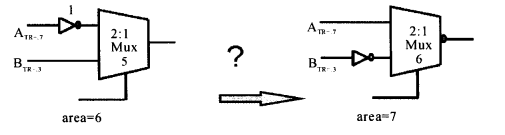

- 修改单元的驱动能力

- 技术映射:把高翻转率的连线放入单元内,减小开关功耗

- 交换引脚:把高翻转的连线接到电容值小的引脚

- 相位分配(不太理解这里是做了什么)

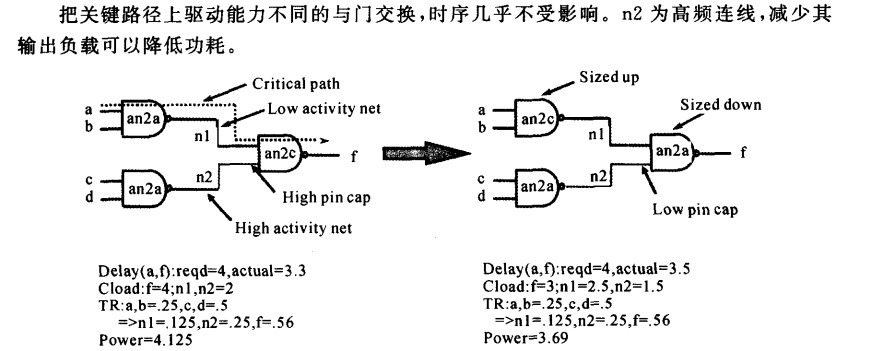

- 因式分解:其中b是高翻转率的信号

- 插入缓冲器

插入缓冲器后,减少了与非门的负载,并使寄存器的输入转换时间变小。

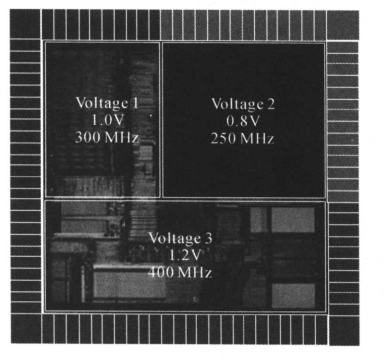

多电压供电

降低供电电压是降低芯片功耗最直接的方式,如下图所示,根据不同的频率要求、单元延时与供电电压成反比关系,对于低频可以使用较低的电压,从而满足时序与低功耗的设计要求。

多电压设计的风格有三种

- 各电压区域有固定的单一电压

- 各电压区域有多个固定电压,软件进行控制

- 采用自适应方式,可以使用软件进行控制

采用多电压技术需要在不同的电压之间进行信号的传递,需要使用电平转换器,将高低电压区域的信号传递到目标电压区域。

电源门控(Power Gating)

电源门控值得是芯片中某个区域的供电电源被关掉,即该区域内的逻辑电路的供电电源断开。

其他

data_gating

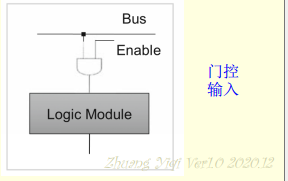

门控输入:暂时切断模块的输入,避免待机时因输入变化而导致的动态功耗,适用于无寄存器的组合逻辑模块,如共享总线

至此,低功耗相关专栏至此结束,回顾来看,制造工艺在其中有着很大的影响。另外的就是需要设计人员,后端人员需要继续努力的,通过相关的技术来优化功耗。

最后

以上就是单纯云朵最近收集整理的关于数字IC设计之——低功耗设计概述CMOS IC功耗分析低功耗方案其他的全部内容,更多相关数字IC设计之——低功耗设计概述CMOS内容请搜索靠谱客的其他文章。

发表评论 取消回复