并串 转换

题目描述

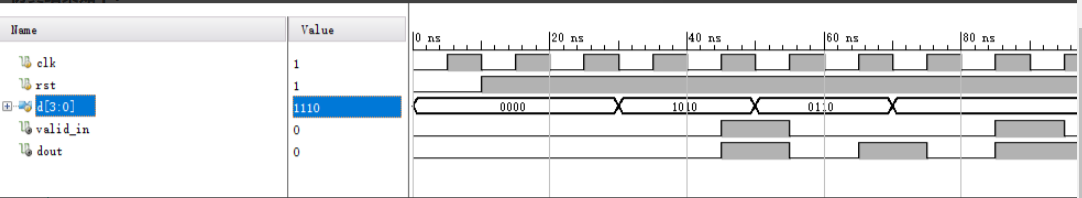

设计一个模块进行并串转换,要求每四位d输为转到一位dout输出,输出valid_in表示此时的输入有效

输入描述:

clk为时钟

rst为低电平复位

d 信号输入

输出描述:

dout 信号输出

valid_in 表示输入有效

题目解读

串并转换操作是非常灵活的操作,核心思想就是移位。

串转并就是把1位的输入放到N位reg的最低位,然后N位reg左移一位,在把1位输入放到左移后的reg的最低位,这样循环,就可以得到,以最高位开始传输,最低位传输完成的N位数据了;

并转串就是把并行的N位数据的最高位给1位输出,然后类似的循环左移就可以了。

`timescale 1ns/1ns

module huawei5(

input wire clk ,

input wire rst ,

input wire [3:0]d ,

output wire valid_in ,

output wire dout

);

//*************code***********//

reg [3:0] data = 'd0;

reg [1:0]cnt;//计数

reg valid;

assign dout = data[3];//data的最高位接输出线

assign valid_in =valid;

always @(posedge clk or negedge rst) begin

if(!rst)begin

data<= 'd0最后

以上就是天真小鸽子最近收集整理的关于并串 转换的全部内容,更多相关并串内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复