**

- 1.

Link for ModelSim介绍

**

Link for ModelSim®是一个把MATLAB/Simulink和针对FPGA 和ASIC的硬件设计流程无缝连结起来的联合仿真的接口扩展模块。它提供一个快速的双向连接将MATLAB/Simulink和硬件描述语言仿真器Modelsim连接起来。使二者之间直接的联合仿真成为可能,并且让你更高效的在MATLAB/Simulink中验证ModelSim中的寄存器传输级(RTL)模型。

传统的Simulink系统级设计和其仿真环境支持M语言,C/C++,以及Simulink模块。而通过添加硬件描述语言(HDL)到MATLAB/Simulink中,扩展了MATLAB/Simulink的并行运行能力,直接性,以及混合语言编程的能力。这使得Link for ModelSim模块缩小了算法和系统设计同硬件实现之间的巨大鸿沟。

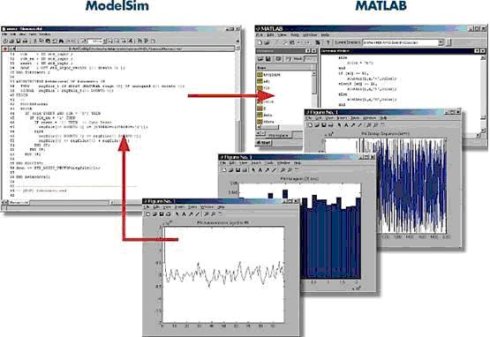

MATLAB 和 ModelSim 经过一个快速的双向的联合仿真接口联系起来,完成二者之间的数据交互特点

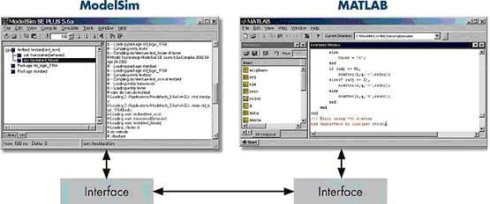

连接ModelSim到MATLAB和Simulink上是双向的,可进行联合仿真,验证,可视化。

支持ModelSim的PE和SE版本。

支持MATLAB/Simulink和ModelSim之间的用户可选通信模式。

提供共享存储器获得更快的系统性能,同时提供TCP/IP套接字加强多样性。

提供联合仿真的Simulink模块的库文件。

可以把输出测试结果转成VCD(value change dump)文件格式。

支持多个并行的ModelSim实例以及支持在Simulink和MATLAB函数中的多个硬件描述实体。

提供在MATLAB环境下与硬件描述语言交互式或批处理模式来进行联合仿真、调试、测试、以及验证工作。

使用Link for ModelSim

Link for ModelSim使用客户端/服务器结构来提供MATLAB/Simulink和ModelSim之间的接口。可以在一个单独的MATLAB环境或Simulink模型下提供与多个HDL实体和ModelSim的接口。

典型应用

使用 Link for ModelSim ,你可以建立一个有效的环境来进行联合仿真、器件建模、以及分析和可视化。进行如下的实例的开发。

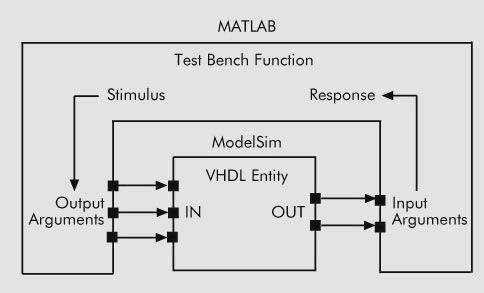

1 :可以在 MATLAB 或 Simulink 中针对 HDL 实体开发软件测试基准 (test bench) 。

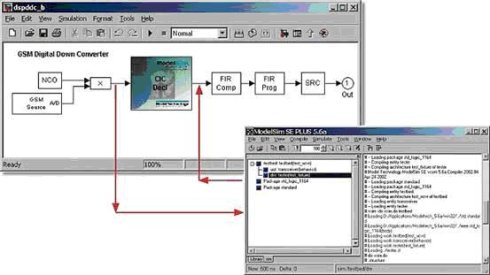

2 :可以在 Simulink 中对包含在大规模系统模型的 HDL 模型进行开发和仿真。

3 :可以生成测试向量进行测试、调试,以及同 MATLAB/Simulink 下的规范原形进行 HDL 代码的验证。

4 :提供在 MATLAB/Simulink 下的对 HDL 行为级的建模能力。

5 :可以在 MATLAB/Simulink 下对 HDL 的实现进行验证、分析、可视化。

Link for ModelSim 中 MATLAB 与 ModelSim 接口和 Simulink 与 ModelSim 接口是独立的。这使得你可以单独使用一个接口或同时使用两个。

使用ModelSim和MATLAB的接口

使用 Link for ModelSim 后,你可以使用 MATLAB 和它提供的工具箱,比如设计和仿真信号处理,或者其他的数值计算算法。你还可以用 HDL 来取代算法和系统设计中的器件模型,并直接完成 HDL 器件和 MATLAB 中剩余算法的联合仿真。

使用ModelSim和Simulink的接口

你可以通过 Simulink 和相关的 Blockset 创建一个关于信号处理方面或者通信系统方面的系统级设计。你也可以把 HDL 器件合并到设计中或者用 HDL 模块来取代相应的子系统,并借此来创建软件测试基准来验证你的 HDL 实现。 ModelSim 中联合仿真模块的参数对话框可以让你很容易的设置输入输出端口,二者连接的属性,时钟,以及 TCL 命令。

本图显示了在 MATLAB 和 ModelSim 的接口关系。把在 MATLAB 中获得的测试基准代码输出作为输入输入到 VHDL 实体中,并把经过 ModelSim 的输出输入到 MATLAB 函数中

Link for ModelSim 还提供一个模块来生成 VCD 的文件格式,可以用来:

1 :观察在 HDL 仿真环境下的 Simulink 仿真波形

2 :使用相同或不同的仿真环境来比较多个不同仿真运行的结果。

3 :提供到后仿真分析工具的输入端口。

关于滤波器在部分设计实现应用的联合仿真和软件测试基准的实例。相当于 VHDL 代码在 ModelSim 中的执行过程

支持Verilog语言

Link for ModelSim 本身就提供对 VHDL 语言的联合仿真的支持。同时你还可以通过在 VHDL wrapper 中自动封装 Verilog 代码,使得其可以支持 Verilog 语言的联合仿真。于是 Verilog 代码相当于直接在 ModelSim 前端就执行完毕,而忽略其性能影响。 Verilog 代码和 MATLAB 的连接可以通过 VHDL wrapper 和 Link for ModelSim 来实现,这使得你可以使用 Verilog 硬件描述设计来完成和 MATLAB 之间联合仿真、软件测试基准、验证以及可视化。

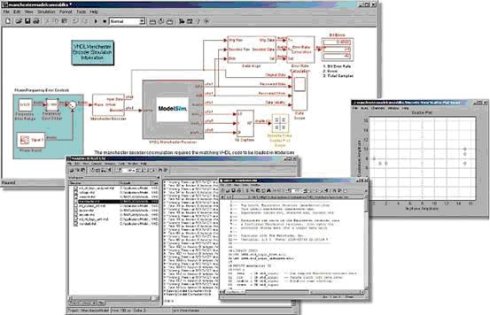

关于一个 Manchester 接收器的联合仿真和软件测试基准的实例。通过使用 Simulink , DSP Blockset 以及 Communicstions B lockset 来创建的一个系统。该接收机在 VHDL 中实现并在 ModelSim 中仿真。

Matlab与Modelsim设计流程:

- 在MATLAB中配置ModelSim:在命令窗中敲入configuremodelsim,根据提示一步一步进行即可。

- 创建一个目录用来准备存放ModelSim工程文件(路径最好遵循上面的经验),可以在MATLAB的命令窗中用如下命令完成:cd、mkdir

- 拷贝如下文件到3准备的文件夹中:

MATLABROOTtoolboxmodelsimmodelsimdemosmodsimrand_plot.m

MATLABROOTtoolboxmodelsimmodelsimdemosVHDLmodsimrandmodsimrand.vhd

可如下完成:在MATLAB中采用cd将当前路径转到目标文件夹,用pwd命令查看确保;然后用

copyfile([matlabroot,‘toolboxmodelsimmodelsimdemosmodsimrand_plot.m’])

和

copyfile([matlabroot,‘toolboxmodelsimmodelsimdemosVHDLmodsimrandmodsimrand.vhd’])实现。 - 在MATLAB命令窗中采用如下语句打开MATLAB的ModelSim服务器,为建立链接做好准备:

hdldaemon (采用的是share memory的方式,也可以采用socket方式,参见help hdldaemon)可以用 hdldaemon(‘status’) 查看服务器状态;用 hdldaemon(‘kill’) 关闭服务器 - 在MATLAB的cmd中采用 vsim打开ModelSim,可见ModelSim自动转到MATLAB当前目录。在ModelSim的命令窗口中采用vlib work创建work库永远接受工作工程编译结果;在ModelSim的cmd中用 vmap work work进行设计库和当前工作库映射

- 在ModelSim的cmd中用edit modsimrand.vhd在editor中打开vhdl文件,进行vhdl文件编写设计修改

- 在ModelSim的cmd中用vcom modsimrand.vhd编译modsimrand.vhd

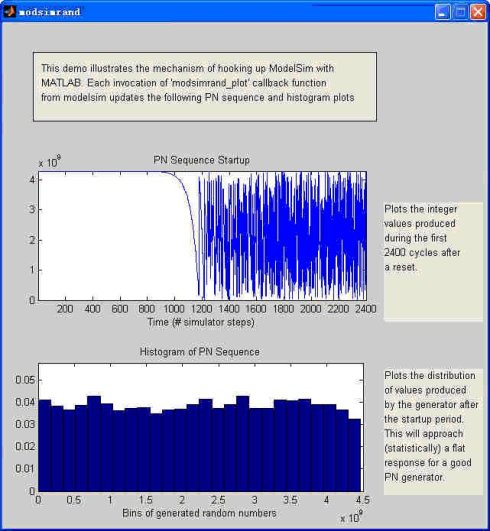

在ModelSim的cmd中用 vsimmatlab work.modsimrand 将modsimrand导入仿真器在ModelSim的cmd中用 matlabtb modsimrand -mfunc modsimrand_plot -rising /modsimrand/clk -socket portnum初始化真器(这里的各个参数的意义可以查阅matlabtb这个函数的帮助信息)

用 force sim:/modsimrand/clk 0 0,1 5 ns -repeat 10 ns

force sim:/modsimrand/clk_en 1

force sim:/modsimrand/reset 1 0,0 50 ns

进行仿真输入信号设置,具体含义请查阅modelSim的用户手册,当然这些信号(实际就是实体的in pin,可以从MATLAB的中获取,这是以后慢慢再学) - 在ModelSim的cmd中用 run 80000

于是乎便得到了如下的根据ModelSim中仿真返回的结果绘制的图像如下:

Simulink与Modelsim设计流程

1.建立HDL模型。

2. ModelSim> vlib work;ModelSim> vmap work work。

3. ModelSim> vcom XXXXXX.vhd。

5. vsim(‘socketsimulink’, 4449)。

6. ModelSim> vsimulink work.XXXXXX。

7.开始仿真。

在Matlab与Modelsim联调用到的命令

Malab的命令:

configuremodelsim:对Modelsim的安装路径进行配置。

hdldaemon:hdldaemon (默认采用的是share memory的方式,也可以采用socket方式,参见help hdldaemon)可以用 hdldaemon(‘status’) 查看服务器状态;用 hdldaemon(‘kill’) 关闭服务器。

mvl2dec:将比特逻辑值转化成为十进制数。

vsim:从matlab调用Modelsim。

Modelsim的命令:

matlabcp:将Matlab函数与Modelsim中的VHDL的entity或者Verilog的module建立联系。例如:vsim> matlabcp u_osc_filter -mfunc oscfilter将Modelsim中的entity:u_osc_filter与Matlab中的函数oscfilter建立关系。其中-mfunc的作用是将不同名的实体或者函数建立关系,若是没有-mfunc则函数与实体的名要一样。

matlabtb:初始化与VHDL的entity或者Verilog的module相关联的Matlab测试平台。例如:matlabtb modsimrand -mfunc modsimrand_plot -rising /modsimrand/clk。

matlabtbeval:调用代表VHDL的entity或Verilog的module的Matlab函数。

nomatlabtb:终止matlab中测试平台的调用。

vsimmatlab:将VHDL的entity和Verilog的module导入仿真器。例如:vsimmatlab work.modsimrand将modsimrand导入仿真器

vsimulink:导入VHDL的entity或Verilog的module与Simulink联系起来。

wrapverilog:使用VHDL封装Verilog的module。在执行Verilog封装之前必须在Modelsim中编译装载,如下例所示:

vlib work

vmap work work

vlog myverilogmod.v

vsim myverilogmod

wrapverilog -nocompile myverilogmod

其中-nocompile禁止自动编译。封装的结果输出到myverilogmod_wrap.vhd里。

vlib work: vlib work创建work库永远接受工作工程编译结果。

vmap work work:进行设计库和当前工作库映射。

edit XXXX.vhd:在editor中打开vhdl文件,进行vhdl文件编写设计修改。

vcom XXXX.vhd:编译XXXX.vhd。

force:进行仿真输入信号设置,例如:

force sim:/modsimrand/clk 0 0,1 5 ns -repeat 10 ns

force sim:/modsimrand/clk_en 1

force sim:/modsimrand/reset 1 0,0 50 ns

run:仿真开始,例如:run 80000

matlab 与 modelsim联合仿真流程

1、安装所需软件,建议完全安装matlab7.01及以上版本,modelsim6.0及以上版本。另外matlab7.0不能在AMD机器上正常运行,需要安装matlab7.01及以上版本。从matlab R2006a以后,即Link for Modelsim 2.0以后才能完全支持verilog的联合仿真,之前仅支持VHDL,如需支持verilog,则需用modelsim命令wrapverilog进行VHDL打包,不幸的是我没有在modelsim 6.0e中找到该命令。另外建议所有软件安装在默认路径下面。

2、利用matlab命令configuremodelsim配置modelsim,其实就是建立一种连接关系。在matlab命令行中输入:

configuremodelsim //“>>“ 表示matlab命令行提示符:

%matlab7.01 中setupmodelsim 对应于该命令。

出现如下提示:

Identify the ModelSim installation to be configured for MATLAB and Simulink

Do you want setupmodelsim to locate installed ModelSim executables [y]/n?”

%输入y并回车

Select a ModelSim installation:

[1] C:Program FilesModeltech_6.0win32 ModelSim SE 6.0

[0] None

Selected Modelsim installation:”

%如果modelsim的路径是正确的,输入1

Modelsim successfully configured for MATLAB and Simulink”

Configuration has finished.

3、通常此时matlab服务器(matlab server)已经启动。可以通过在matlab命令行输入:

hdldaemon(‘status’)

进行检测,如果正常运行,则显示:

HDLDaemon shared memory server is running with 0 connections

如果没有启动,则显示:

HDLDaemon is NOT running

此时,可在matlab命令行中输入:

hdldaemon

4、通过在matlab命令行输入:

vsim

启动modelsim

5、在modelsim命令行下利用”cd”命令切换到工作目录下,通常是.v文件的存储目录下(通常.v和.m的文件名相同),同时执行如下命令:

ModelSim>vlib work

ModelSim>vmap work work

ModelSim>vlog prj.v //编译.v文件

ModelSim>vsimmatlab prj //启动vsim与matlab的联合仿真

ModelSim>matlabtb prj -rising /prj/clk -mfunc prj_plot //初始化modelsim并且调用matlab进行验证。其中prj_plot是项目的.m文件名。

//如果.v和.m文件名一致,则可以省略-mfunc 参数

VSIM n>force /prj/clk 0 0ns, 1 5ns -repeat 10ns //设置clk信号

VSIM n>force /prj/reset 1 0ns, 0 50ns //设置reset信号

VSIM n>run 80000

//仿真结束后,在modelsim中选择simulate->End Simulation结束modelsim仿真,在matlab命令行输入”hdldaemon(‘kill’)“结束matlab服务器。

注意事项:

0、最好用force产生clk 及 reset信号!!!

1、如果采用force 产生外部时钟信号,各子模块最好去掉timescale定义,否则很可能无法正常运行; timescale的定义,需按要求在各个模块上面增加相应的

2、如果由于调用xilinx库文件,而且为了保持模块可移植性,从而不能改动Xilinx库中timescale定义,并且在matlabtb命令中增加-rising选项,如: timescale定义必须去掉,否则在matlab 2006a 调用modelsim时产生死循环。

matlabtb prj -rising /prj/clk -mfuc prjm

3、如果采用iport传递clk信号及其他信号,可采用tnext或者在matlabtb中采用-repeat选项,但各子模块的

即使采用-rising选项,死循环依然存在。

最后

以上就是香蕉哈密瓜最近收集整理的关于MATLAB 与Modelsim之间对测试系统的联合仿真的全部内容,更多相关MATLAB内容请搜索靠谱客的其他文章。

发表评论 取消回复