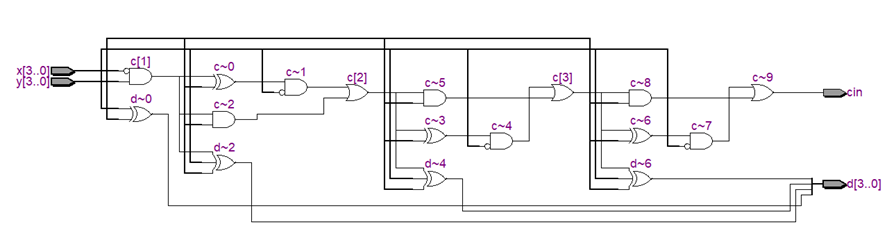

类似于行波进位加法器,用串联的方法也能够实现多位二进制数的减法操作。 比如下图是4位二进制减法逻辑电路图。

8位二进制减法的verilog代码如下:

module subn(x, y, d,cin); parameter n=8; input [n-1:0] x; input [n-1:0] y; output reg[n-1:0] d; //diff output reg cin; //borrow from high bit reg [n:0] c; integer k; always @(x,y) begin c[0] = 1'b0; for(k = 0; k < n; k = k + 1) begin d[k] = x[k]^y[k]^c[k]; c[k+1] = (~x[k]&(

最后

以上就是干净项链最近收集整理的关于Verilog 加法器和减法器(4)的全部内容,更多相关Verilog内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复